Method for manufacturing semiconductor device

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electric solid-state devices, etc., can solve problems such as wiring layer resistance changes, EPROM reliability degradation, etc., and achieve the effect of preventing changes or reliability degradation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

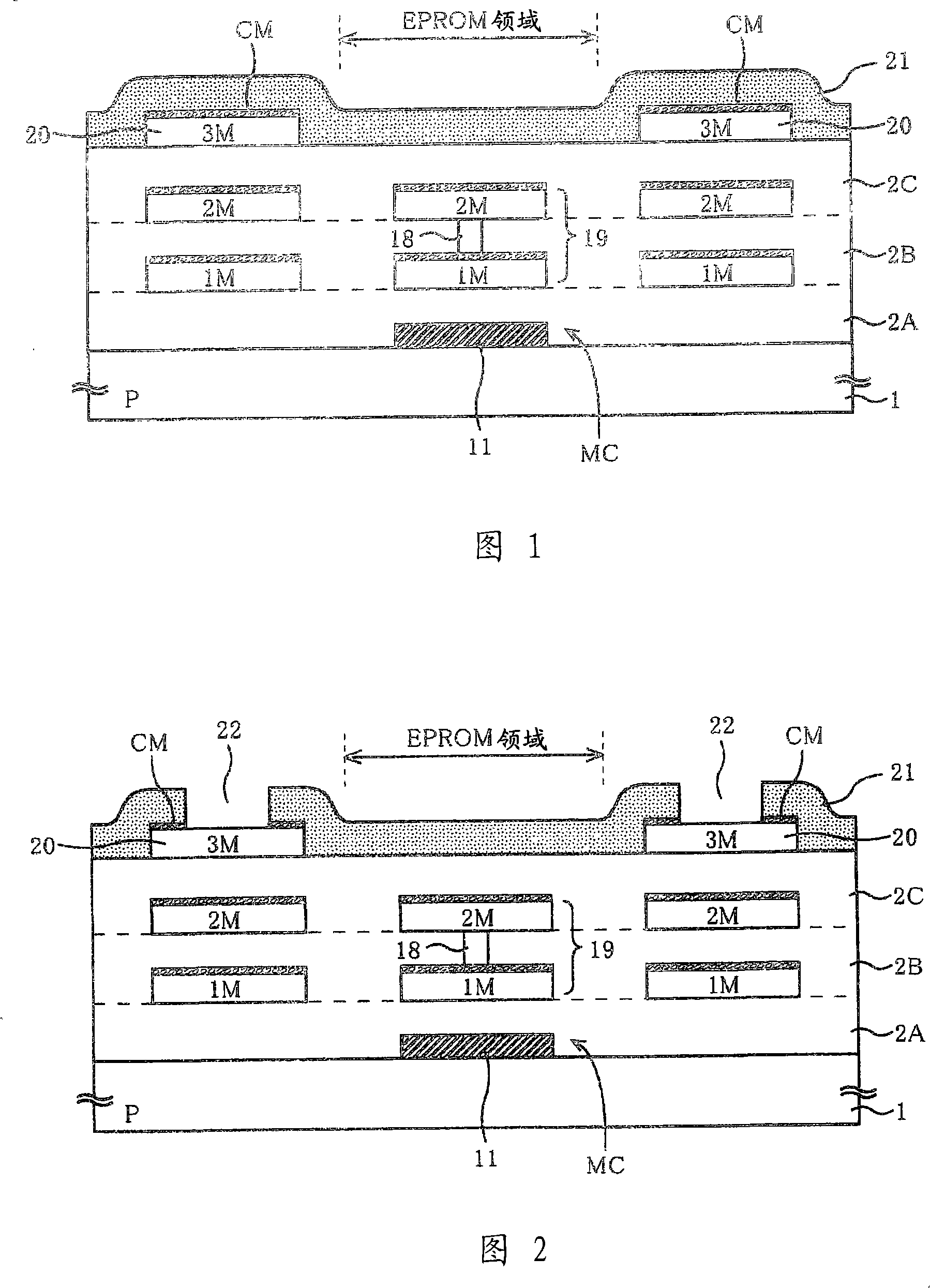

[0038] Next, a method of manufacturing a semiconductor device according to an embodiment of the present invention will be described with reference to the drawings.

[0039] As shown in FIG. 1 , memory cells MC are formed in the EPPOM region on the P-type semiconductor substrate 1 . Although there are actually a plurality of memory cells MC, FIG. 1 schematically shows only one floating gate 11 of the memory cell MC. This semiconductor device is formed by a three-layer metal process, a first metal layer 1M, a second metal layer 2M, and a third metal layer 3M on the floating gate 11 of the memory cell MC with interlayer insulating layers 2A, 2B, 2C formed. Interlayer insulating layers 2A, 2B, and 2C are formed of, for example, a laminated film of TEOS film / SOG film / TEOS film (film thickness about 950 nm), and are planarized. In addition, interlayer insulating layers 2A, 2B, and 2C have a property of transmitting ultraviolet rays.

[0040] The structure of the memory cell Mc wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More