Method for calibrating sub-nanometer critical dimension using pitch offset

A technology of key dimensions and calibration methods, applied in nanotechnology, components for opto-mechanical processing, measurement devices, etc., can solve the problems of damage to test wafers, poor calibration results, and high process costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

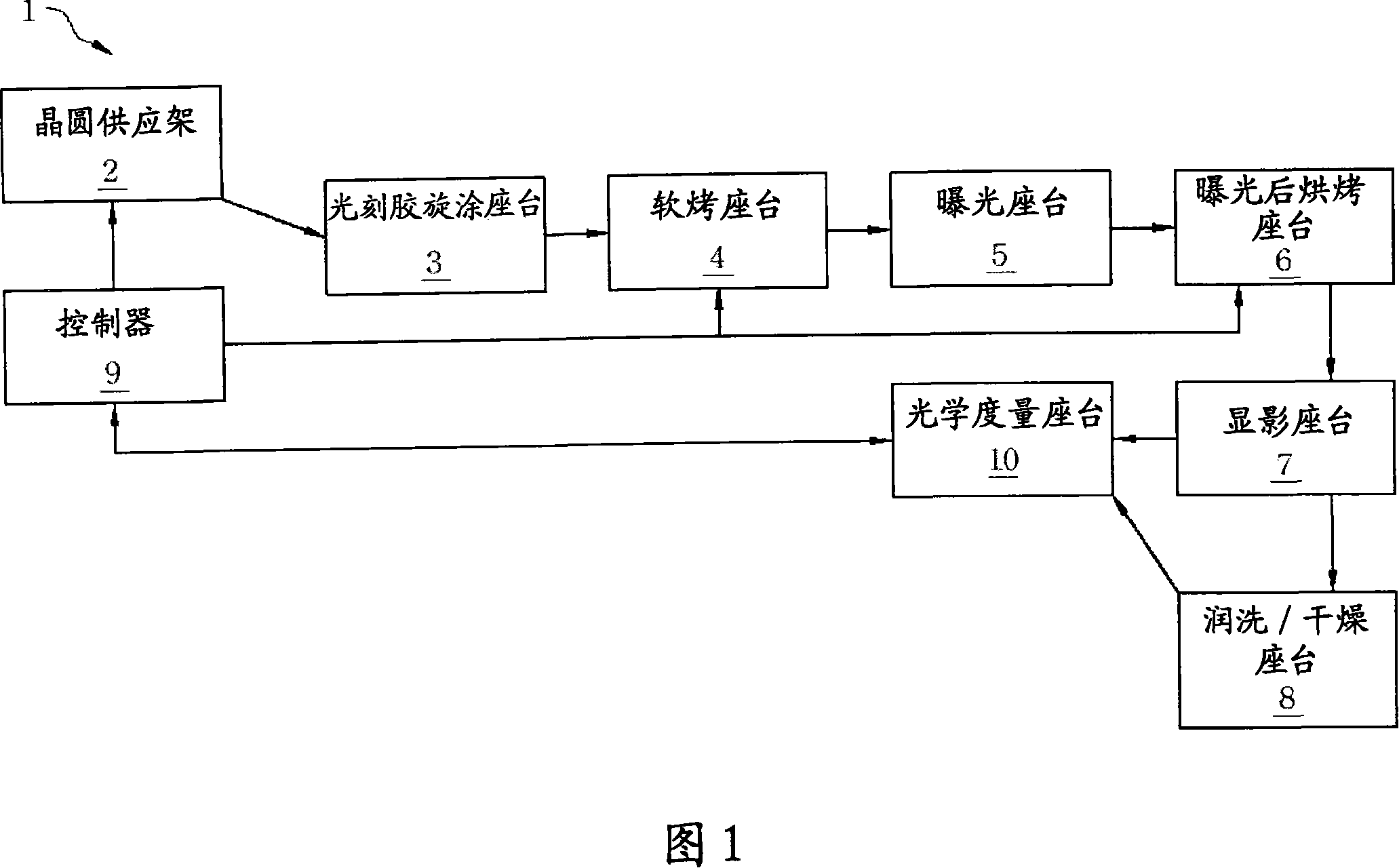

[0049] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, the method for calibrating sub-nanometer critical dimensions proposed according to the present invention will be implemented in conjunction with the accompanying drawings and preferred embodiments below. Ways, methods, steps, features and effects thereof are described in detail below. For convenience of description, in the following embodiments, the same elements are denoted by the same numbers.

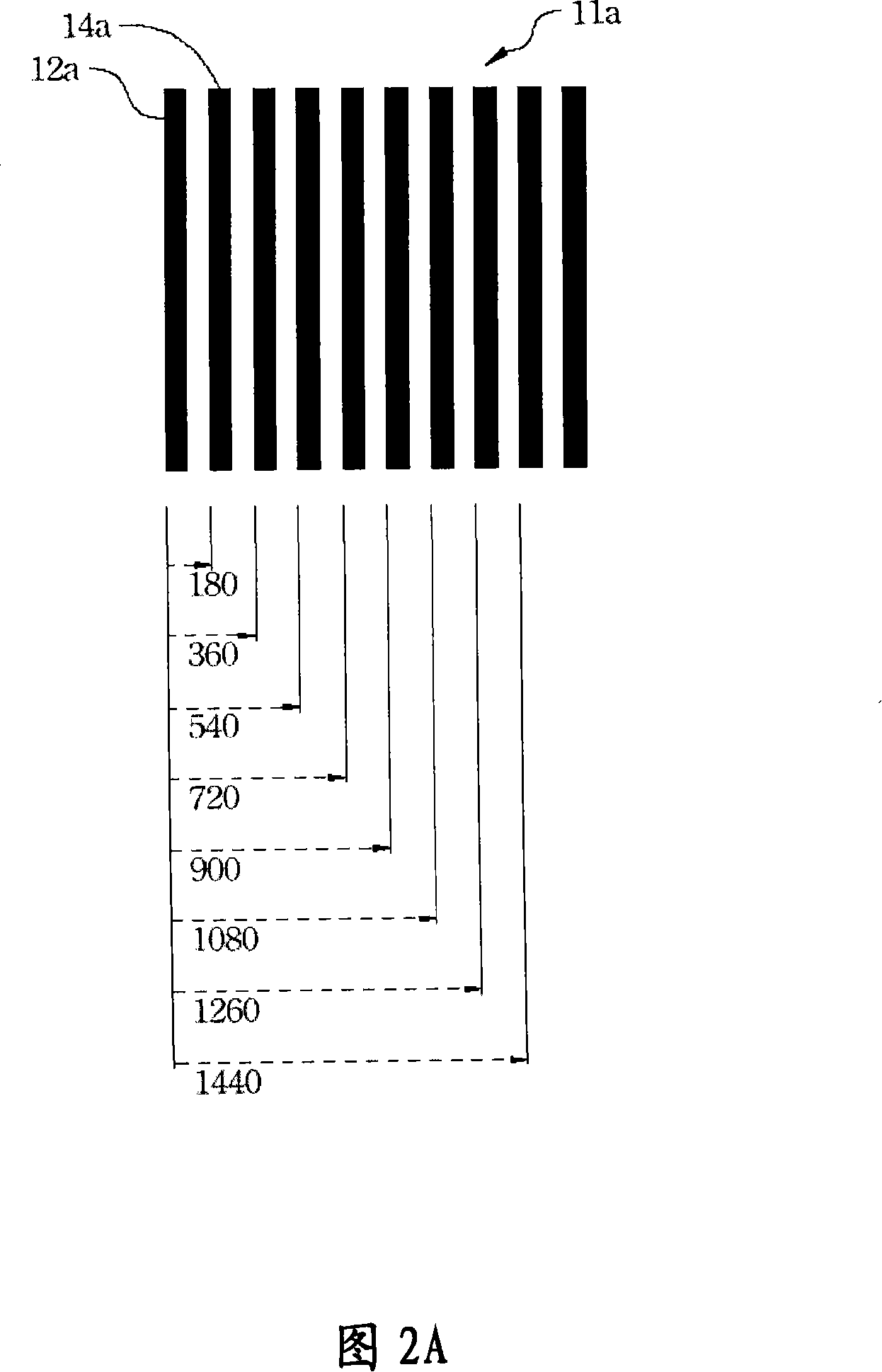

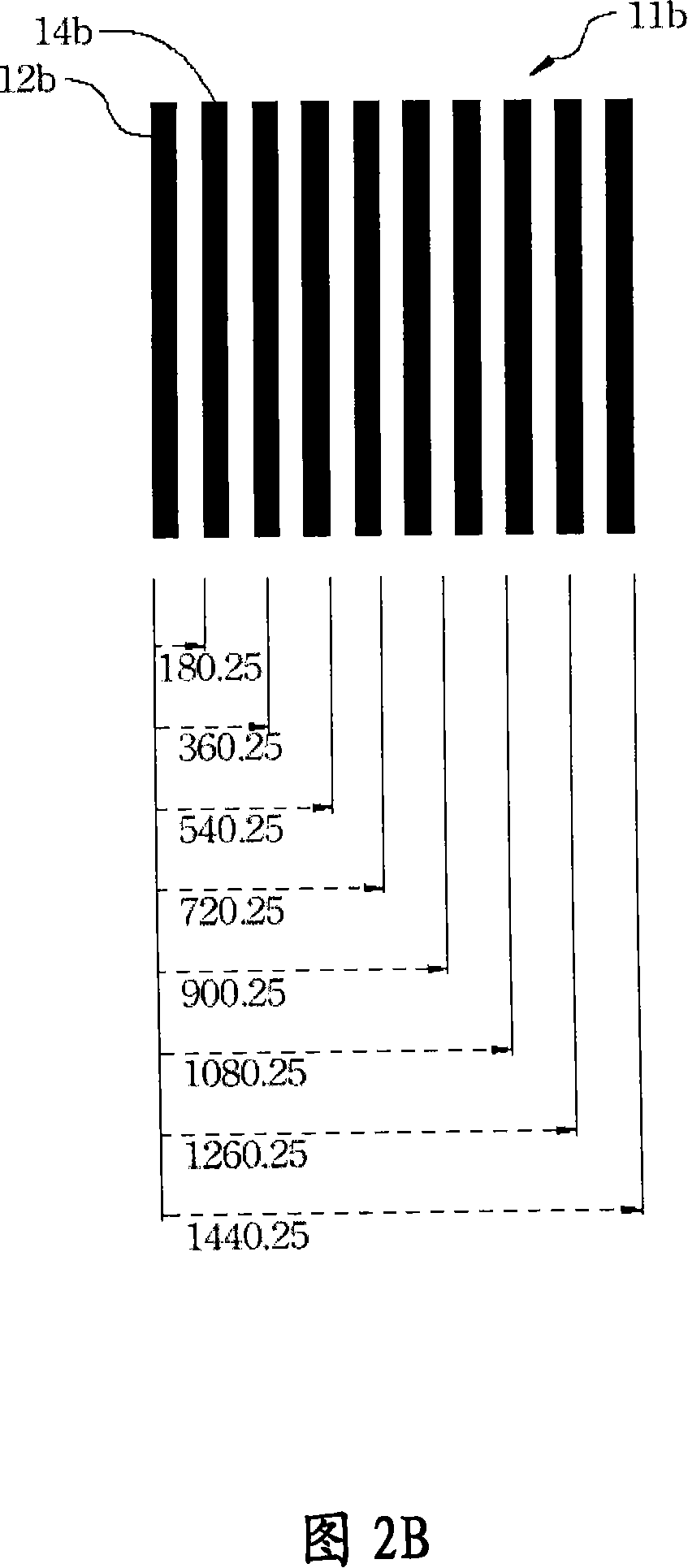

[0050] The present invention provides a method for calibrating a metrology tool or system. In an exemplary embodiment, a pattern layer is formed such that the formed shutter pattern has a known pitch plus an offset value, wherein the material of the pattern layer may include but not limited to photoresist, polysilicon, oxide, and the like. In an exemplary embodiment, the spacing value is less than 1 nanometer. The present invention facilitate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle of incidence | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More