A burr judgement and elimination circuit

A technology for eliminating circuit and burrs, which is applied in the field of microelectronics, can solve problems such as burr elimination errors, and achieve the effect of eliminating burrs and ensuring safe work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The following is based on Figure 7 to Figure 11 , a preferred embodiment of the present invention is given and described in detail, so that the functions and features of the present invention can be better understood.

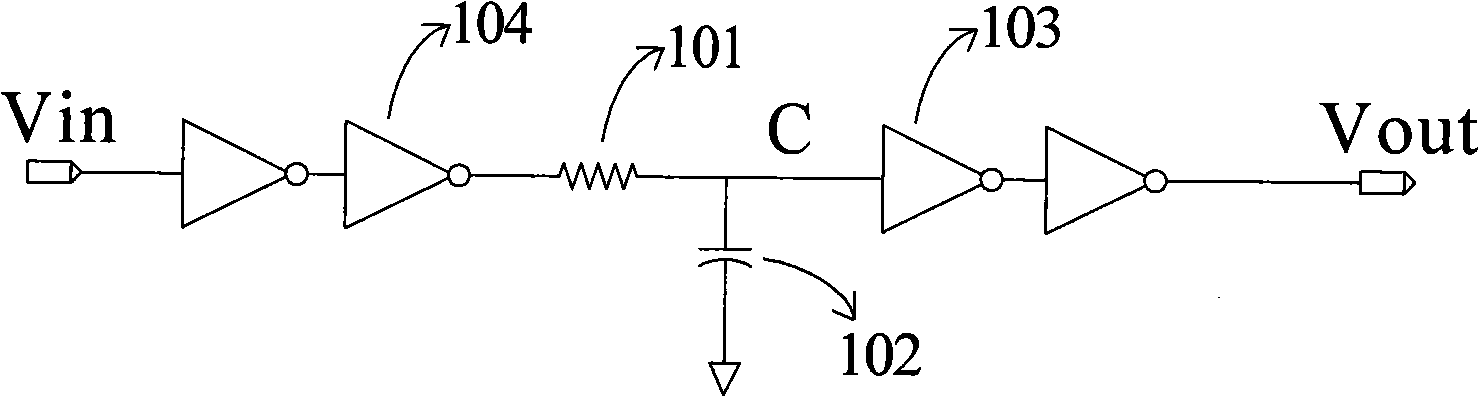

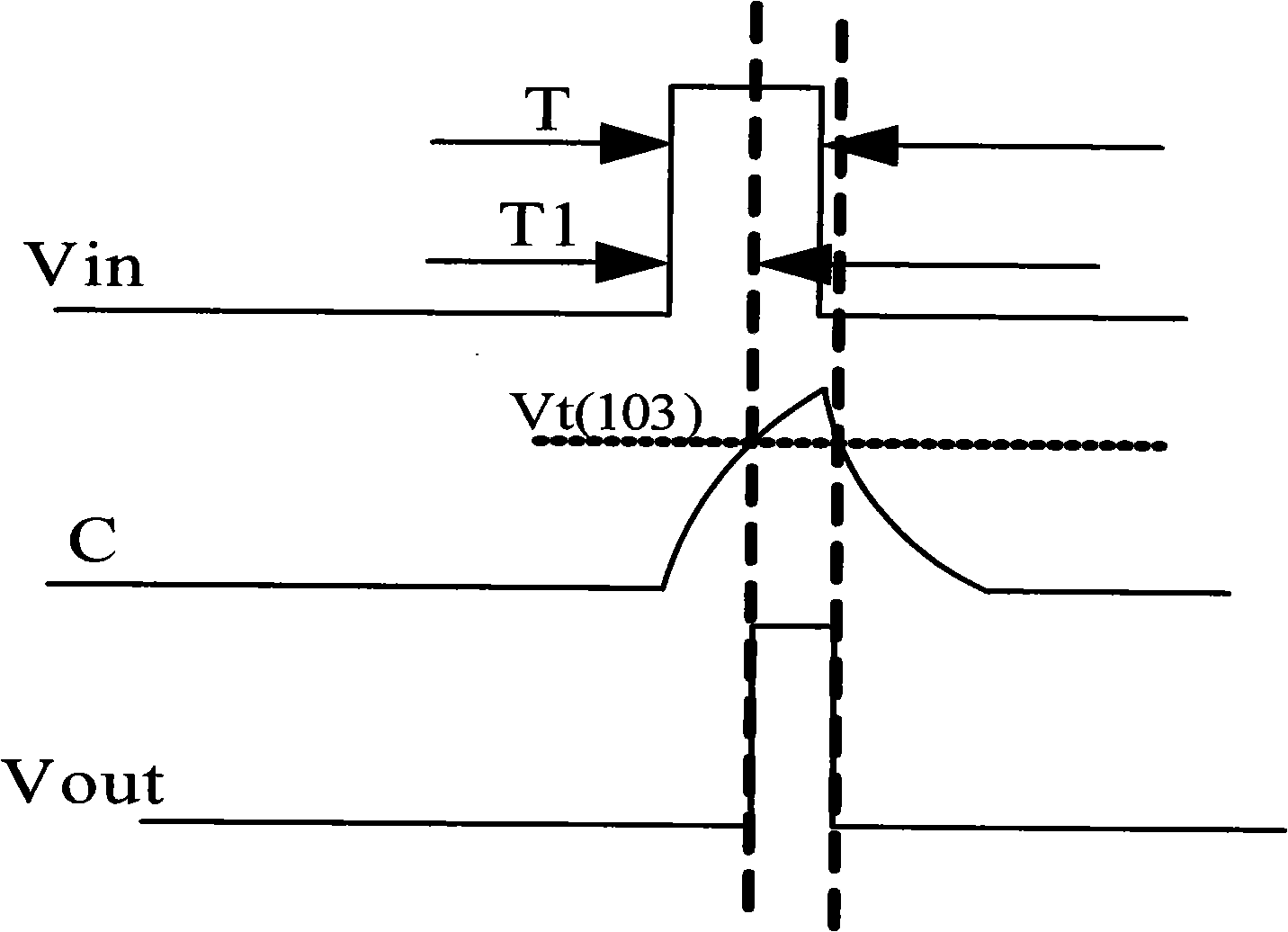

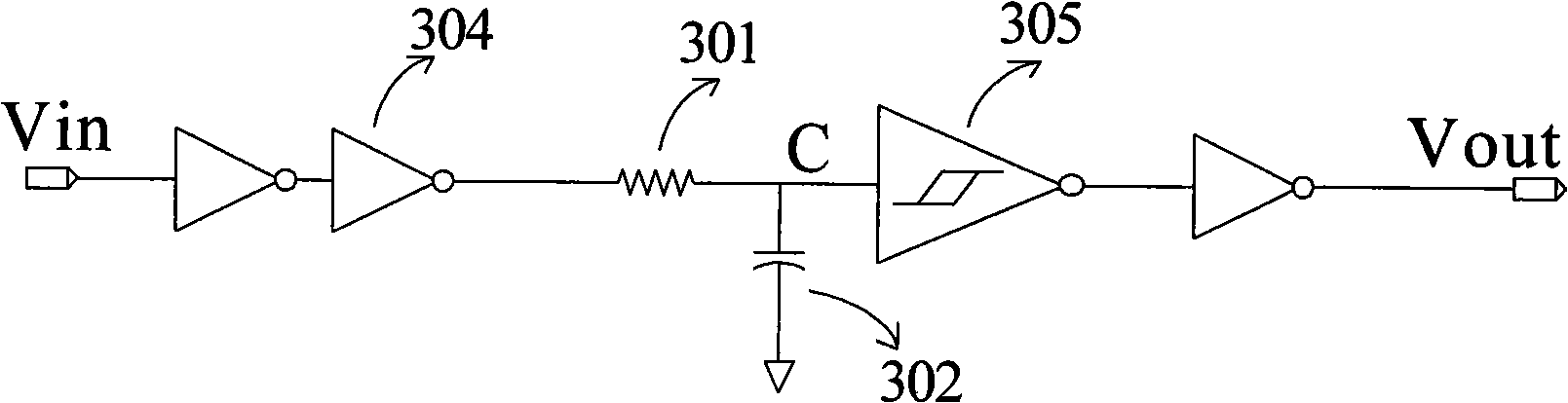

[0034] Figure 7 It is a structural block diagram of the burr judgment and elimination circuit of the present invention. Such as Figure 7 As shown, the glitch judging and eliminating circuit of the present invention includes an RC delay circuit for detecting the glitch width. A delay output circuit connected to the output of the RC delay circuit is used to eliminate glitches generated under specific conditions. The front end A and the back end B of the RC delay circuit are connected to a feedback circuit, and the output of the feedback circuit returns to the back end C of the RC delay circuit. The RC delay circuit controls the feedback circuit to perform an accelerated reset after detecting a glitch, and accelerates the setting through the feedback...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More