Dynamic simulation platform method for embedded processor function verification

An embedded processor and dynamic simulation technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of reduced efficiency of verification simulation process, low efficiency of manual writing one by one, and time-consuming functional verification platform. , to achieve the effects of strong reusability, shortened verification time, and convenient maintenance and modification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043]This embodiment is to apply the present invention to carry out functional verification for CKCore series embedded processors. CKCore series embedded processors are 32-bit high-performance embedded processors with independent intellectual property rights, which are jointly developed by Hangzhou Zhongtian Microsystems Co., Ltd. and Zhejiang University.

[0044] The basic idea of the specific implementation is:

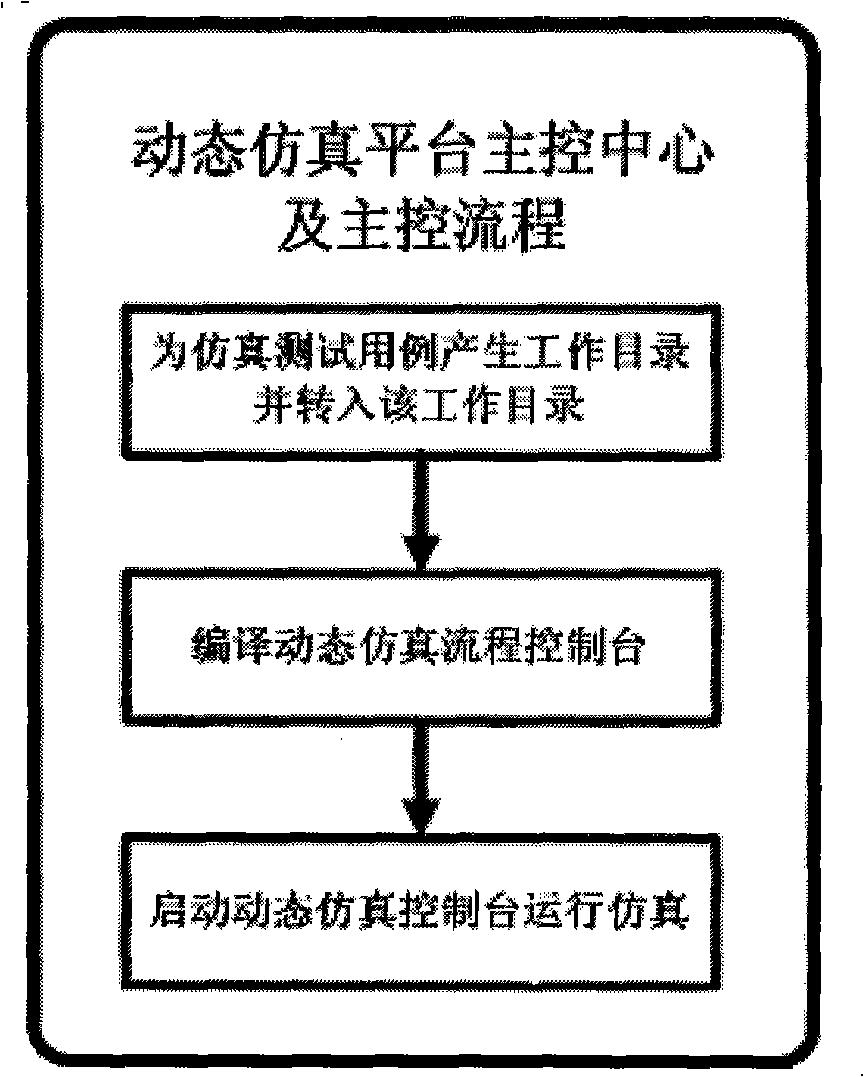

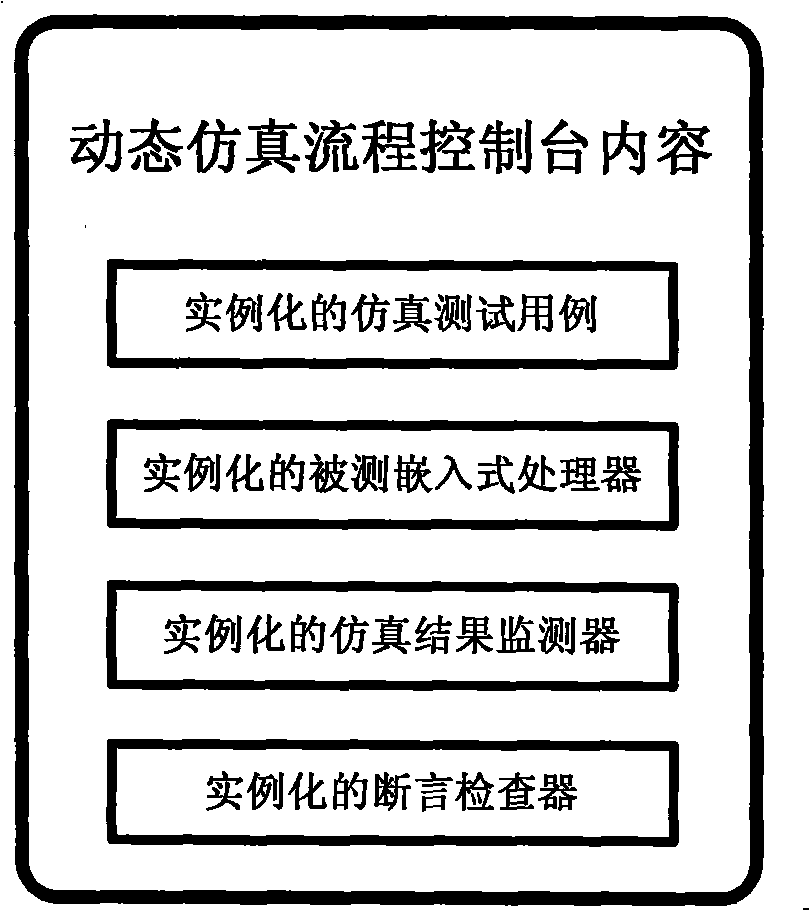

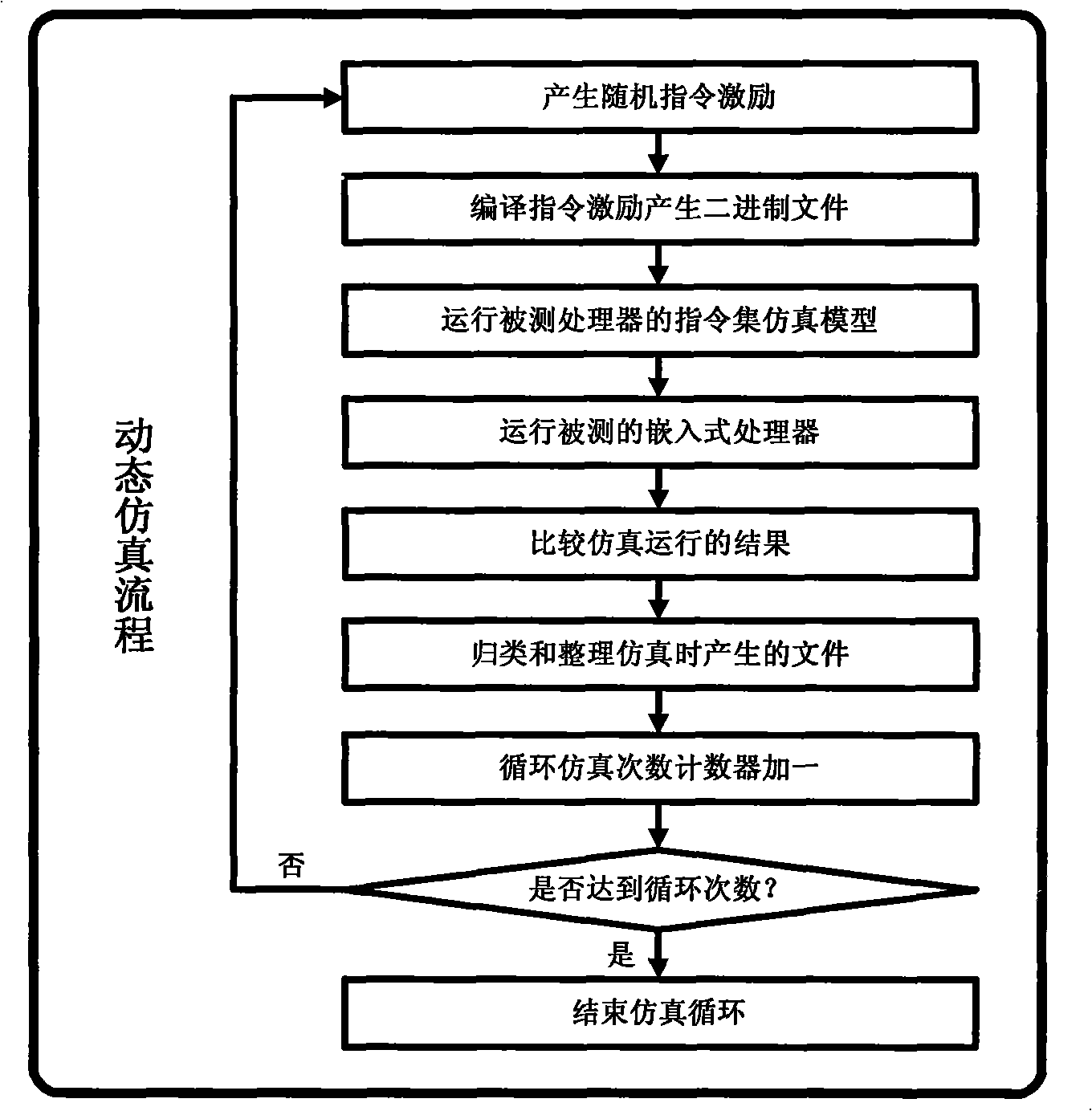

[0045] Establish a platform master control center and a simulation process console, the former is responsible for the establishment of the platform environment, the conversion of the working directory, the compilation of the verification platform and the start of the simulation; the latter is responsible for the control of the simulation process, including the generation of incentives, the embedding of the tested The operation of the model processor and its instruction set reference model, the comparison of simulation results, and the processing of simulation res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com