Ciphering unit being suitable for compacting instruction set processor

A technology of encryption unit and processor, applied in the direction of public key of secure communication, machine execution device, etc., can solve problems such as cost increase

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

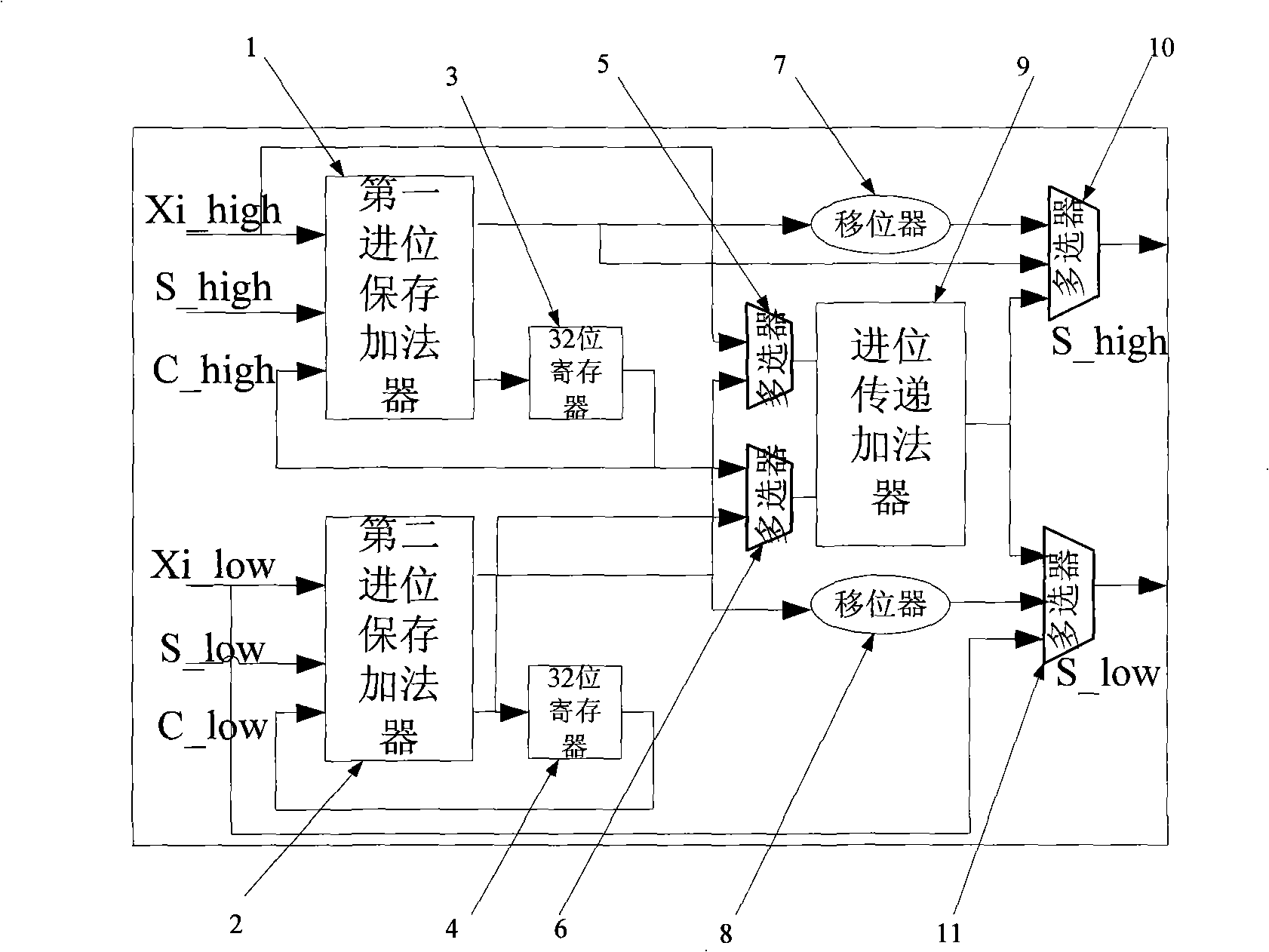

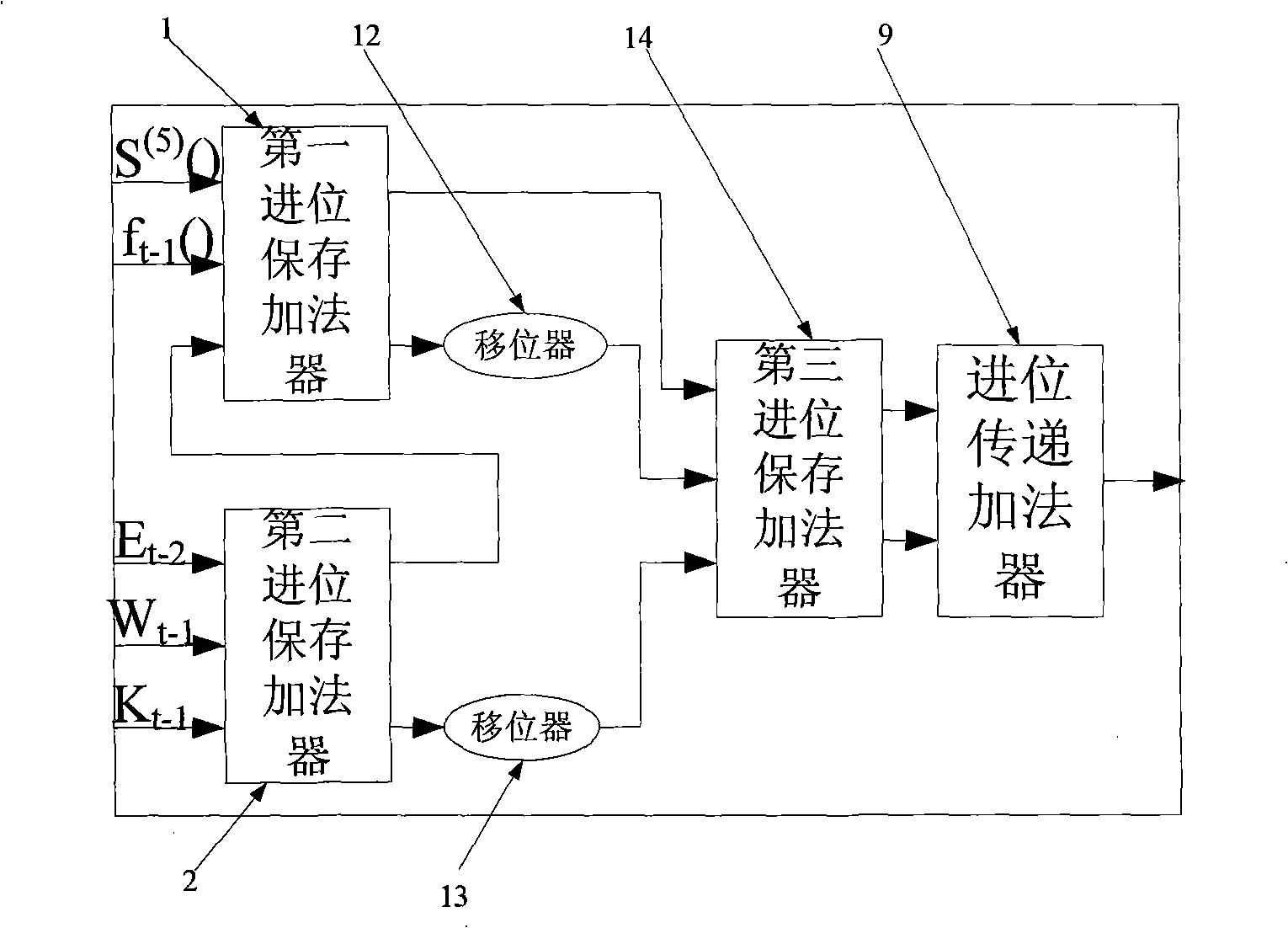

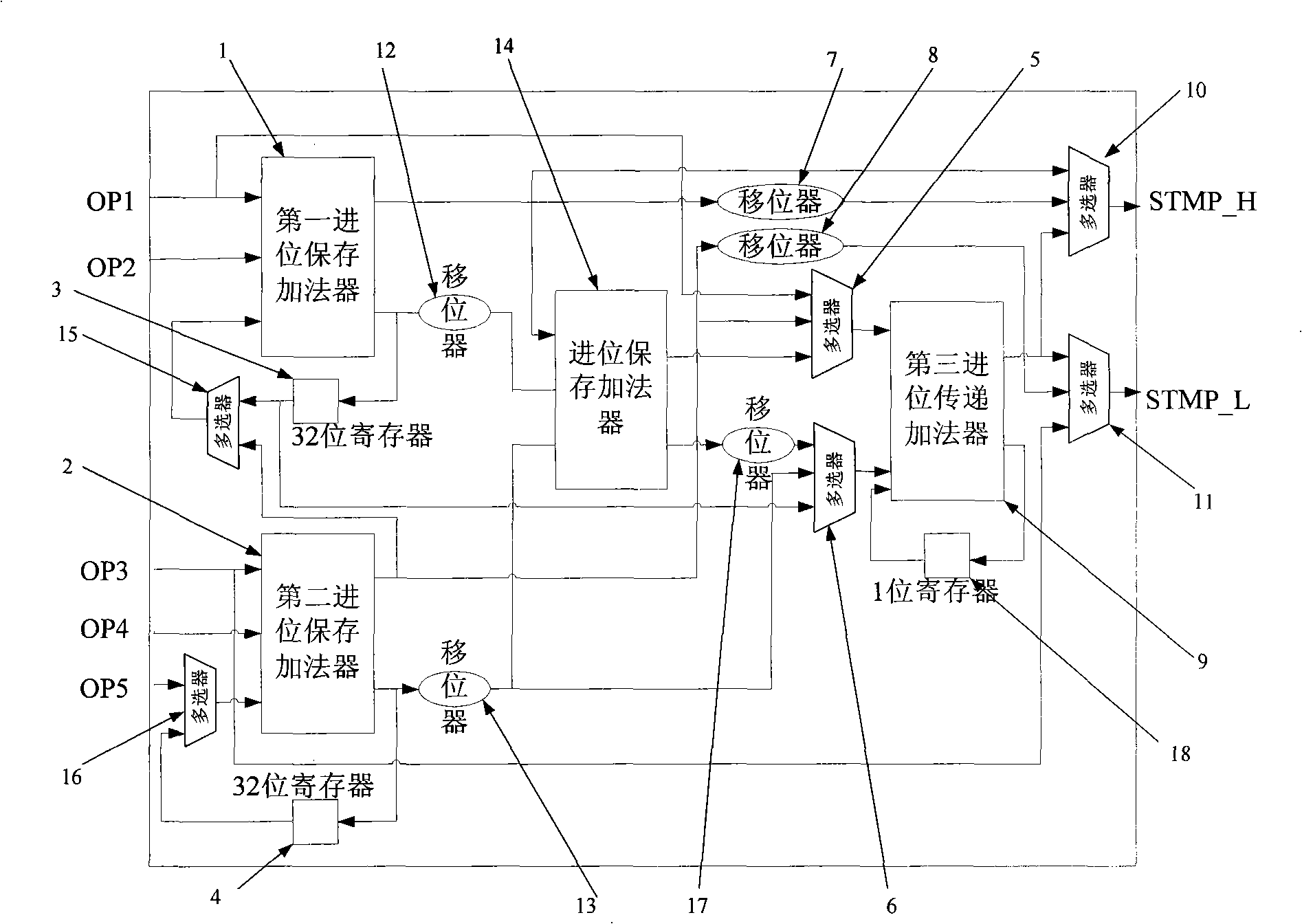

[0127] The RSA / SHA multiplexing encryption unit applicable to RISC processors proposed by the present invention consists of 3 carry save adders, a carry transfer adder, 6 multiplexers, 2 32-bit registers, a 1-bit register, 5 Composed of shifters. Further describe the present invention below in conjunction with accompanying drawing.

[0128] The present invention has two working modes, RSA mode and SHA-1 mode. Mode selection is determined by the command. Such as Figure 4 As shown, the instruction memory 19 is accessed according to the address generated by the address generation unit 20, and the instruction is taken out from the instruction memory 19 and sent to the inter-stage latch 21. The instruction is decoded by the decoding unit 25 to determine which instruction it belongs to and generate The mode selection signal is sent to the RSA / SHA multiplexing encryption unit 27 after being cached by the inter-stage latch 22 for one cycle.

[0129] When the RSA / SHA multiplexing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com