Chip stack packaging structure and method of producing the same

A technology of packaging structure and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc. Solve the effect of low packaging density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0062] In order to make the above and other objects, features, advantages and embodiments of the present invention more clearly understood, several chip stack packaging structures are provided as preferred embodiments for further description.

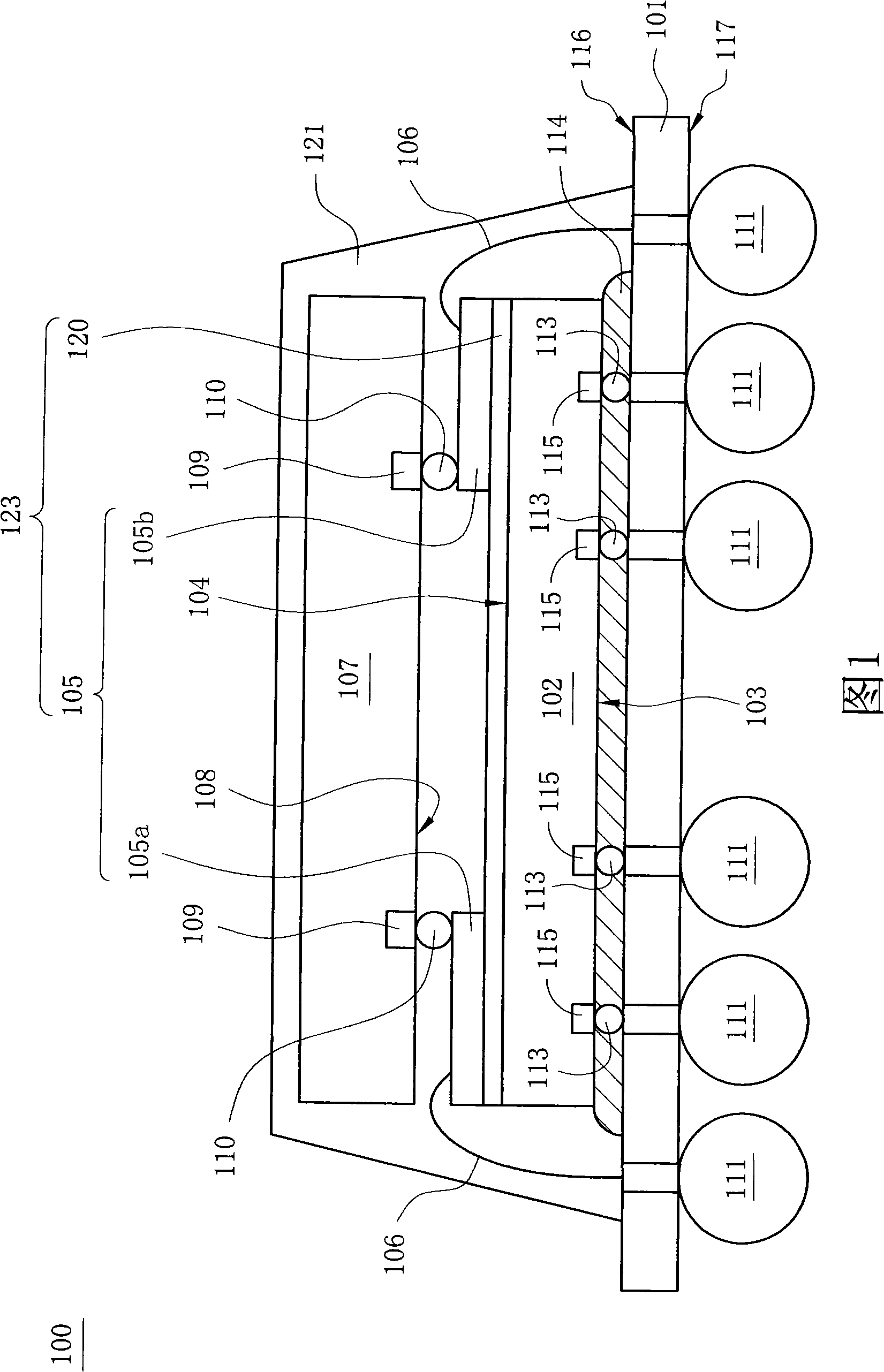

[0063] Please refer to FIG. 1 . FIG. 1 is a schematic cross-sectional view of a chip stack package structure 100 according to a first preferred embodiment of the present invention.

[0064] The chip stack package structure 100 includes: a base material 101 , a first chip 102 , a circuit substrate 123 , a second chip 107 and a sealing resin 120 .

[0065] First, a substrate 101 is provided, and the substrate has a first surface 116 and an opposite second surface 117 . In a preferred embodiment of the present invention, the substrate 101 is formed of a lead frame, a printed circuit board or a die carrier. In this embodiment, the base material 101 is a printed circuit board, and its material is, for example, BT or FR4 circuit board or oth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More