Flash memory and manufacturing method thereof

A manufacturing method and flash memory technology, which can be applied to electrical components, electrical solid devices, circuits, etc., can solve problems such as unfavorable and unfavorable component erasing operations, and achieve improved performance, improved memory data retention, and elimination of memory cell dislocations. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

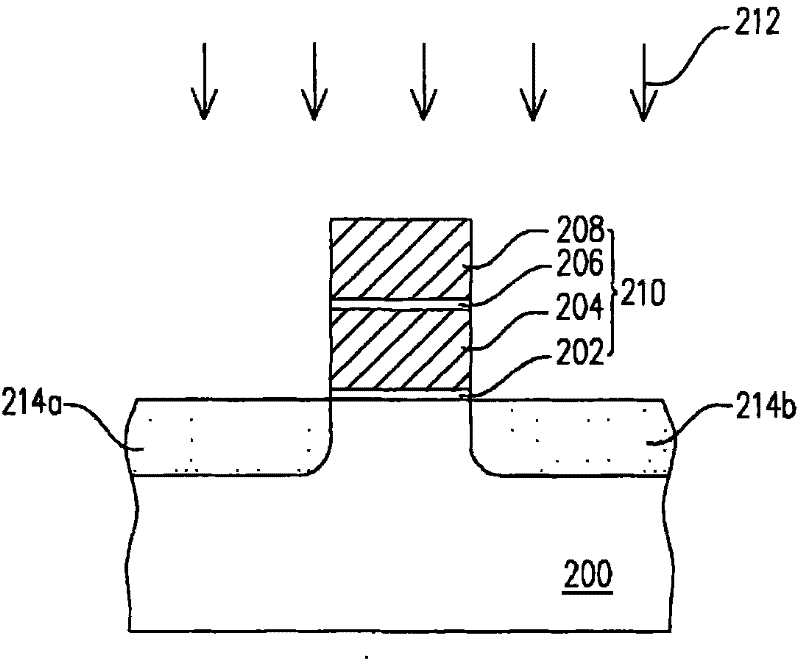

[0051] Figure 2A to Figure 2E is a sectional view of a manufacturing process of a flash memory according to an embodiment of the present invention.

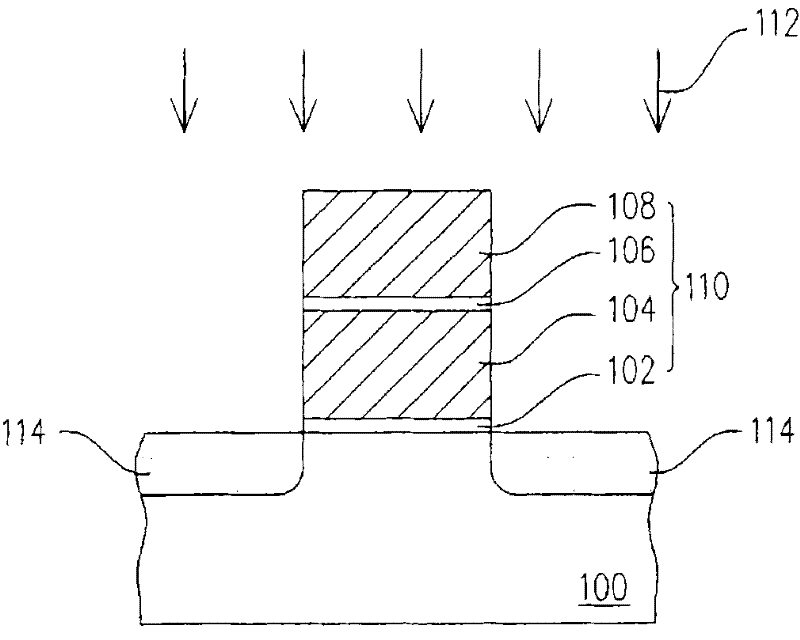

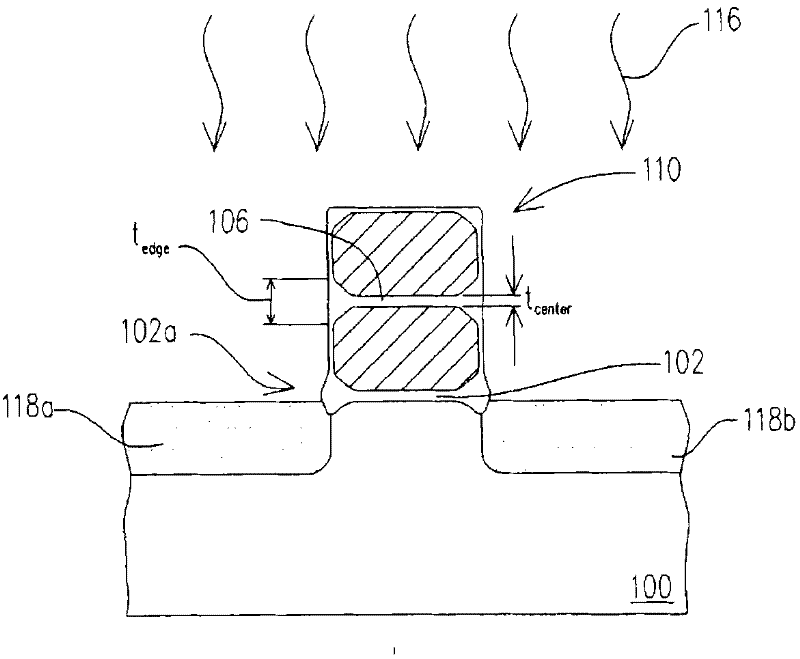

[0052] Please refer to Figure 2A , forming a stack structure 210 on the substrate 200, for example, the stack structure 210 includes a tunnel oxide layer 202, a charge storage layer 204, an intergate dielectric layer 206 and a layer Control grid 208 . Wherein, the material of the charge storage layer 204 is, for example, doped polysilicon, silicon nitride or other materials capable of storing charges. The tunnel oxide layer 202 and the inter-gate dielectric layer 206 are, for example, one of materials selected from oxide layers, nitride layers, nitride and oxide layers, oxide, nitride and oxide layers. The material of the control gate 208 is, for example, selected from one of materials composed of doped polysilicon, metal silicide, and conductive metal. In addition, the stack structure 210 may include other film layers, suc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More