Micro lead frame semiconductor packaging method

A lead frame and packaging method technology, which is applied in the field of new packaging manufacturing, can solve the problems of poor fragmentation of IC components, reduced reliability and penetration of micro-lead frame IC components, and achieves control of poor fragmentation and improvement of reliability. bad effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

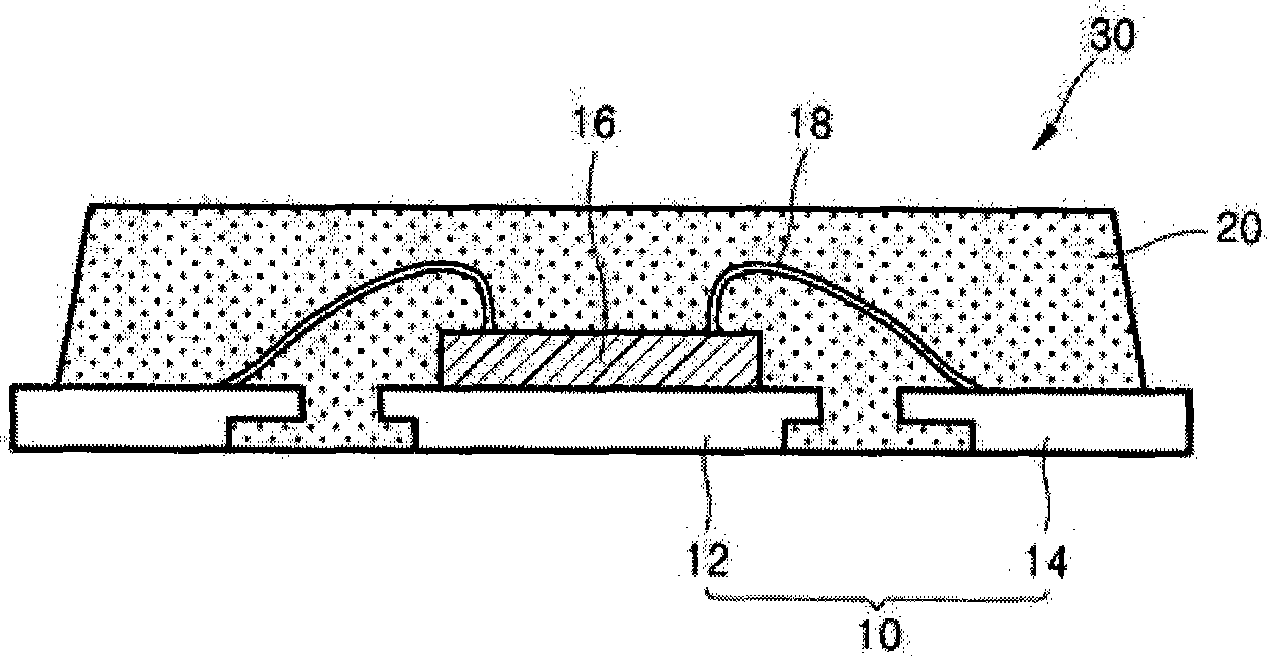

[0018] figure 1 It is a cross-sectional view of an M.L.F type IC component package of the prior art, and the M.L.F type semiconductor package 30 of the prior art is shown in the figure. The lead frame type lead frame 10 is composed of a chip pasted on the substrate and a lead 18 connecting the chip 16 and the pin 14 .

[0019] figure 2 It is a plan view of M.L.F packaged IC components in the prior art, the exposed portion 24 of the pin 14 of the lead frame 10, the exposed portion 22 of the connecting rib of the lead frame 10, and the exposed portion between the exposed pin and the pin. Epoxy molding compound 26.

[0020] image 3 It is a cross-sectional view of an M.L.F type packaged IC component of an embodiment of the present invention. The M.L.F type IC component package 30 of an embodiment of the present invention is shown in the figure. The micro-lead frame type lead frame 110 composed of pins 112 is composed of a chip pasted on the substrate and a lead 130 connectin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More