High dielectric constant grid dielectric material forming method and a semiconductor device

A technology of high dielectric constant material and gate dielectric material, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., to improve roughness and quality, and improve charge carrier mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

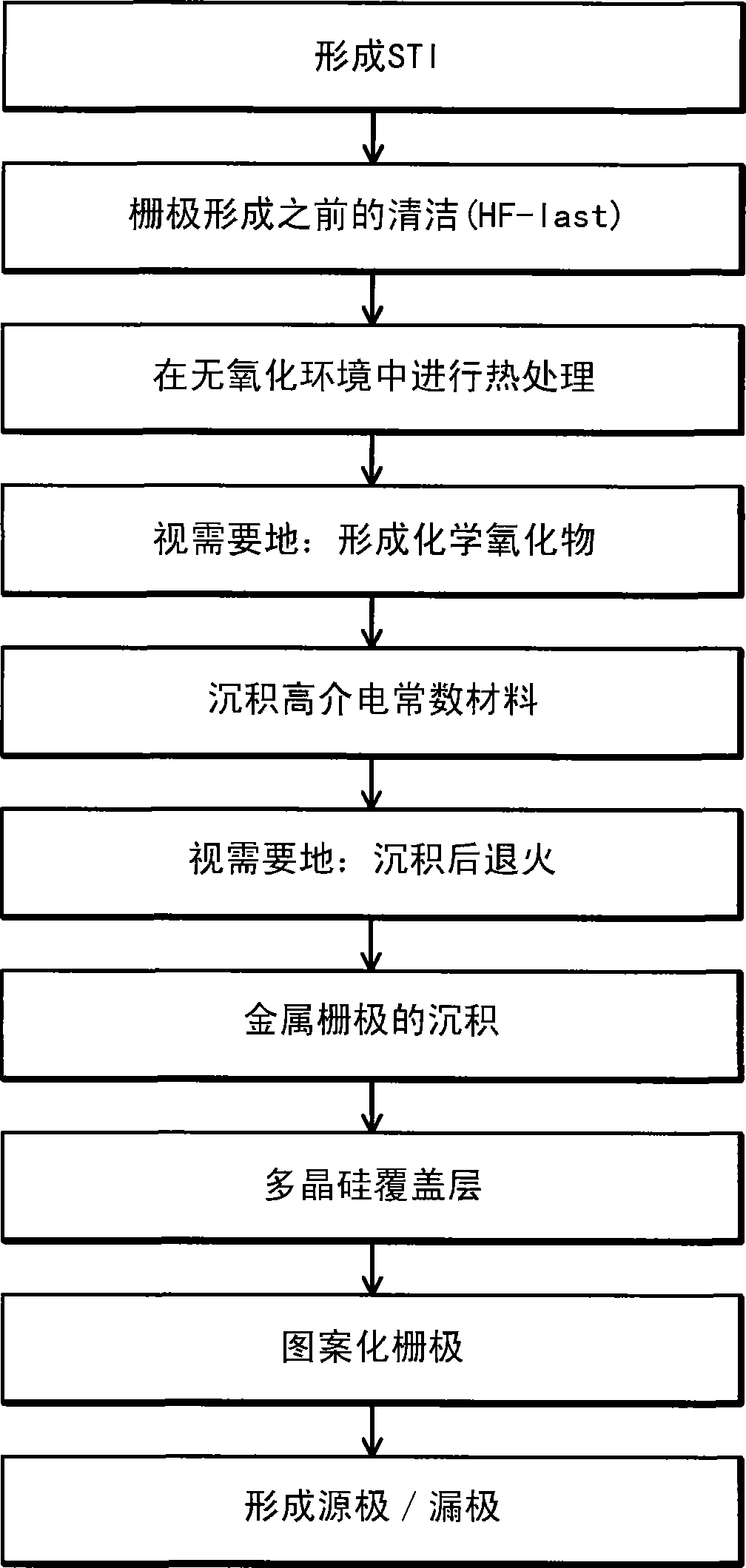

[0043] The present invention is based on the unexpected discovery that a method for carrying out the present invention comprises thermally treating in a non-oxidizing environment containing a passivating gas to form a thin interfacial layer.

[0044] The so-called "oxidative-free environment" in the present invention refers to an environment without oxygen. This environment preferably includes an inert gas environment or inert gas mixture, and optionally other additives.

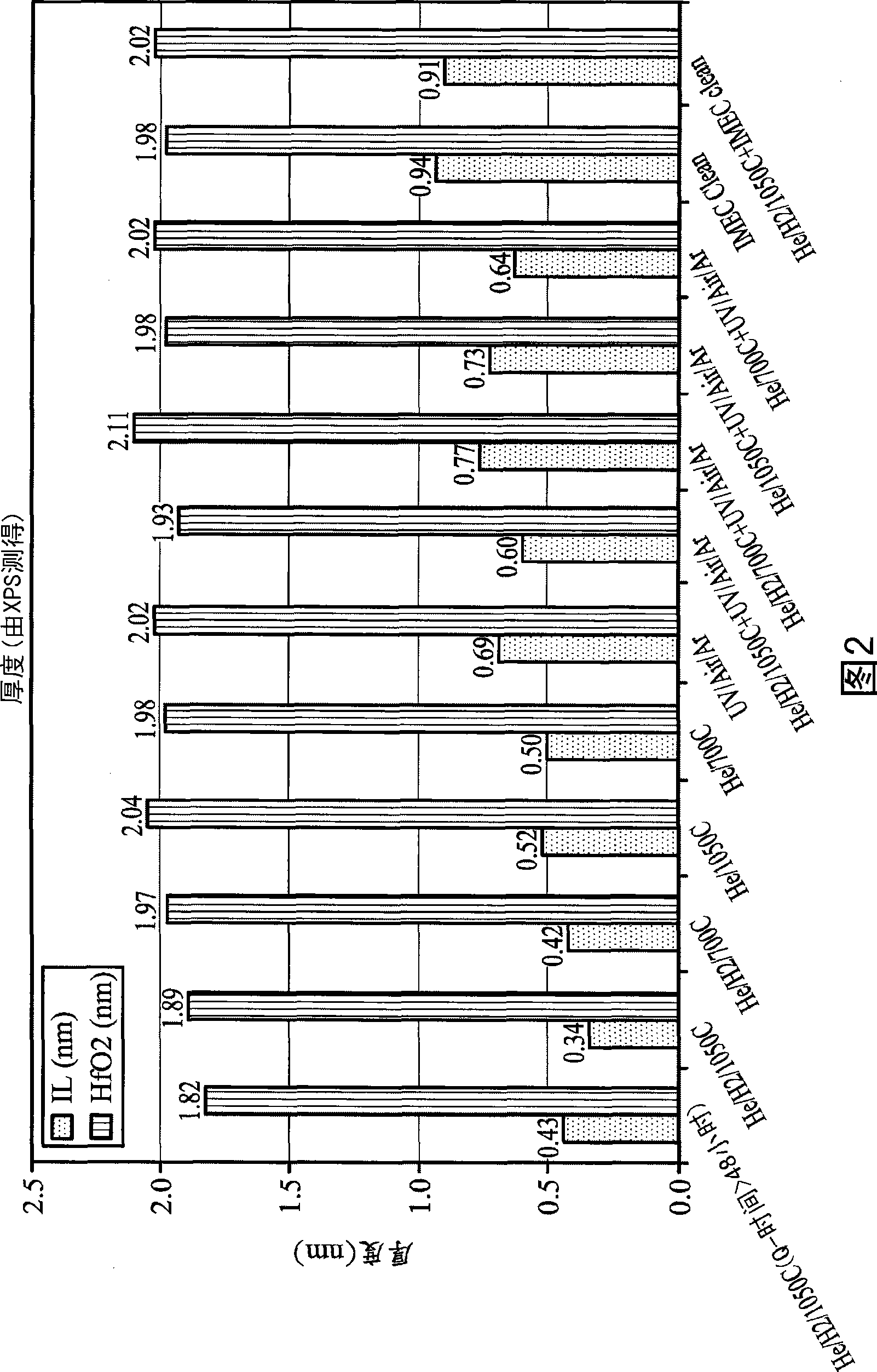

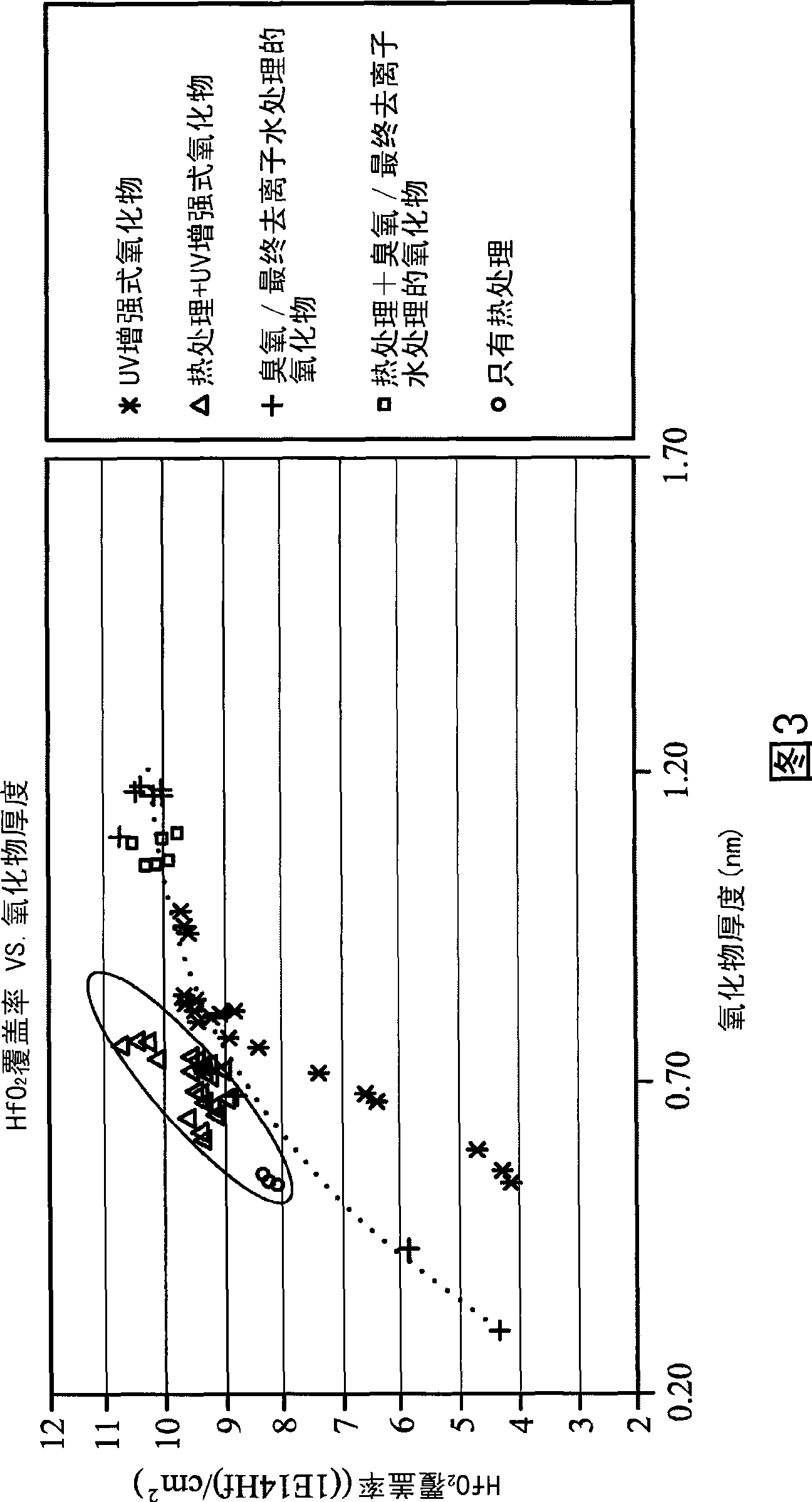

[0045] In particular, the addition of hydrogen in an oxygen-free environment containing a passivation gas environment or a passivation gas mixture can increase the surface smoothness of the thin interfacial layer described above.

[0046] In the present invention, the step of heat treatment is performed after cleaning the substrate and before depositing the high dielectric constant material.

[0047] The so-called "high dielectric constant" of the present invention refers to any dielectric material, which h...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com