Method of manufacturing semiconductor chip

一种制造方法、半导体的技术,应用在半导体/固态器件制造、半导体器件、电固体器件等方向,能够解决测试图案除去等问题,达到通用特性保证、高效率的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Embodiment modes of the present invention are described below with reference to the drawings.

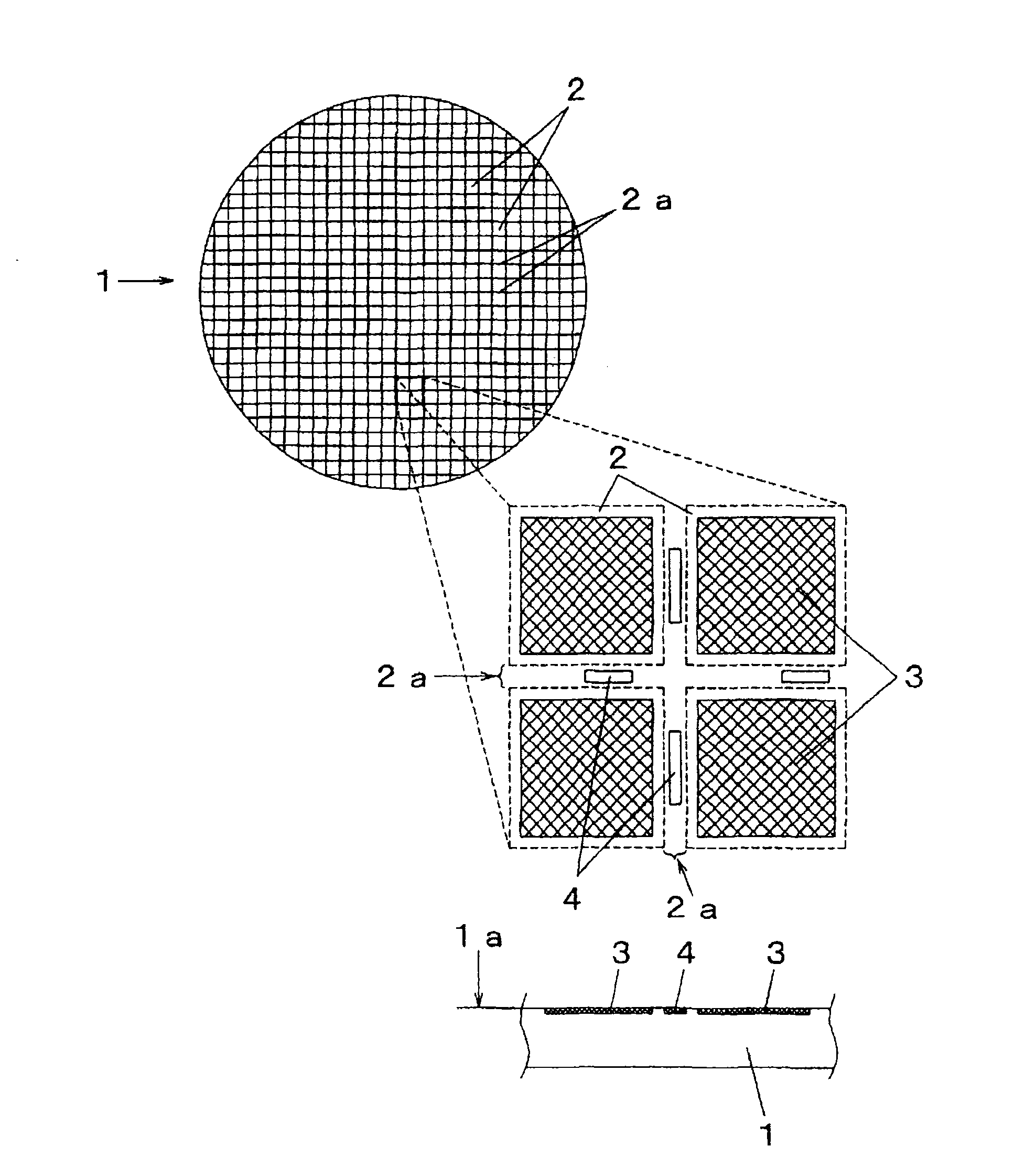

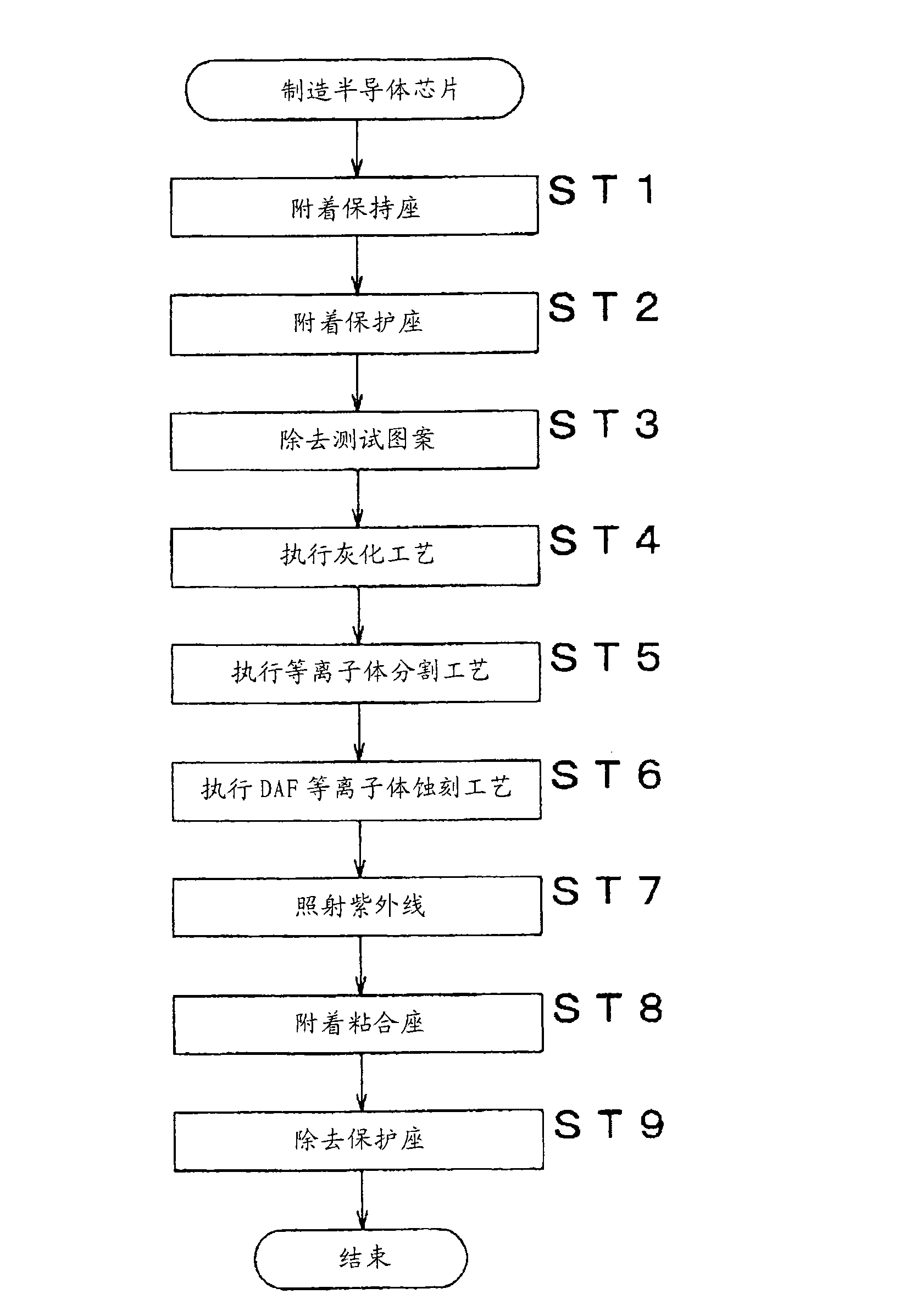

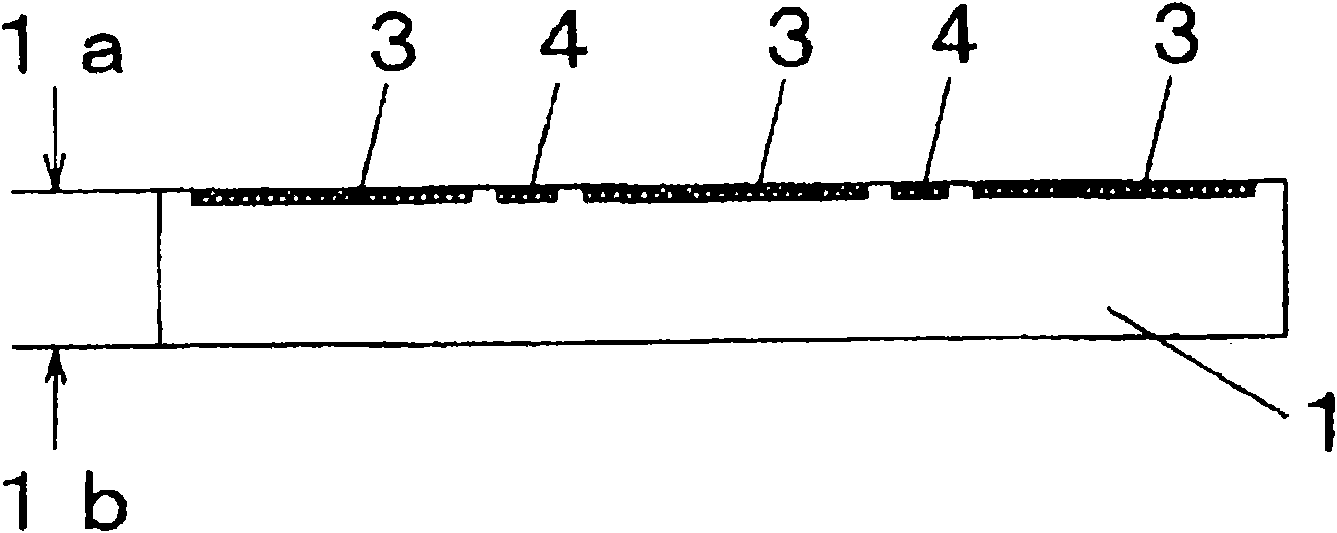

[0030] First, refer to figure 1 The semiconductor wafer 1 used in the semiconductor chip manufacturing method of the embodiment mode of the present invention will be described. exist figure 1 In , the semiconductor wafer 1 has been partitioned into a plurality of chip regions 2 (regions) in a rectangular shape by using scribe lines 2a arranged in a lattice shape, thereby cutting the respective semiconductor chips from each other. On the front side 1a opposite to the circuit formation side of the semiconductor wafer 1, each integrated circuit 3 has been formed in each chip region 2, and test patterns 4 have been formed in the scribe lines 2a. The test pattern 4 is used for characteristic tests and the like in the semiconductor chip manufacturing steps, and is removed after the function of the test pattern 4 has been achieved. In the semiconductor chip manufacturing method s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More