An anti-SEE system and method based on synchronizing redundant threads and coding technique

An anti-single event effect and coding technology, applied in the system field of anti-single event effect, can solve the problems of increasing system hardware overhead, sensitivity, hidden danger of single-event overturn, etc., achieving strong real-time error correction, avoiding performance loss, and controlling simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

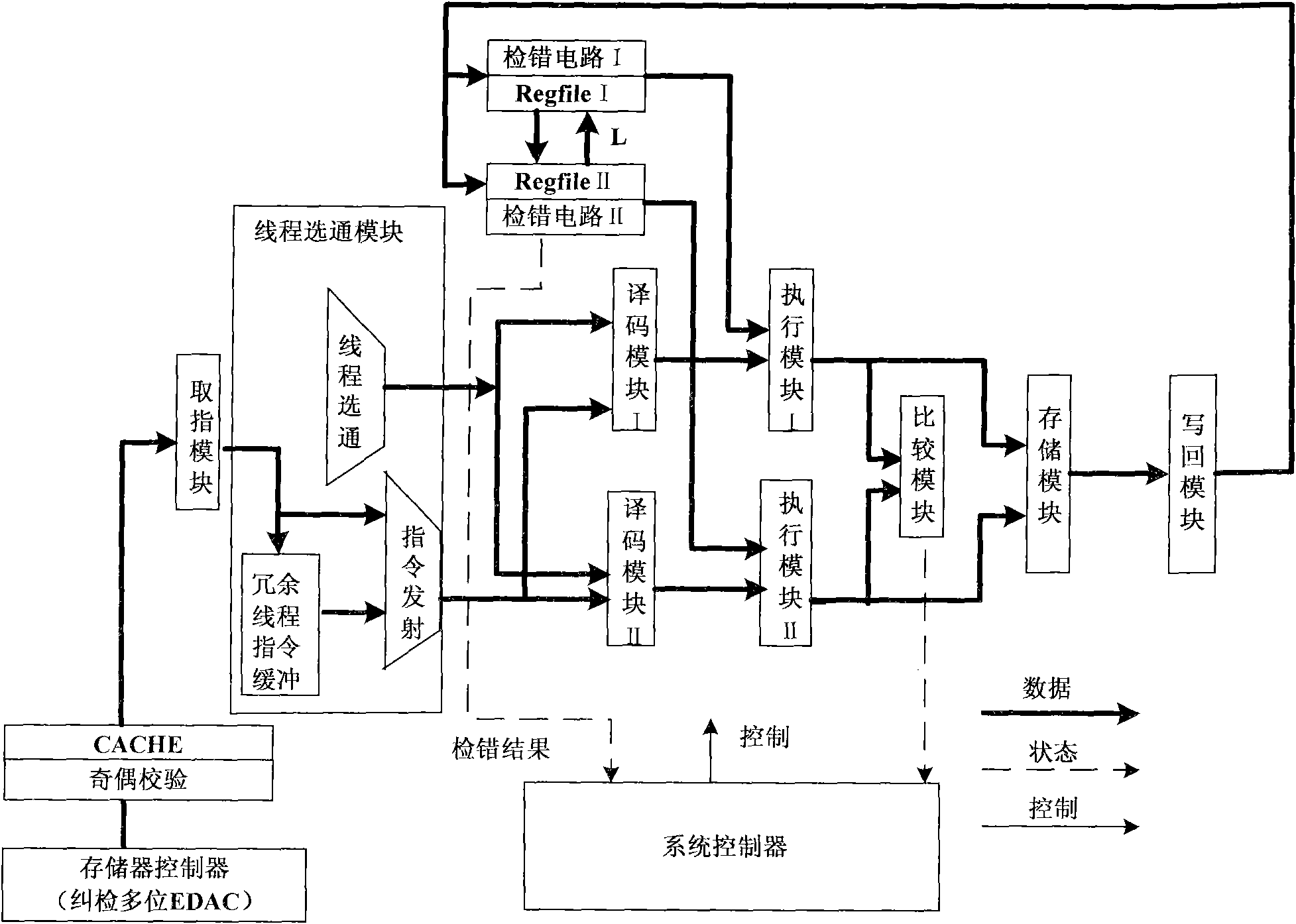

[0036] Such as figure 1 As shown, the system of the present invention includes an instruction fetch module, a thread gating module, a decoding module I, an execution module I, a decoding module II, an execution module II, an error detection circuit I, an error detection circuit II, a register file I (Regfile I ), register file II (Regfile II), comparison module, memory module and system controller;

[0037] The instruction fetching module reads the instruction A from the hit CACHE or from the external memory according to the system controller, and caches the read instruction A; the instruction read from the external memory needs to undergo EDAC error correction and error detection Processing; the instructions read from the hit CACHE are processed through parity; these two processing methods are technologies well known to those skilled in the art, and will not be described in detail here. For EDAC error correction and error detection processing, please refer to Chinese patent 2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More