Method for producing semiconductor packaging part

A semiconductor and packaging technology, applied in the field of flip-chip semiconductor packaging manufacturing, can solve the problems of tool wear, increase manufacturing cost and complexity, reduce waste, improve product yield, and reduce tool wear. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0063] see Figure 3A to Figure 3G , is the first embodiment of the manufacturing method of the semiconductor package proposed by the present invention.

[0064] Such as Figure 3A As shown, a carrier 30 is provided, and the carrier 30 has a plurality of openings 300 thereon. The carrier 30 is made of organic insulating materials such as FR4, FR5, BT and the like.

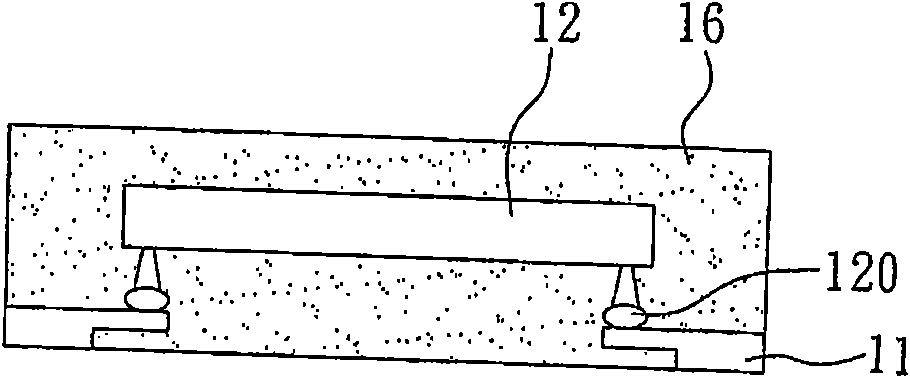

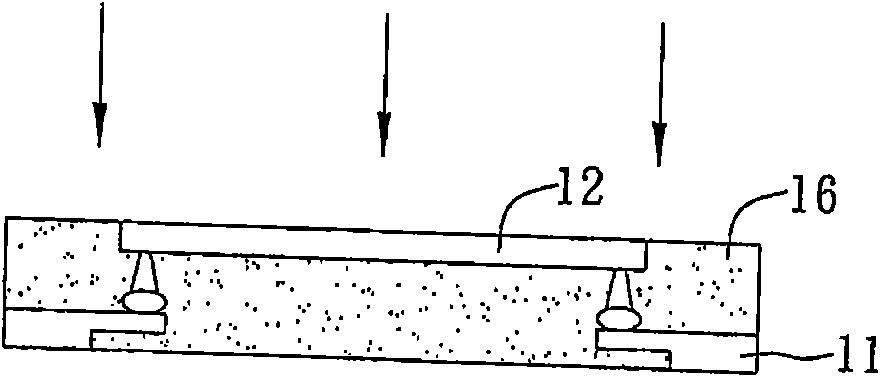

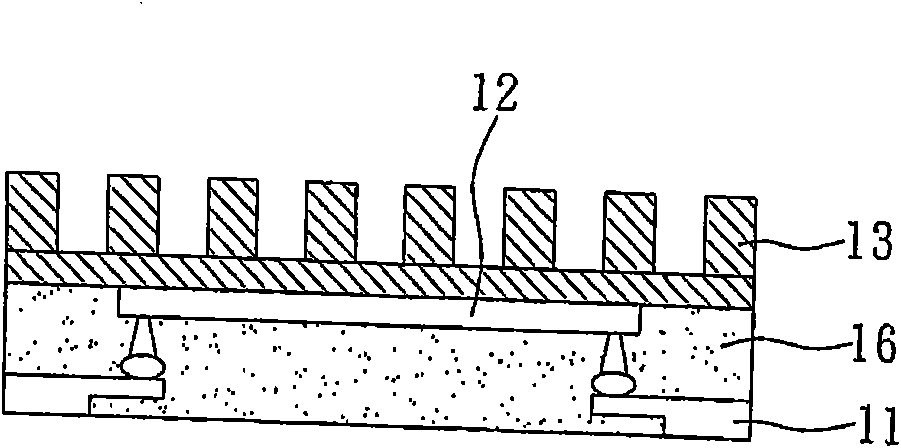

[0065] Such as Figure 3B As shown, a plurality of substrates 31 are provided for the flip-chip semiconductor chips 32 to be connected and electrically connected to the substrates 31 through conductive bumps 320, and the flip-chip semiconductor chips 32 are connected with The heat sink 33 , wherein the length and width of the substrate 31 are approximately equal to the predetermined length and width of the semiconductor package to be completed, and the length and width of the heat sink 33 are smaller than the length and width of the substrate 31 .

[0066] Such as Figure 3C As shown, the plurality of substrat...

no. 2 example

[0078] see Figure 4A to Figure 4E , is a schematic diagram of the second embodiment of the manufacturing method of the semiconductor package of the present invention.

[0079] In addition to selecting organic insulating materials such as FR4, FR5, BT, etc., the carrier of the present invention can also use a metal material coated with a metal coating on the surface. The metal coating is a coating material that is not easy to adhere to the packaging colloid. In this embodiment The predetermined length and width dimensions of the semiconductor package, the preparation dimensions of the substrate, the flip-chip semiconductor chip and the heat sink, and the opening dimensions of the carrier are all similar to those of the aforementioned first embodiment, and the main difference is that the carrier The selection of materials and some process steps.

[0080] Such as Figure 4A As shown, a carrier 40 is prepared, and the carrier 40 has a plurality of openings 400, wherein the carr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More