Semiconductor encapsulation structure by taking lead frame as substrate and applicable lead frame thereof

A lead frame and semiconductor technology, applied in the field of lead frame, can solve problems such as the inclination or displacement of the chip 140, the length of the first pin 110 cannot be shortened, and the structural strength of the chip 140 cannot be provided, so as to strengthen the chip load strength and increase the chip load The effect of strength and strengthening the locking ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

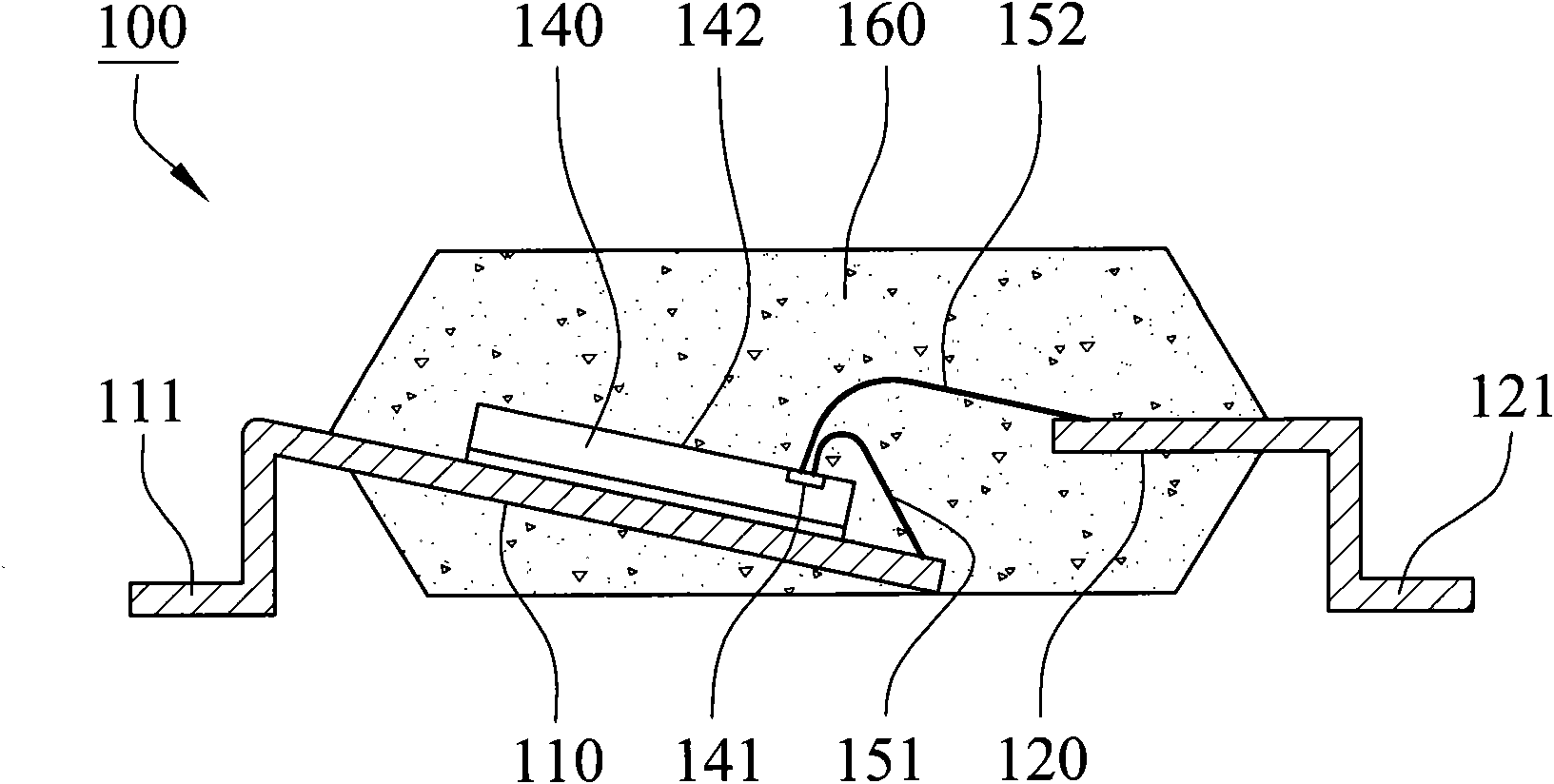

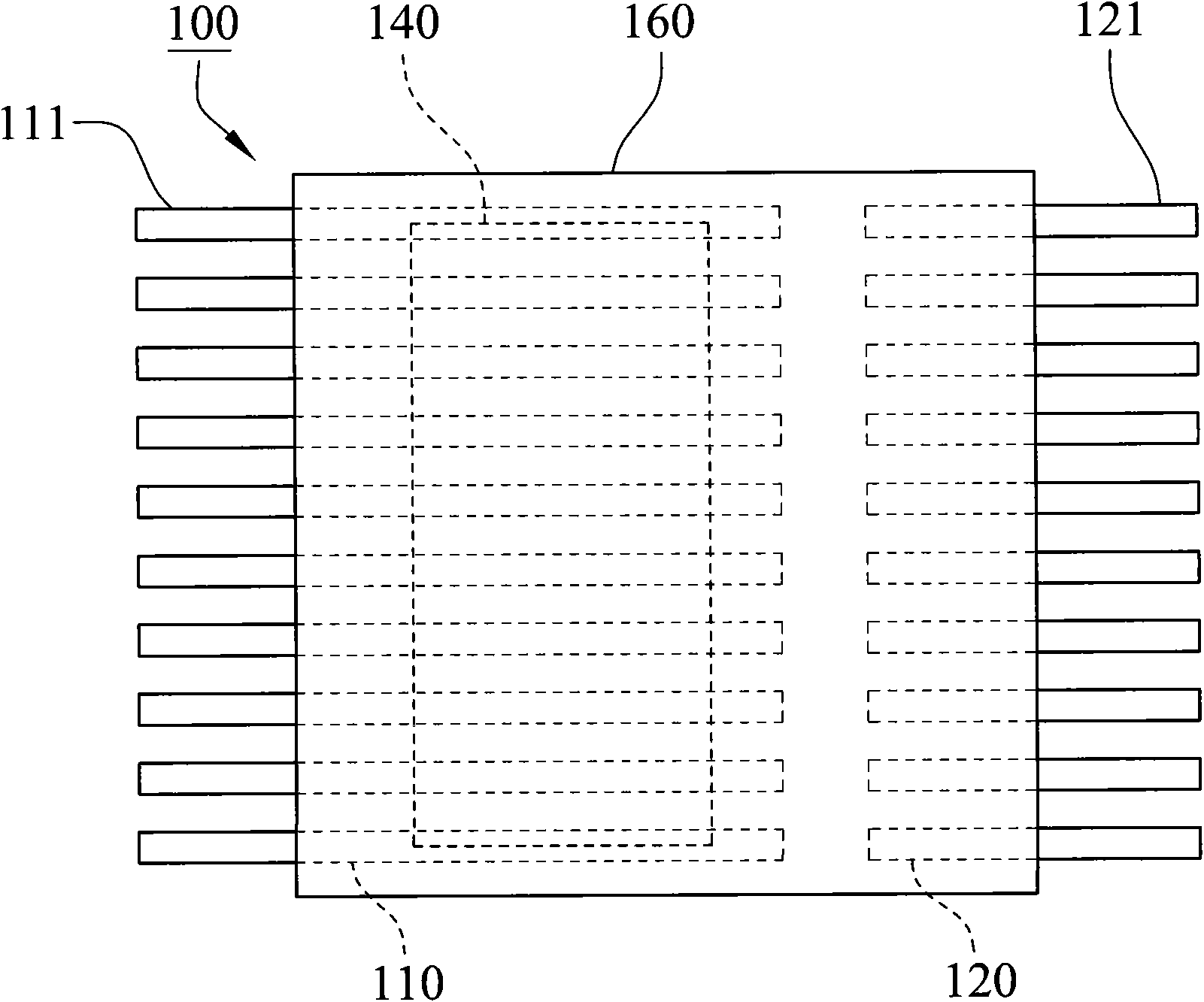

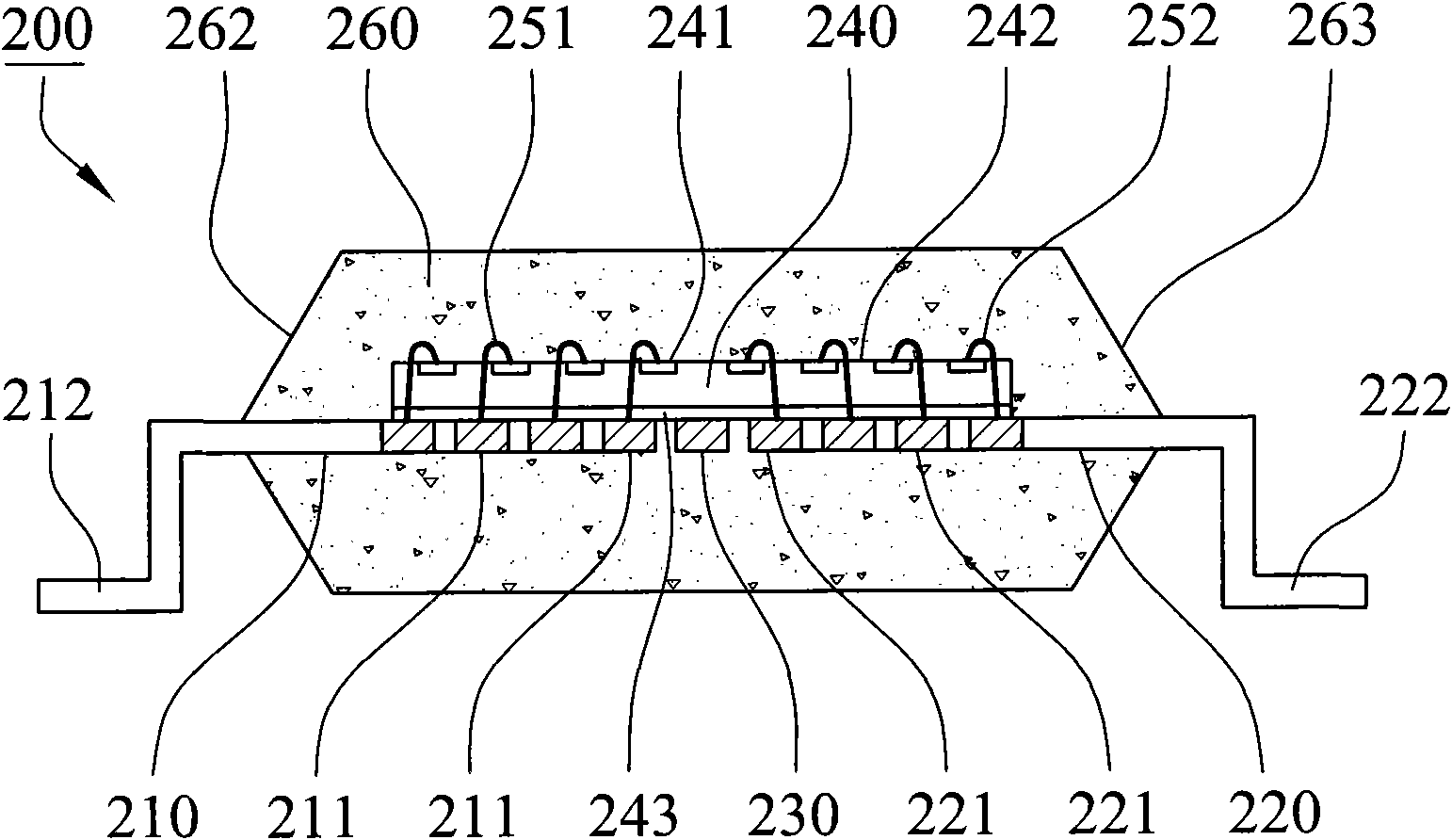

[0045] According to a specific embodiment of the present invention, a semiconductor package structure based on a lead frame and an applicable lead frame are disclosed. see image 3 and Figure 4As shown, the semiconductor package structure 200 mainly includes at least one first lead 210, at least one second lead 220, connection bar 230, chip 240, two or more first bonding wires 251, two or two The second bonding wire 252 and the encapsulant 260 above. The semiconductor package structure 200 has a chip-on-lead (COL, Chip-On-Lead) package structure.

[0046] like Figure 5 and Image 6 As shown, the first pin 210, the second pin 220 and the connection bar 230 form the same lead frame, including the same metal material, generally made of copper or iron metal, and have an appropriate thickness (about 0.2mm) . Each first pin 210 has a first finger 211 , and each second pin 220 has a second finger 221 . The connecting bar 230 is disposed between the first pin 210 and the seco...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More