Method for forming gate oxide

A gate oxide, thermal oxidation technology, applied in electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as the inability to fundamentally adjust the threshold of a single device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

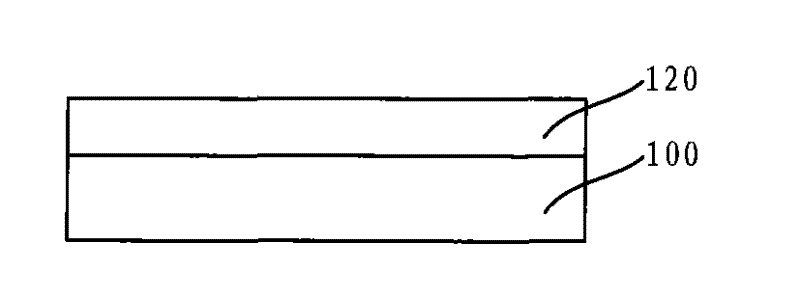

[0041]As a first embodiment of the present invention, the specific steps of forming a gate oxide layer include:

[0042] Step 11: performing a thermal oxidation operation on the substrate, and forming a gate oxide layer with a target thickness on the substrate.

[0043] A well region is formed on a substrate, and an active region of a device is defined, and the base is formed after shallow trench isolation is completed. The substrate includes, but is not limited to, silicon material including semiconductor elements, such as silicon or silicon germanium (SiGe) in single crystal, polycrystalline or amorphous structure, or silicon-on-insulator (SOI).

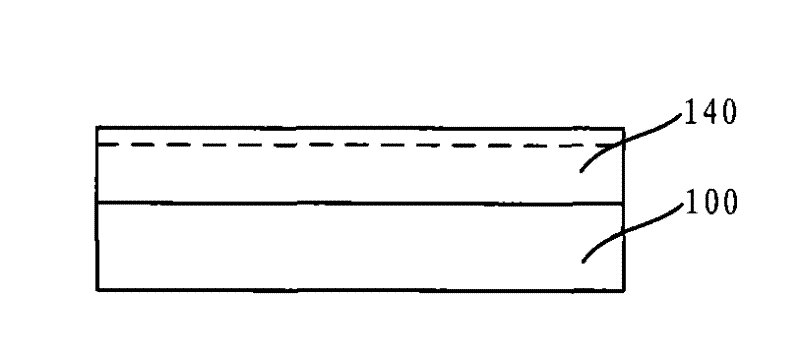

[0044] The well region is formed by an ion implantation process; in the traditional process, after the well region is formed, it undergoes a thermal oxidation operation introduced during the subsequent formation of a gate oxide layer to complete the threshold voltage adjustment operation. Corresponding to a certain operating volta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More