Patents

Literature

65 results about "Triple gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Triple Gate. The set on the right is a triple-arched gate, known as the Triple Gate (Arabic: Bab an-Nabi, "Gate of the Prophet [Muhammad]") - not to be confused with Barclay's Gate, which has the same Arabic name.

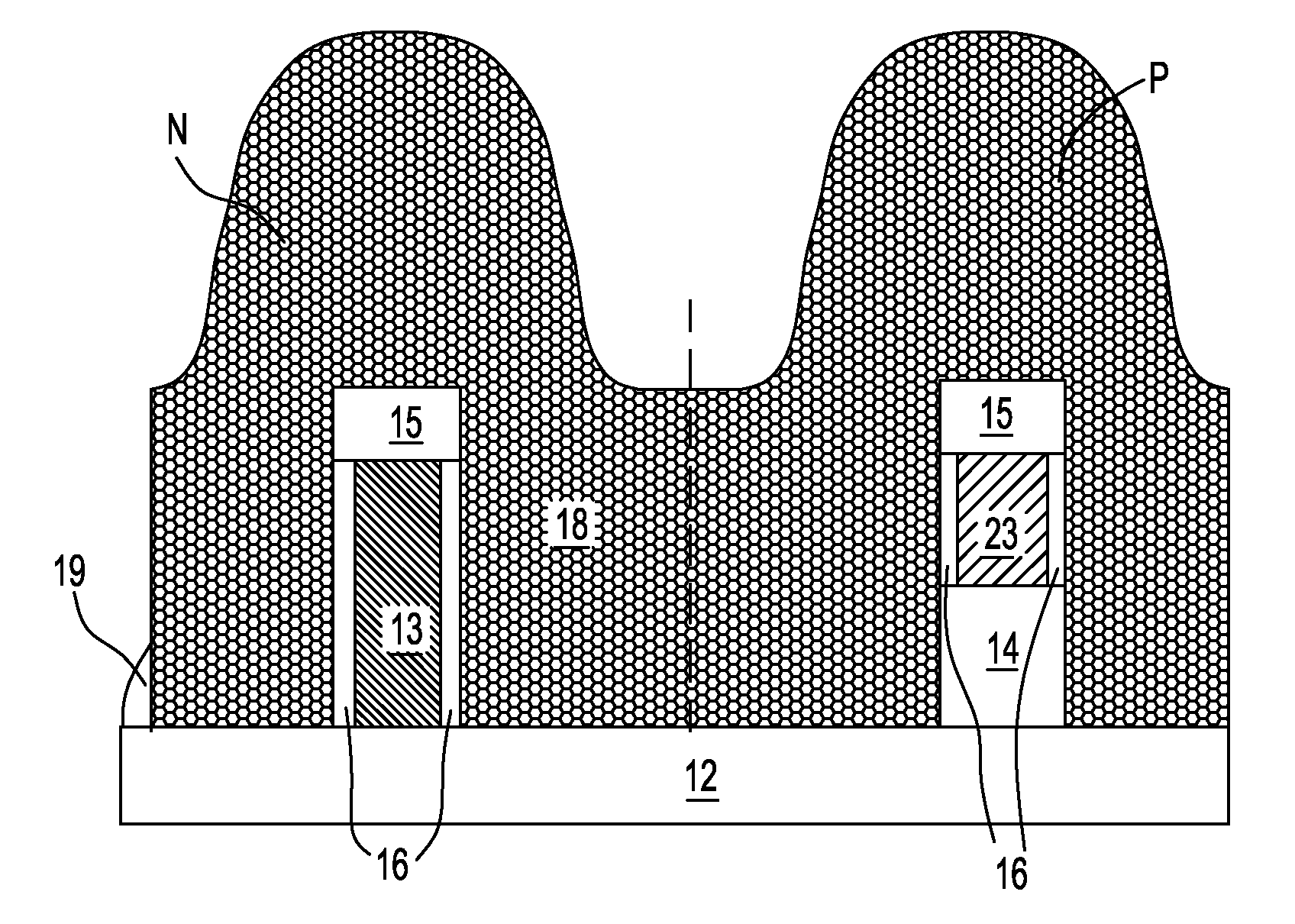

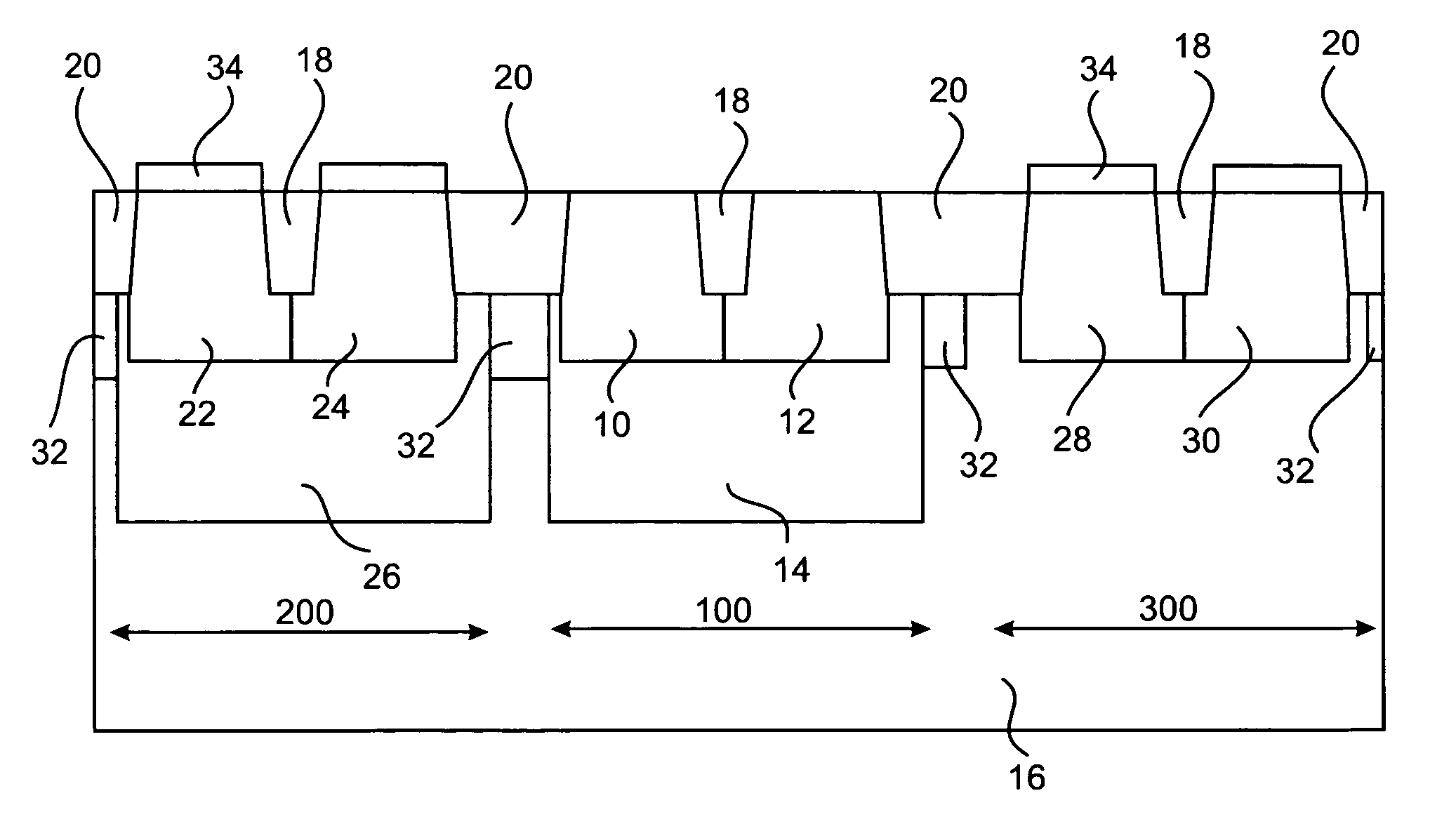

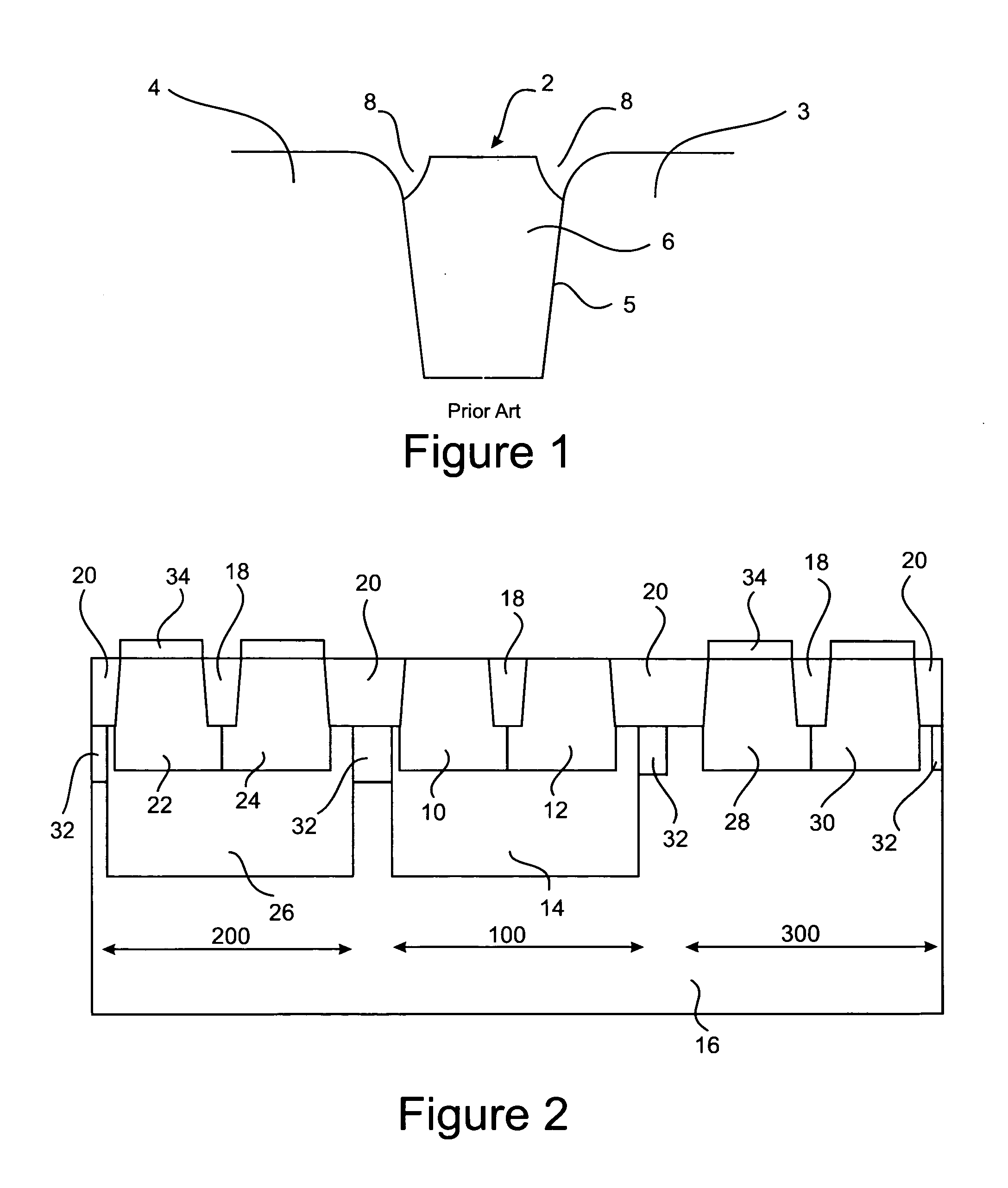

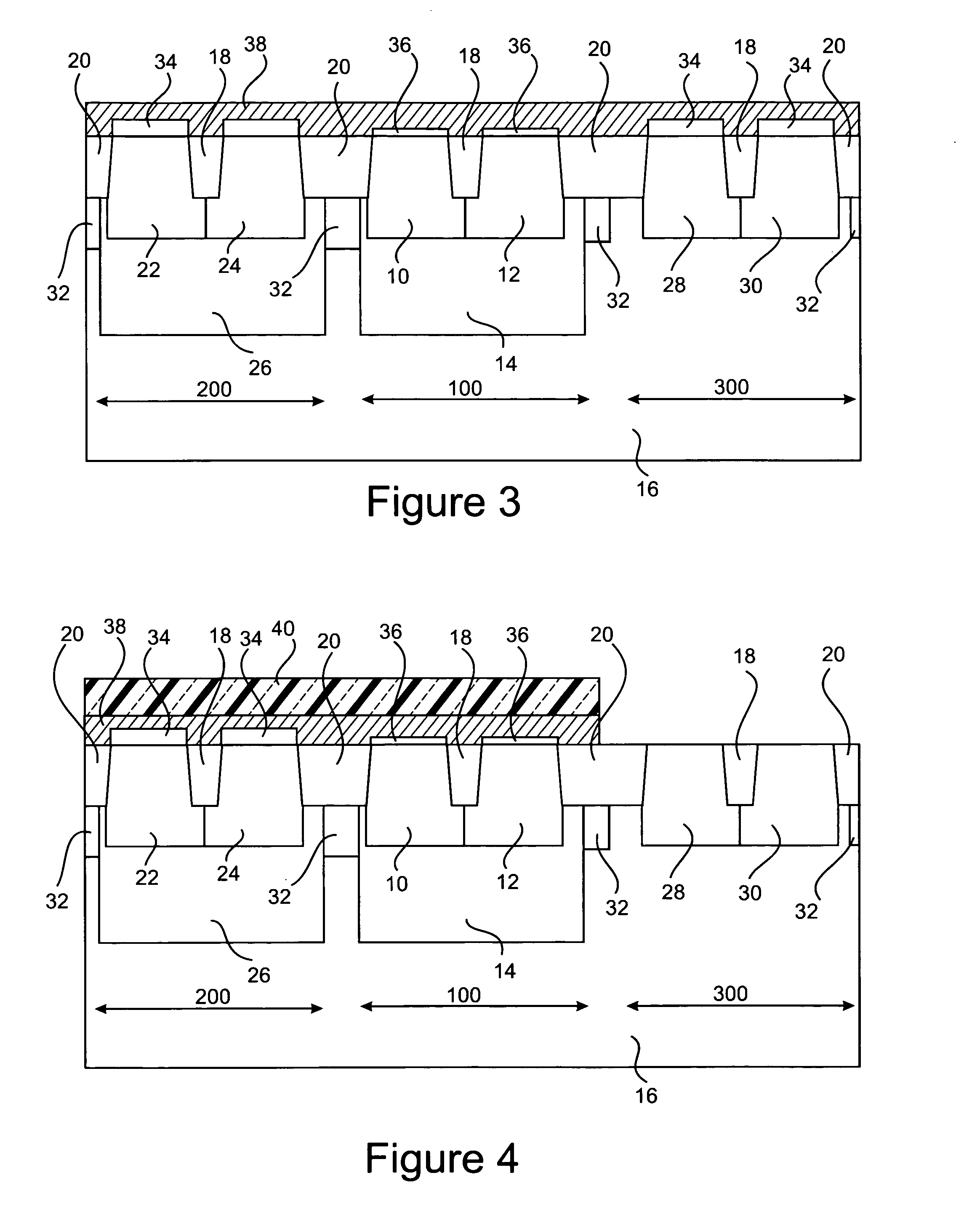

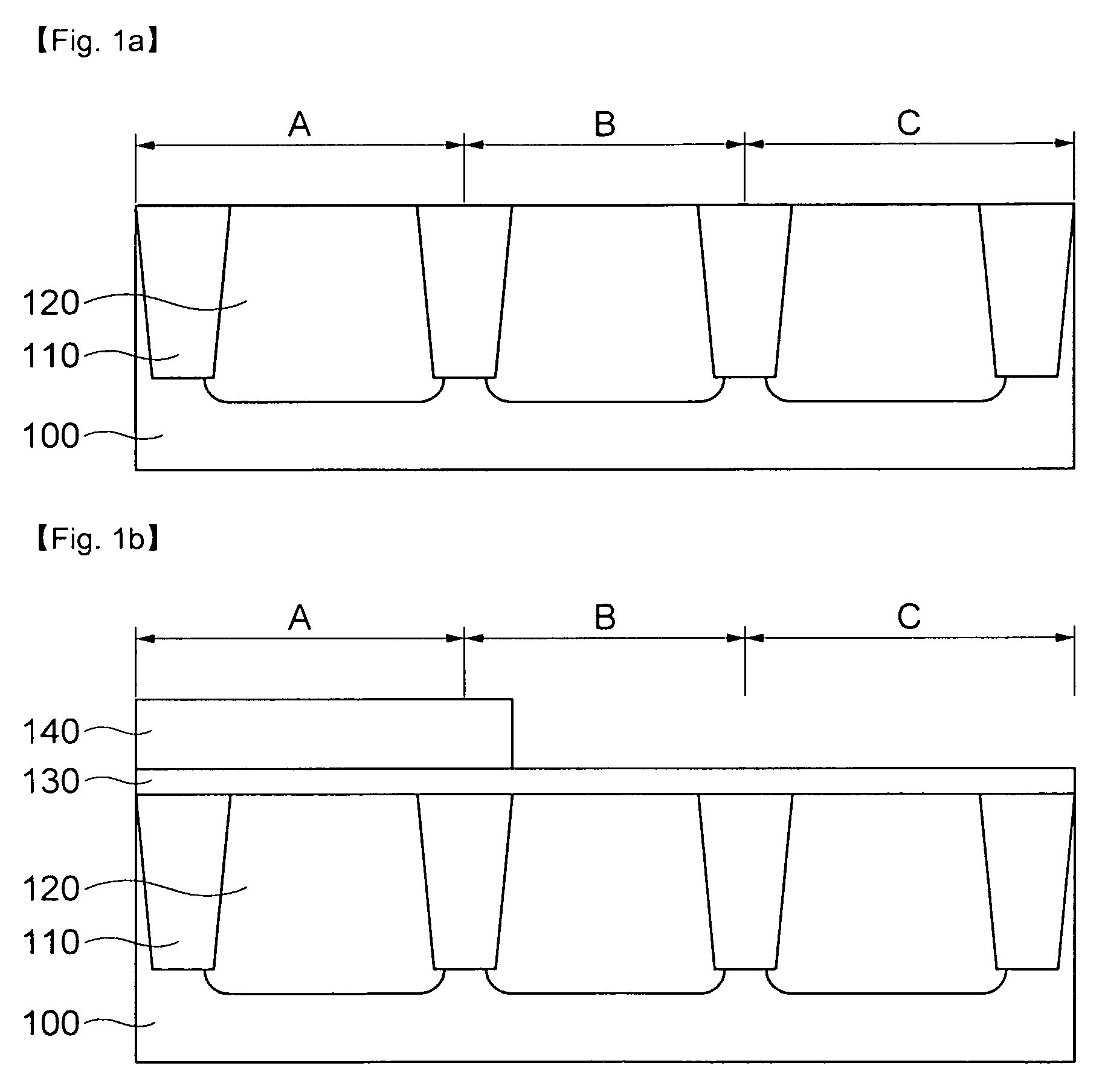

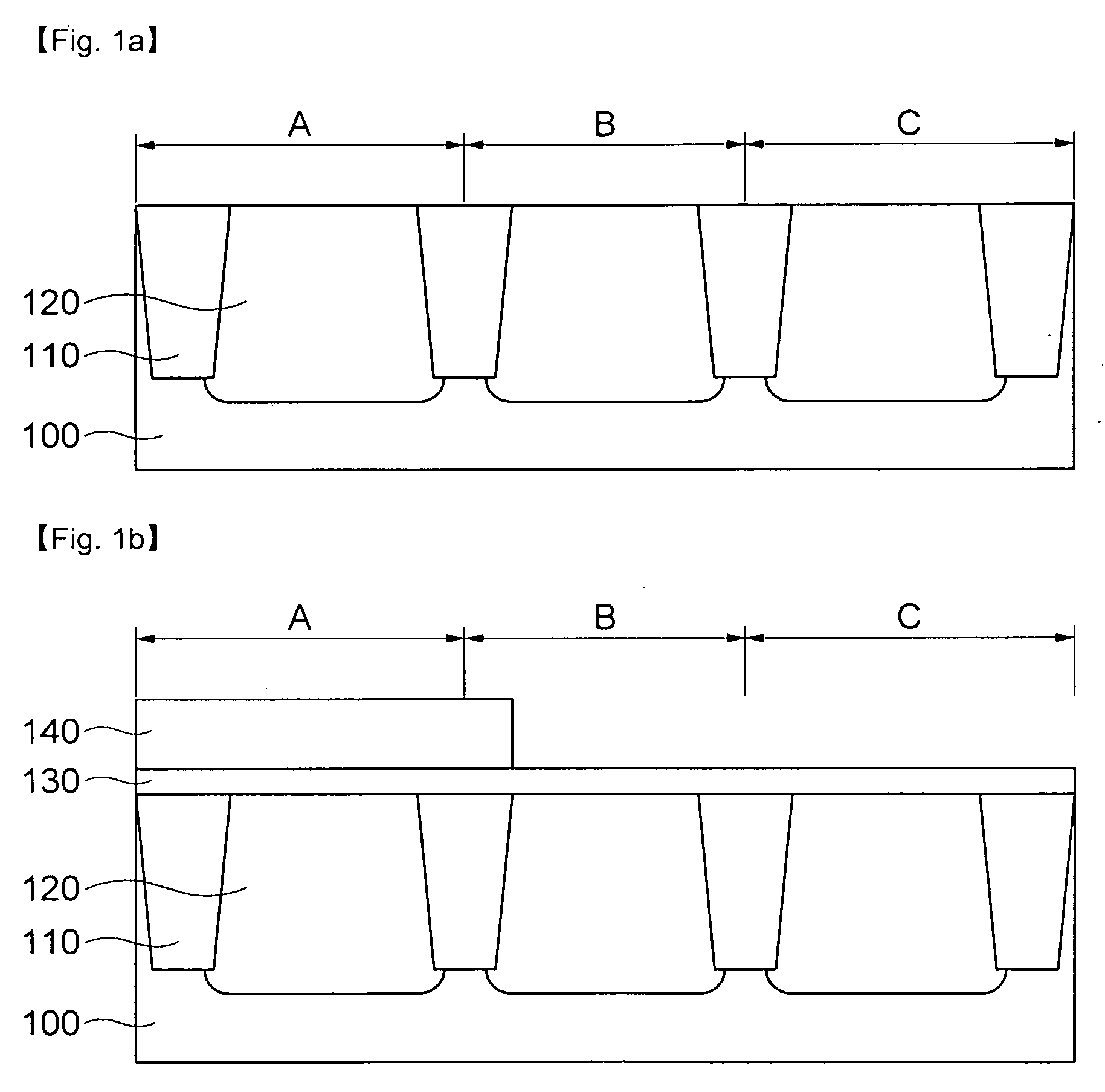

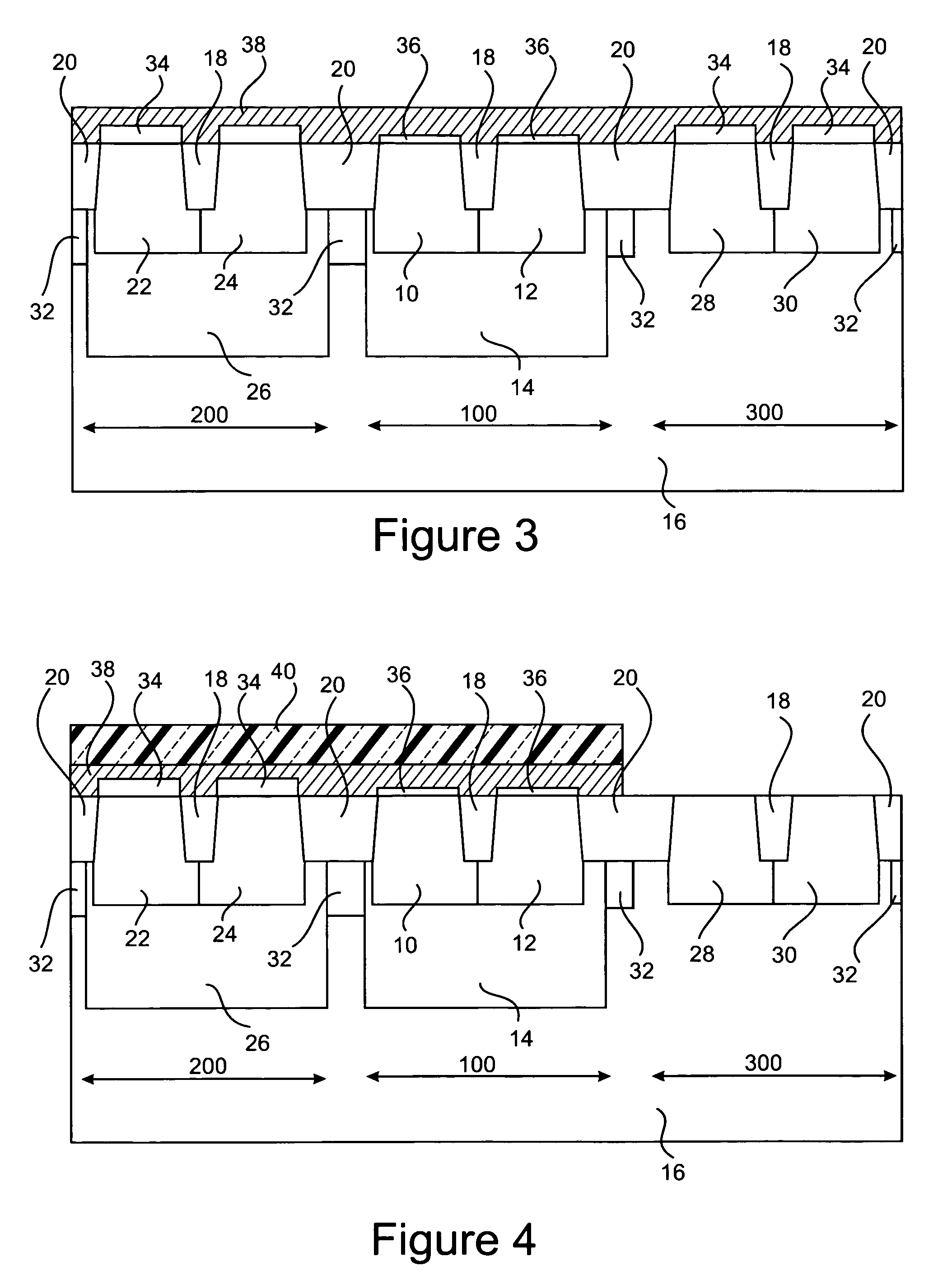

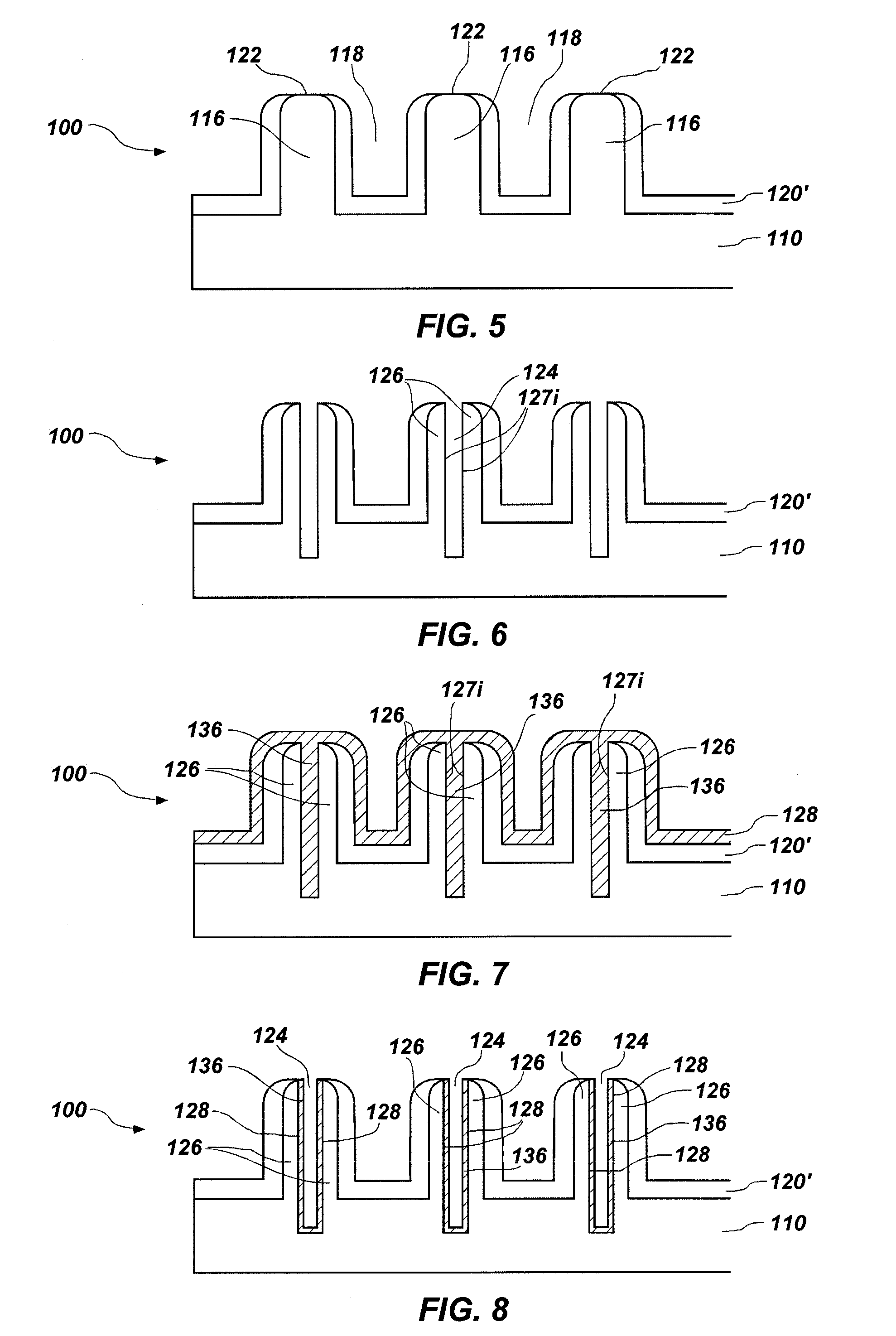

Triple gate and double gate finFETs with different vertical dimension fins

ActiveUS7655989B2Simple and inexpensiveEasy to operateTransistorSolid-state devicesSemiconductor materialsSemiconductor structure

A semiconductor structure and its method of fabrication include multiple finFETs with different vertical dimensions for the semiconductor fins. An implant species is implanted in a bottom portion of selected semiconductor fins on which reduced vertical dimension is desired. The bottom portion of the selected semiconductor fins with implant species is etched selective to the semiconductor material without the implanted species, i.e., the semiconductor material in the top portion of the semiconductor fin and other semiconductor fins without the implanted species. FinFETs with the full vertical dimension fins and a high on-current and finFETs with reduced vertical dimension fins with a low on-current thus results on the same semiconductor substrate. By adjusting the depth of the implant species, the vertical dimension of the semiconductor fins may be adjusted in selected finFETs.

Owner:GLOBALFOUNDRIES U S INC

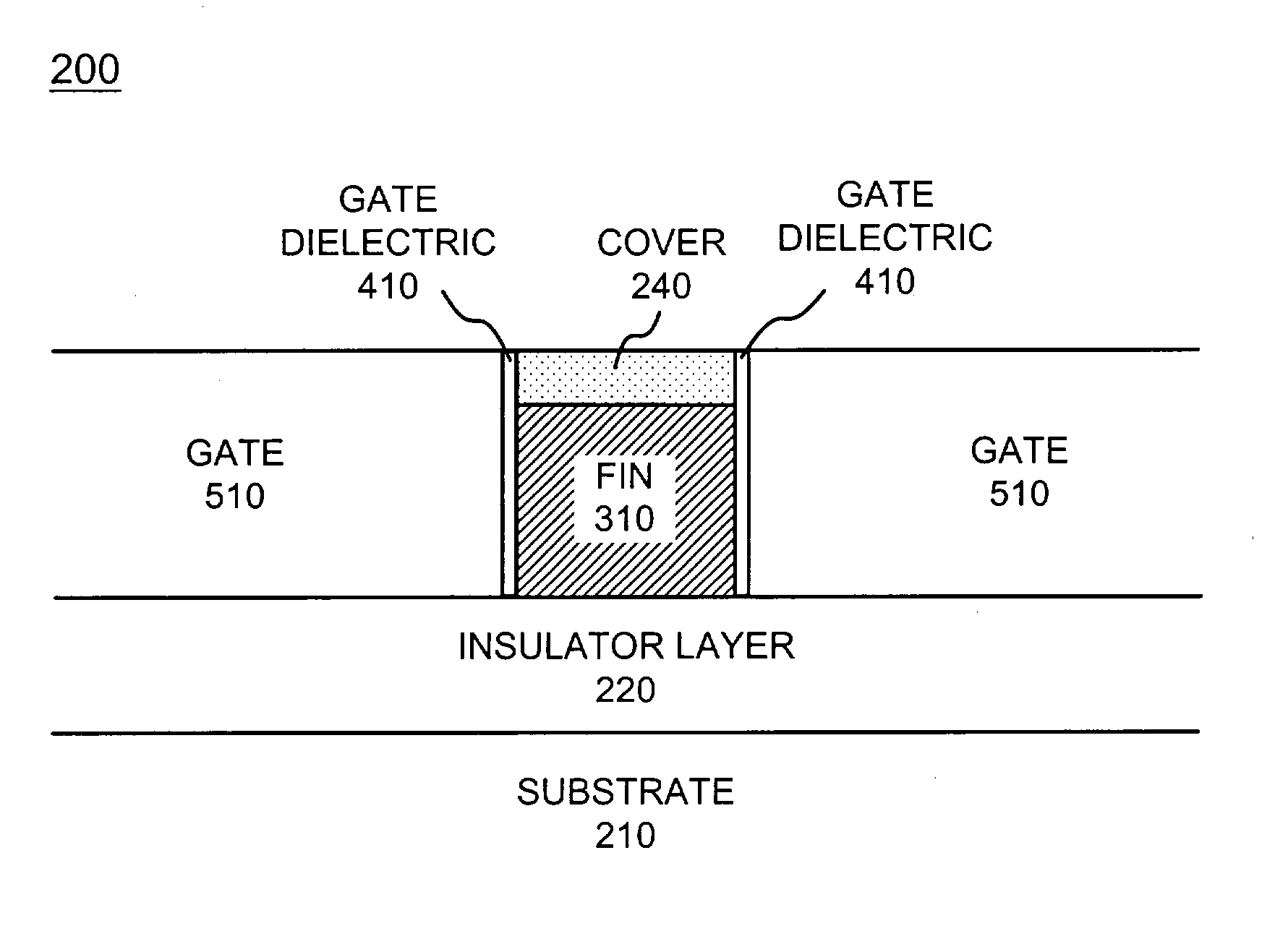

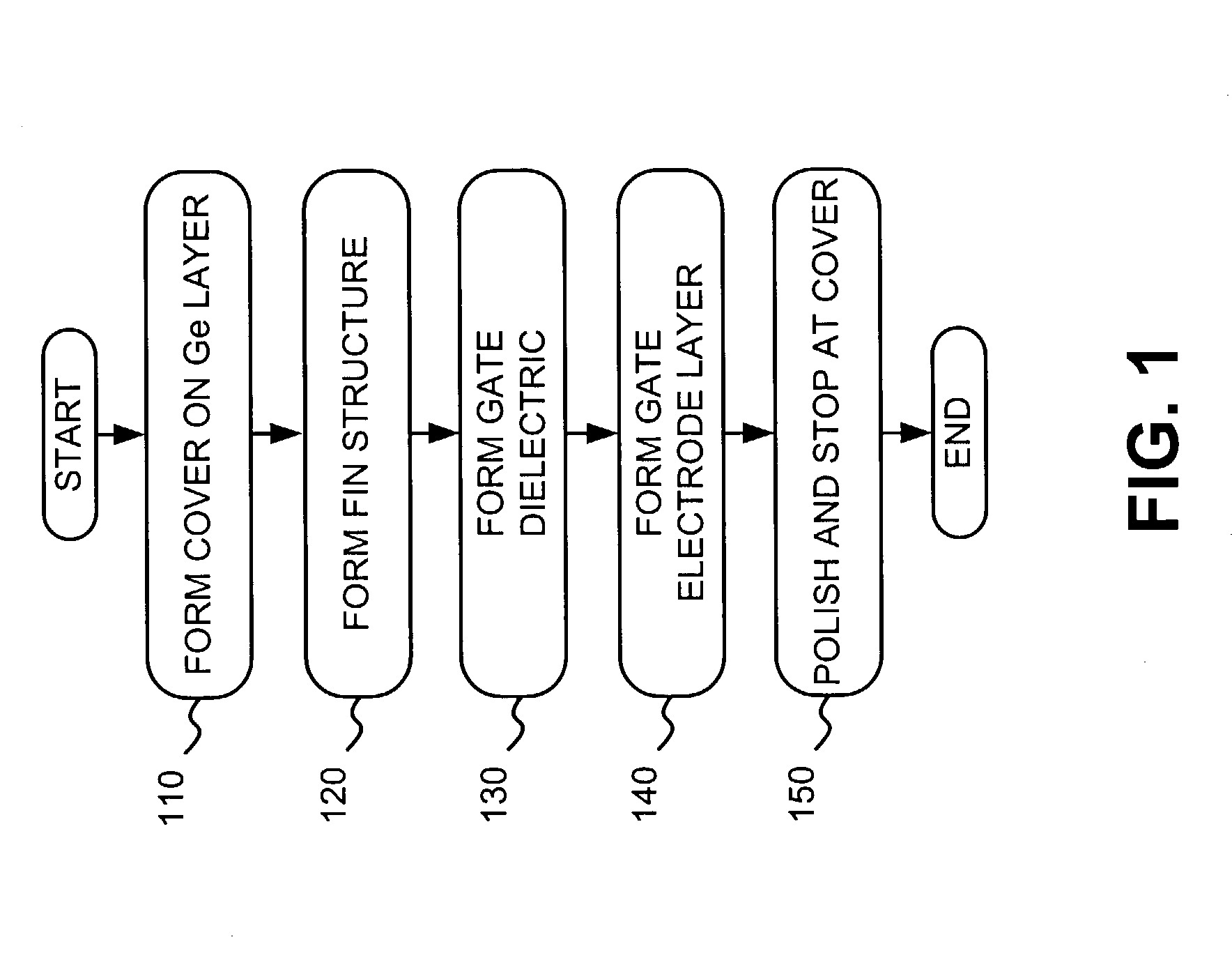

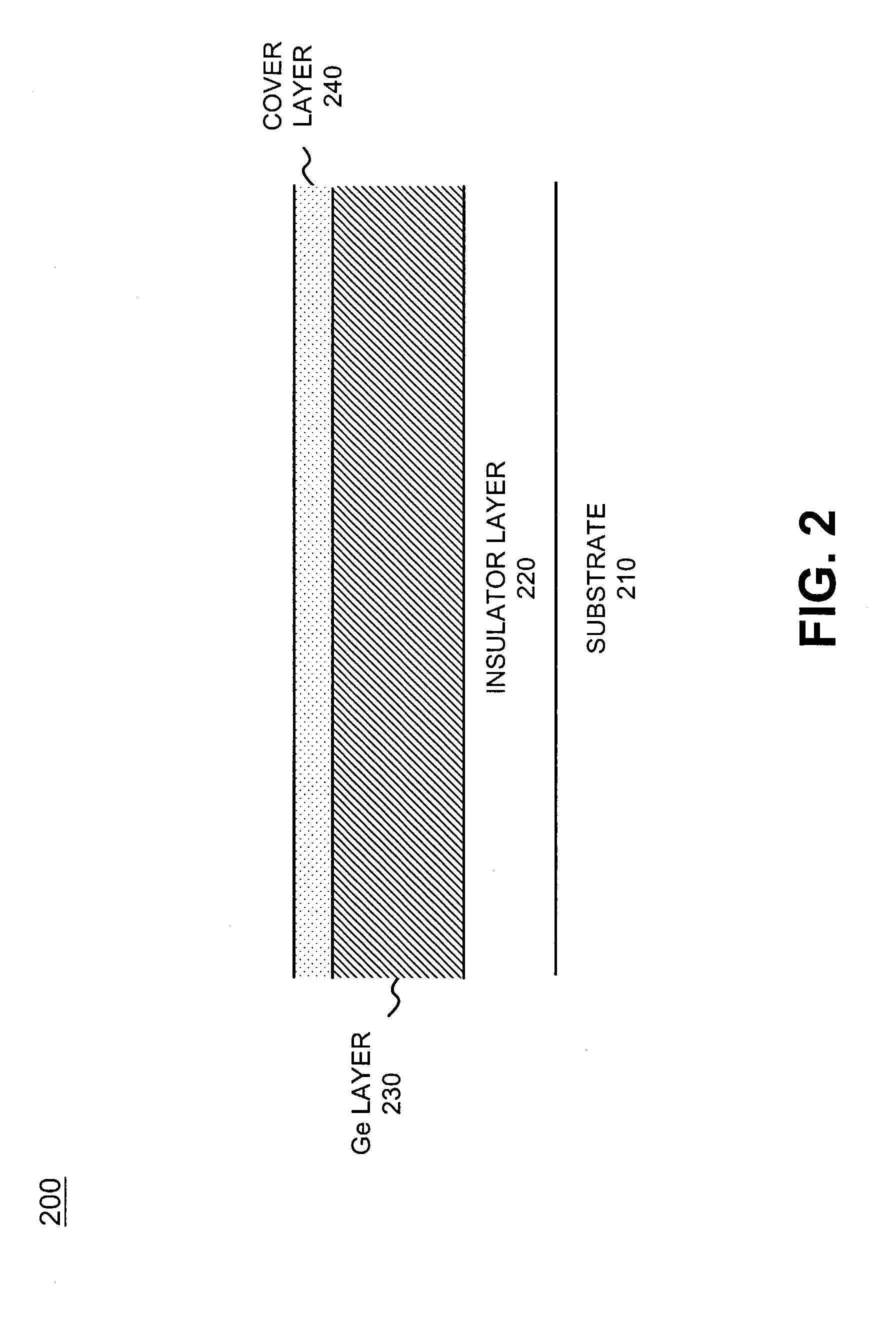

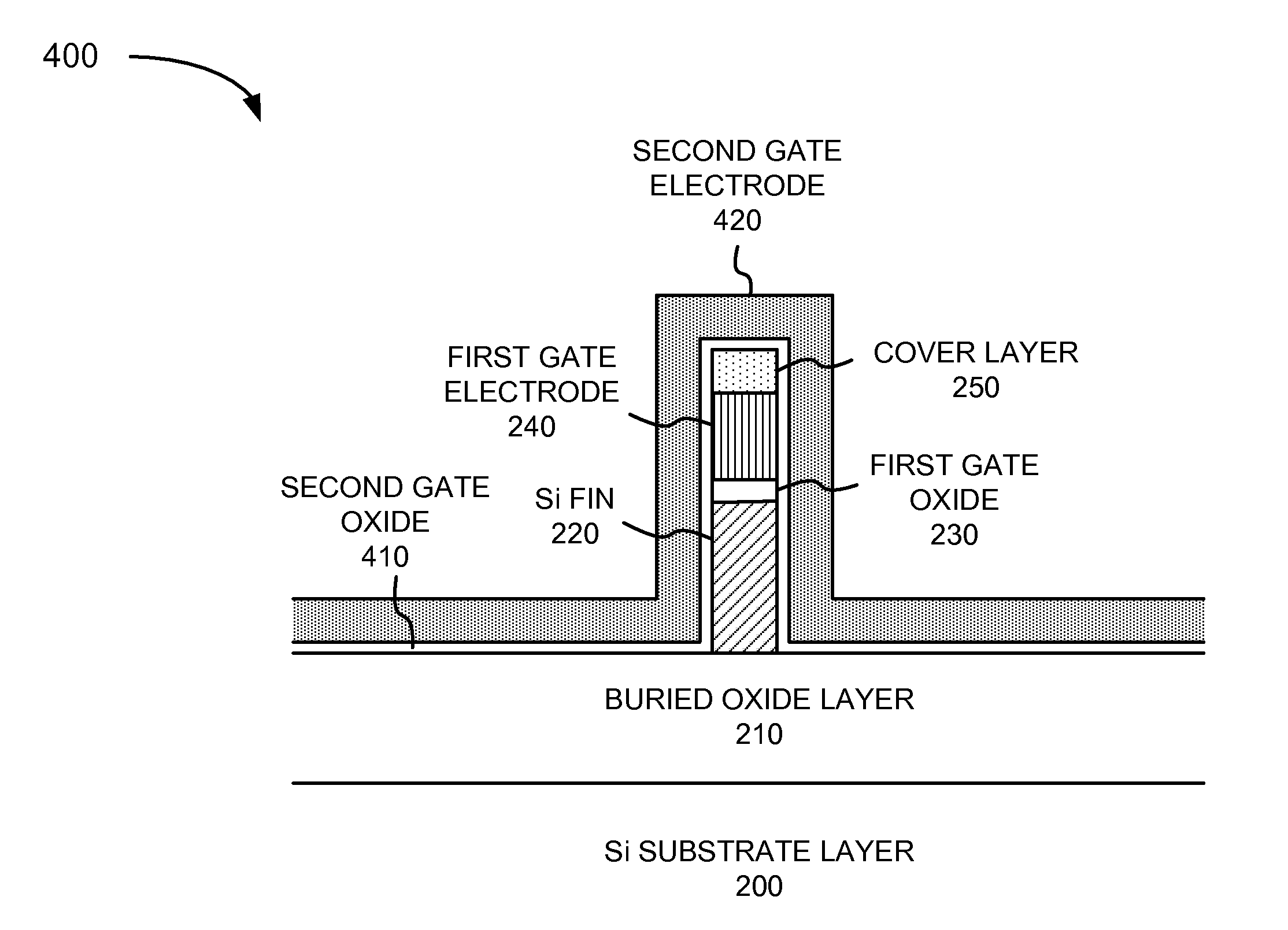

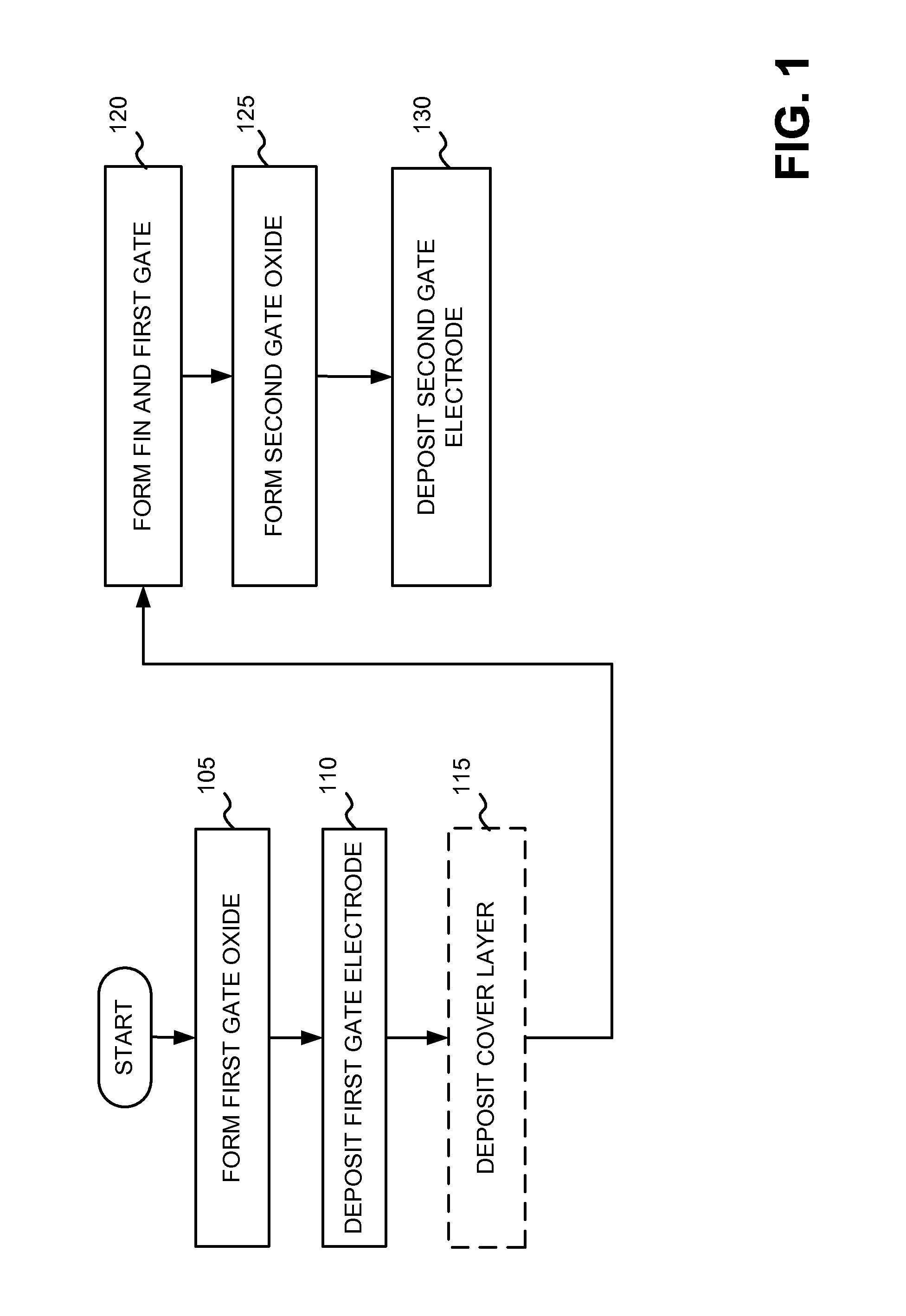

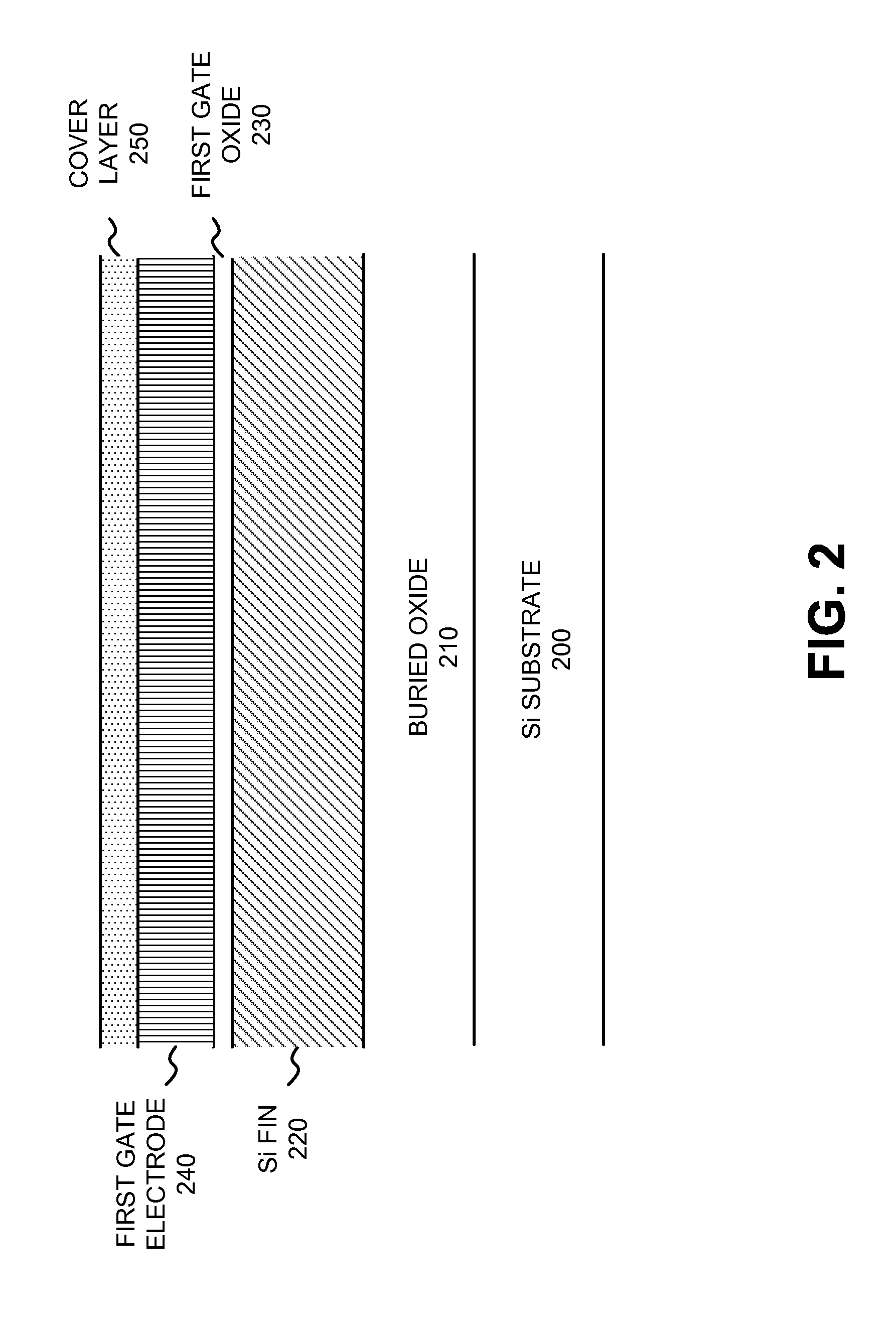

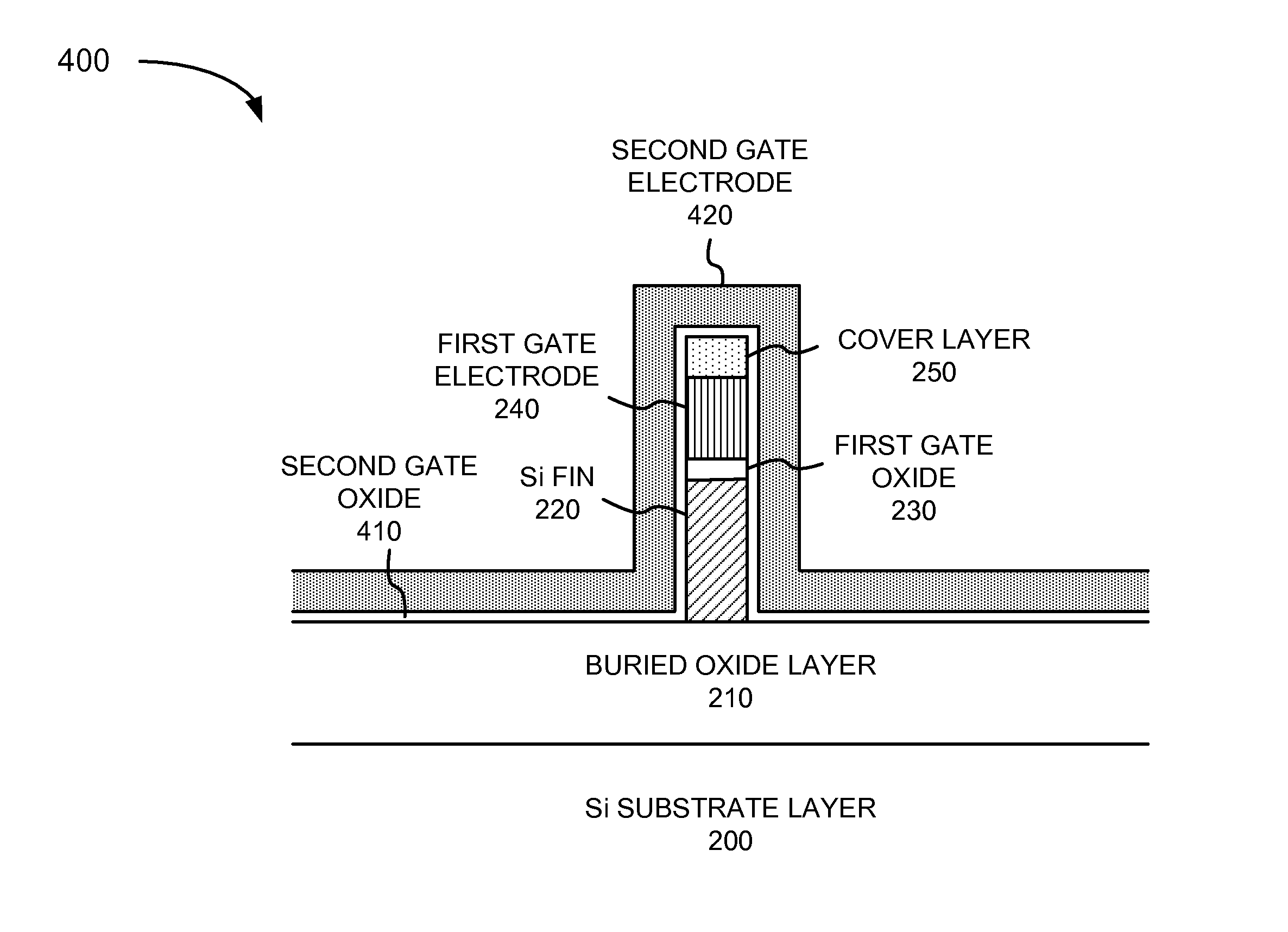

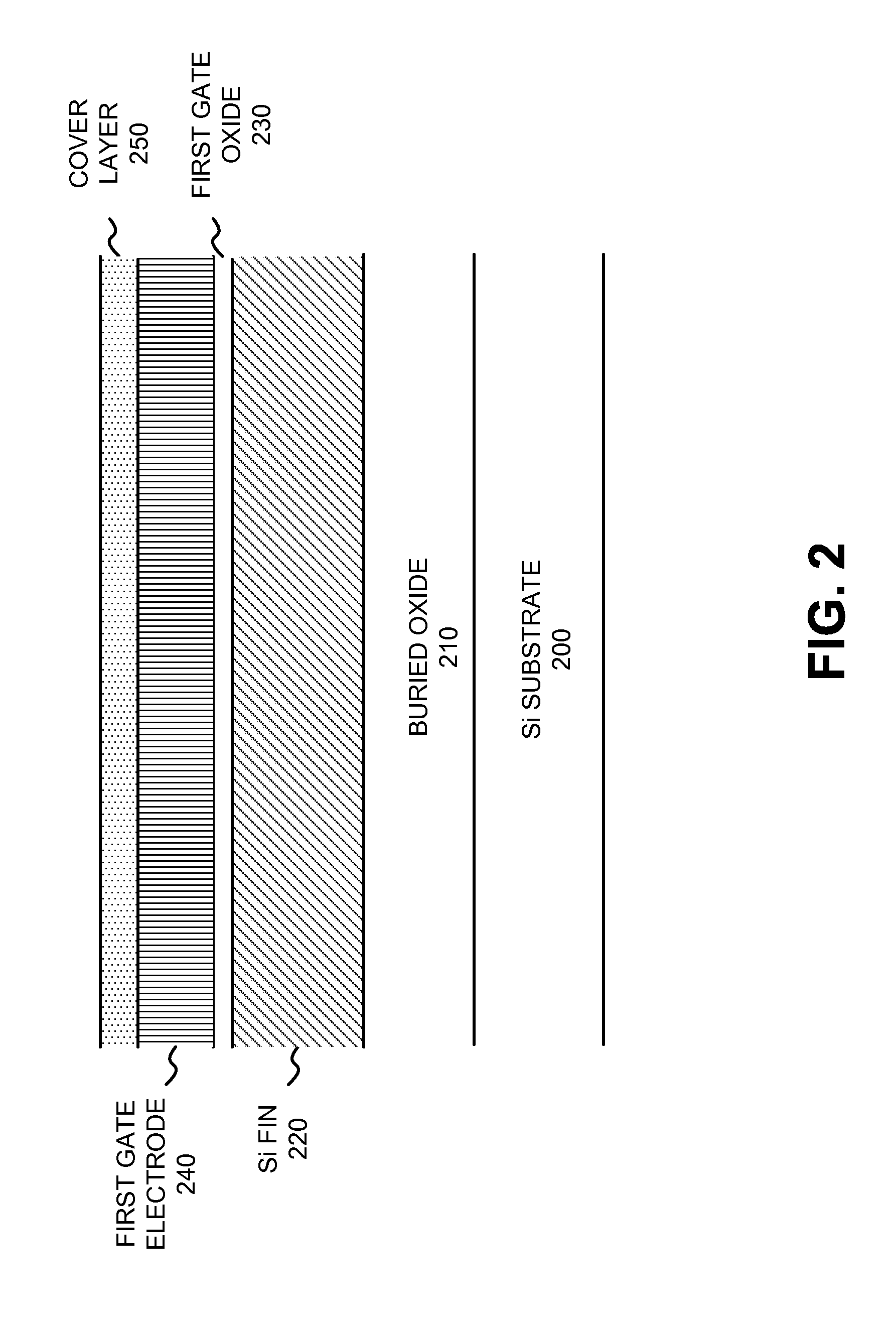

Germanium MOSFET devices and methods for making same

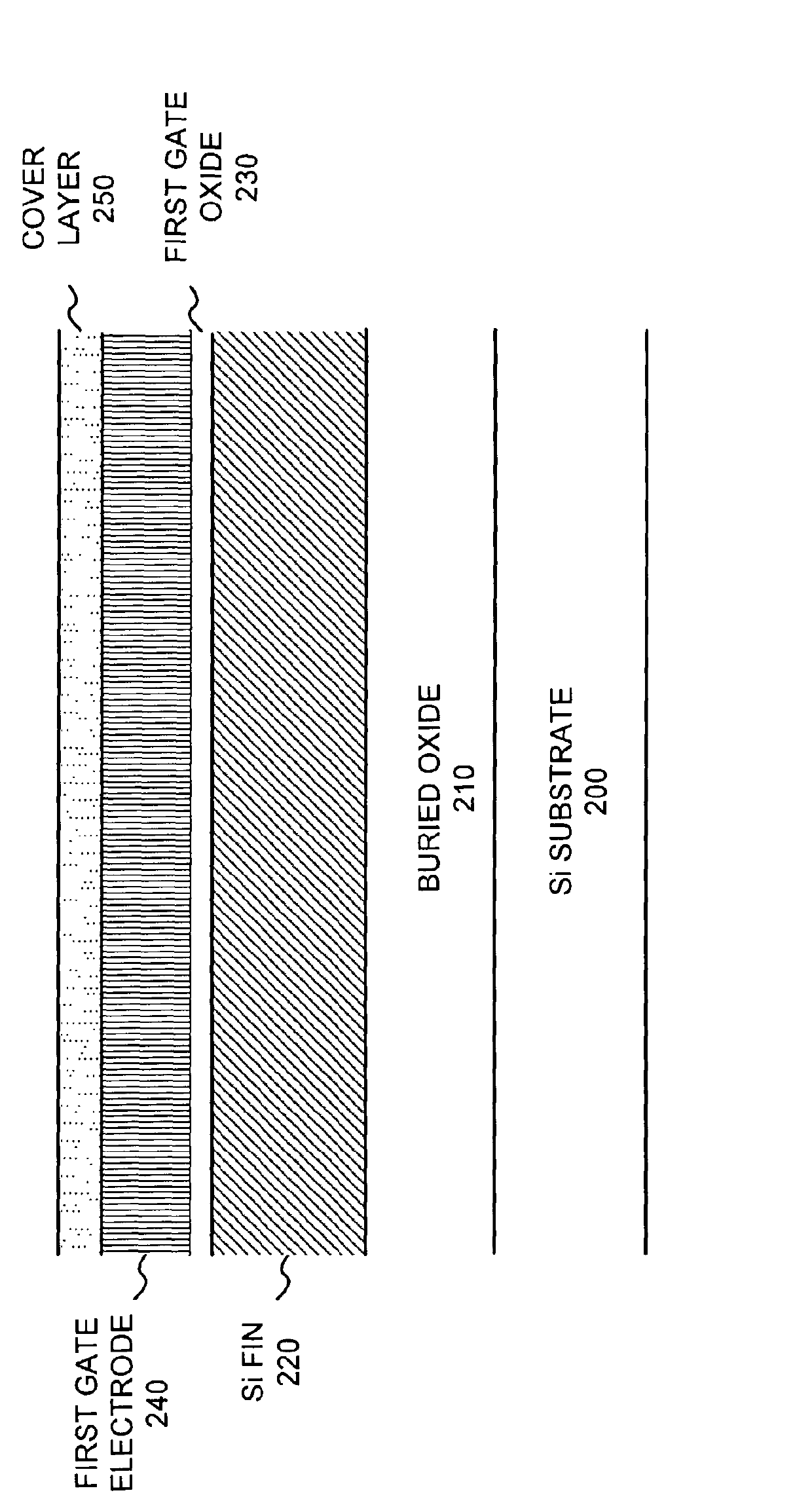

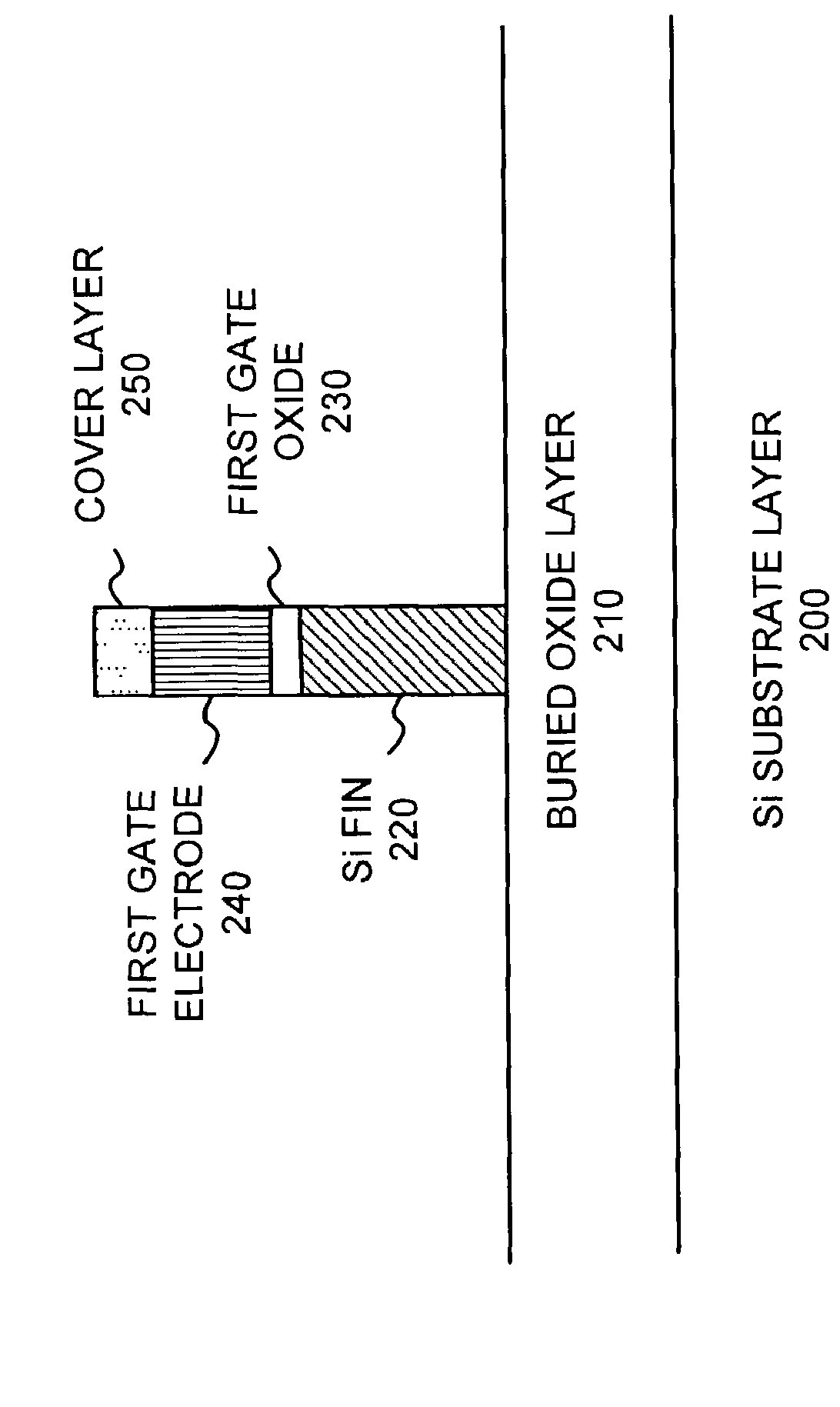

A double gate germanium metal-oxide semiconductor field-effect transistor (MOSFET) includes a germanium fin, a first gate formed adjacent a first side of the germanium fin, and a second gate formed adjacent a second side of the germanium fin opposite the first side. A triple gate MOSFET includes a germanium fin, a first gate formed adjacent a first side of the germanium fin, a second gate formed adjacent a second side of the germanium fin opposite the first side, and a top gate formed on top of the germanium fin. An all-around gate MOSFET includes a germanium fin, a first sidewall gate structure formed adjacent a first side of the germanium fin, a second sidewall gate structure formed adjacent a second side of the germanium fin, and additional gate structures formed on and around the germanium fin.

Owner:ADVANCED MICRO DEVICES INC

Complementary carbon nanotube triple gate technology

InactiveUS7492015B2Facilitate conductionMinimizes parasitic capacitanceTransistorNanoinformaticsElectrical resistance and conductanceParasitic capacitance

Disclosed is a CNT technology that overcomes the intrinsic ambipolar properties of CNTFETs. One embodiment of the invention provides either a stable p-type CNTFET or a stable n-type CNTFET. Another embodiment of the invention provides a complementary CNT device. In order to overcome the ambipolar properties of a CNTFET, source / drain gates are introduced below the CNT opposite the source / drain electrodes. These source / drain gates are used to apply either a positive or negative voltage to the ends of the CNT so as to configure the corresponding FET as either an n-type or p-type CNTFET, respectively. Two adjacent CNTFETs, configured such that one is an n-type CNTFET and the other is a p-type CNTFET, can be incorporated into a complementary CNT device. In order to independently adjust threshold voltage of an individual CNTFET, a back gate can also be introduced below the CNT and, particularly, below the channel region of the CNT opposite the front gate. In this manner parasitic capacitances and resistances are minimized.

Owner:GLOBALFOUNDRIES INC

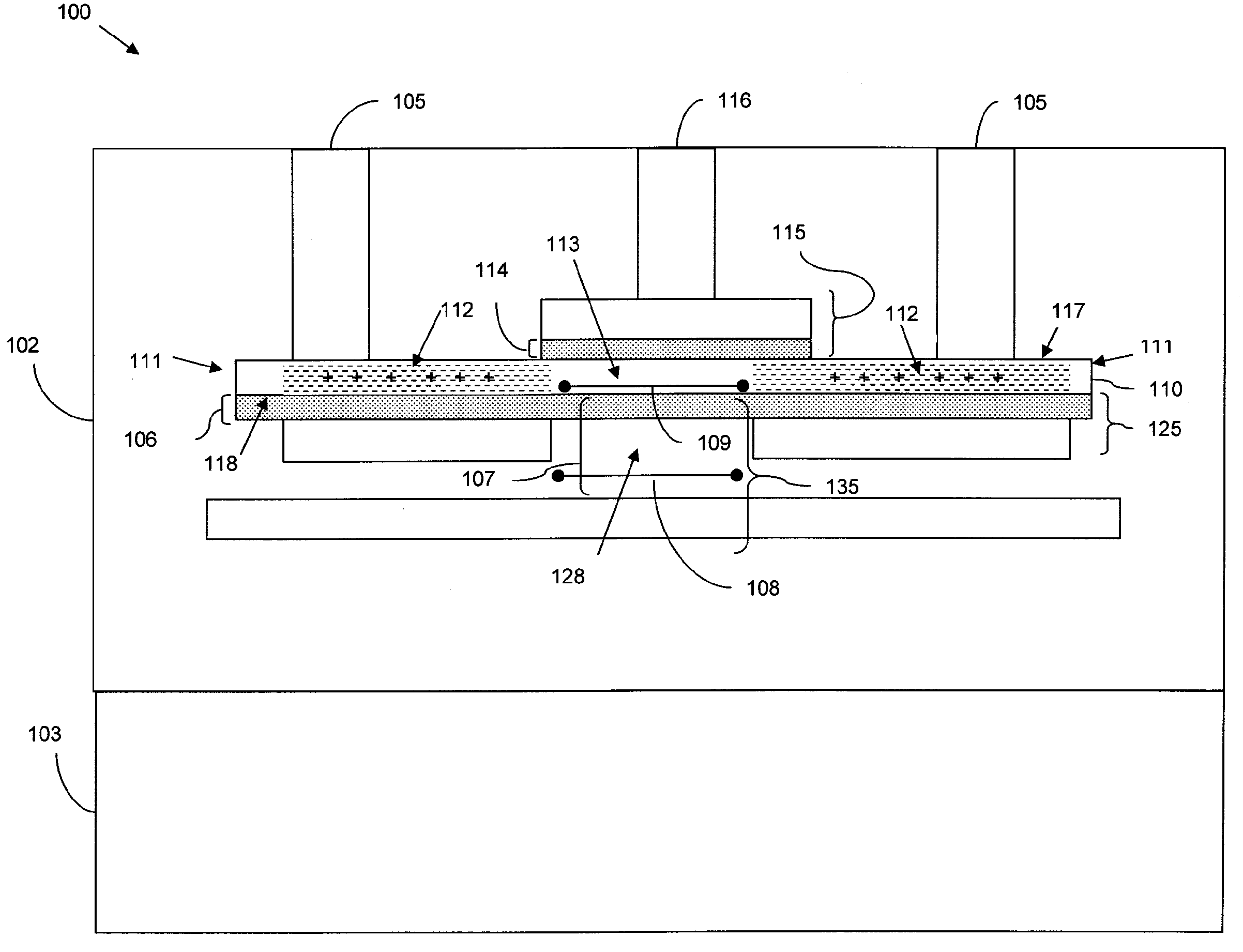

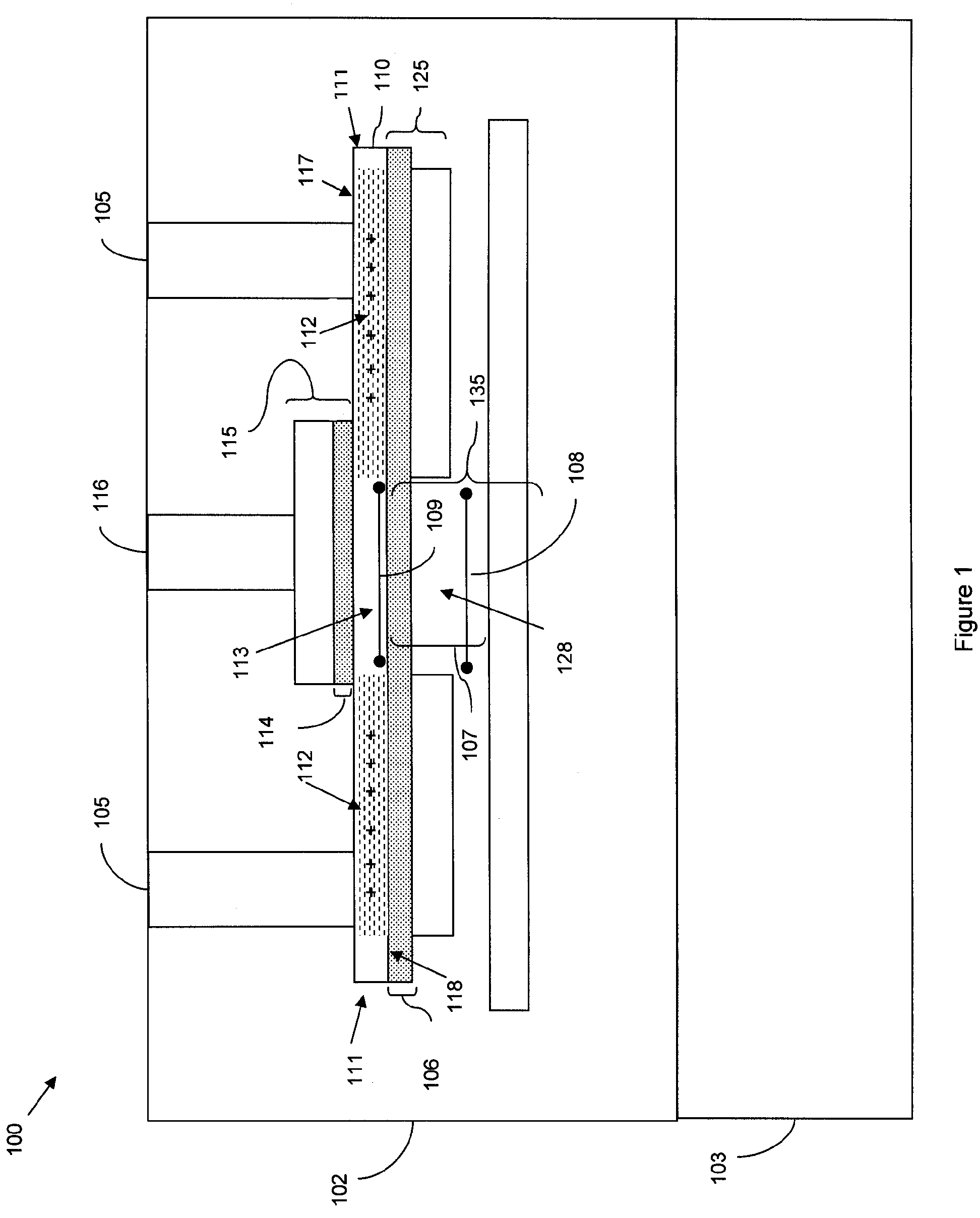

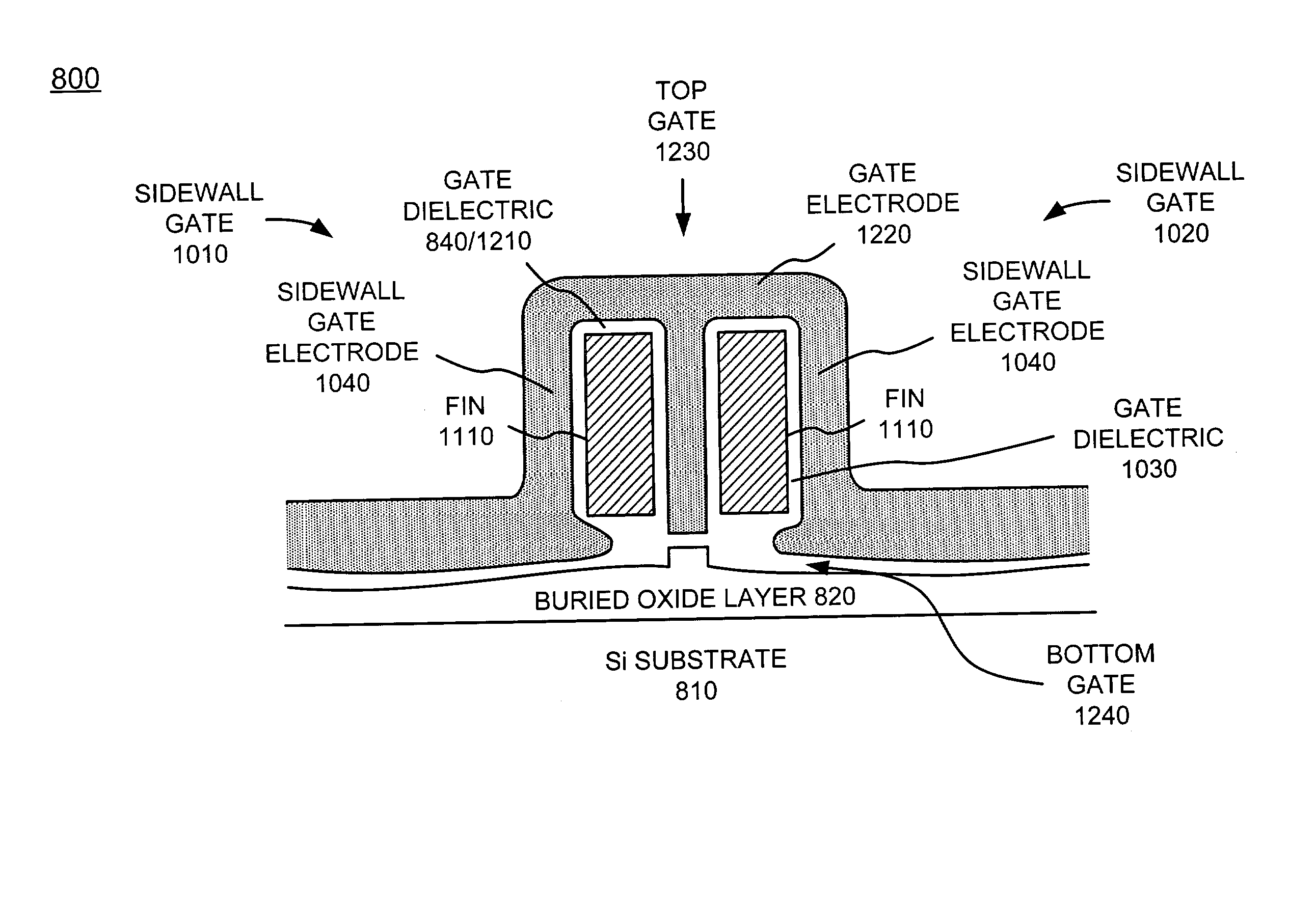

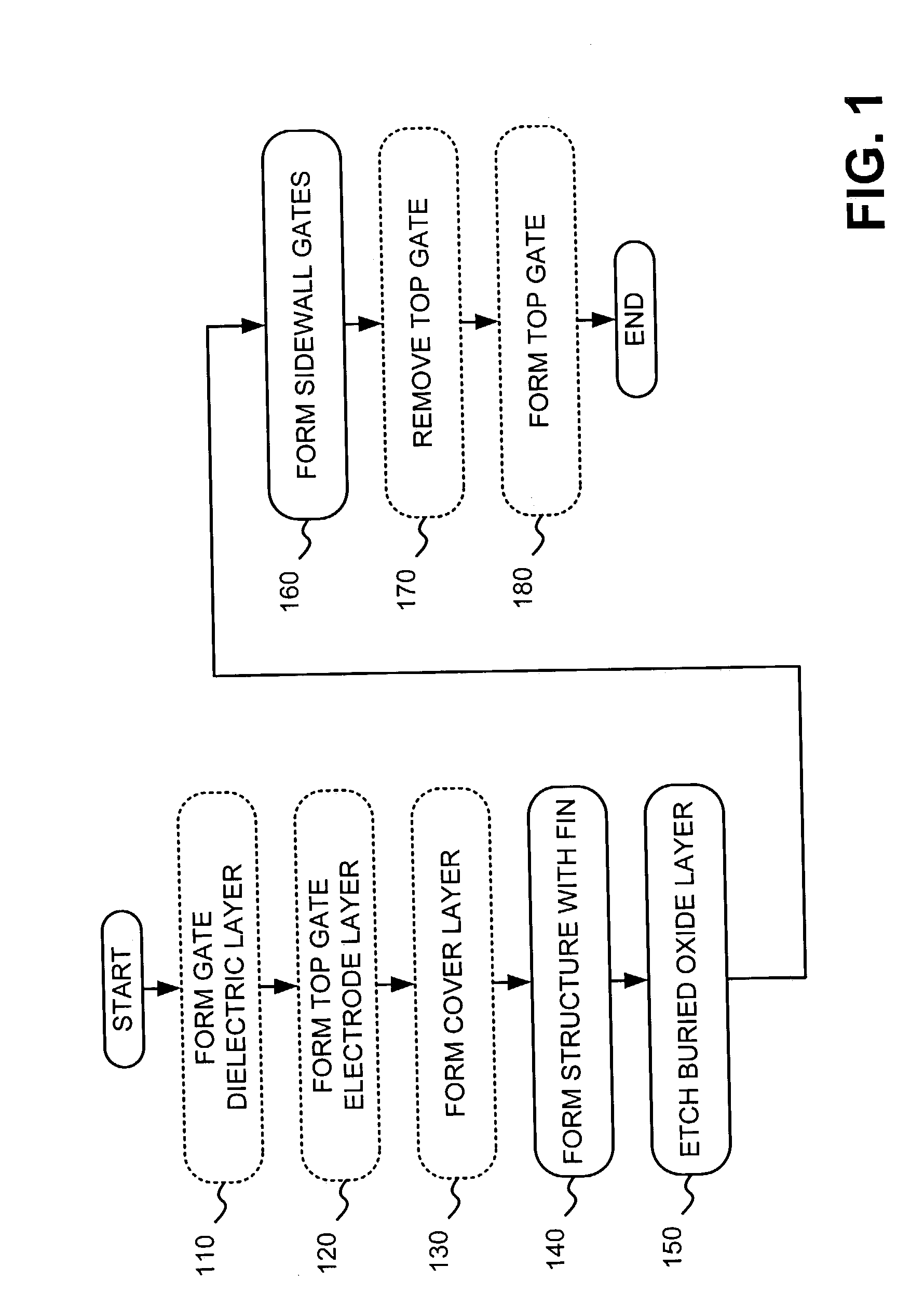

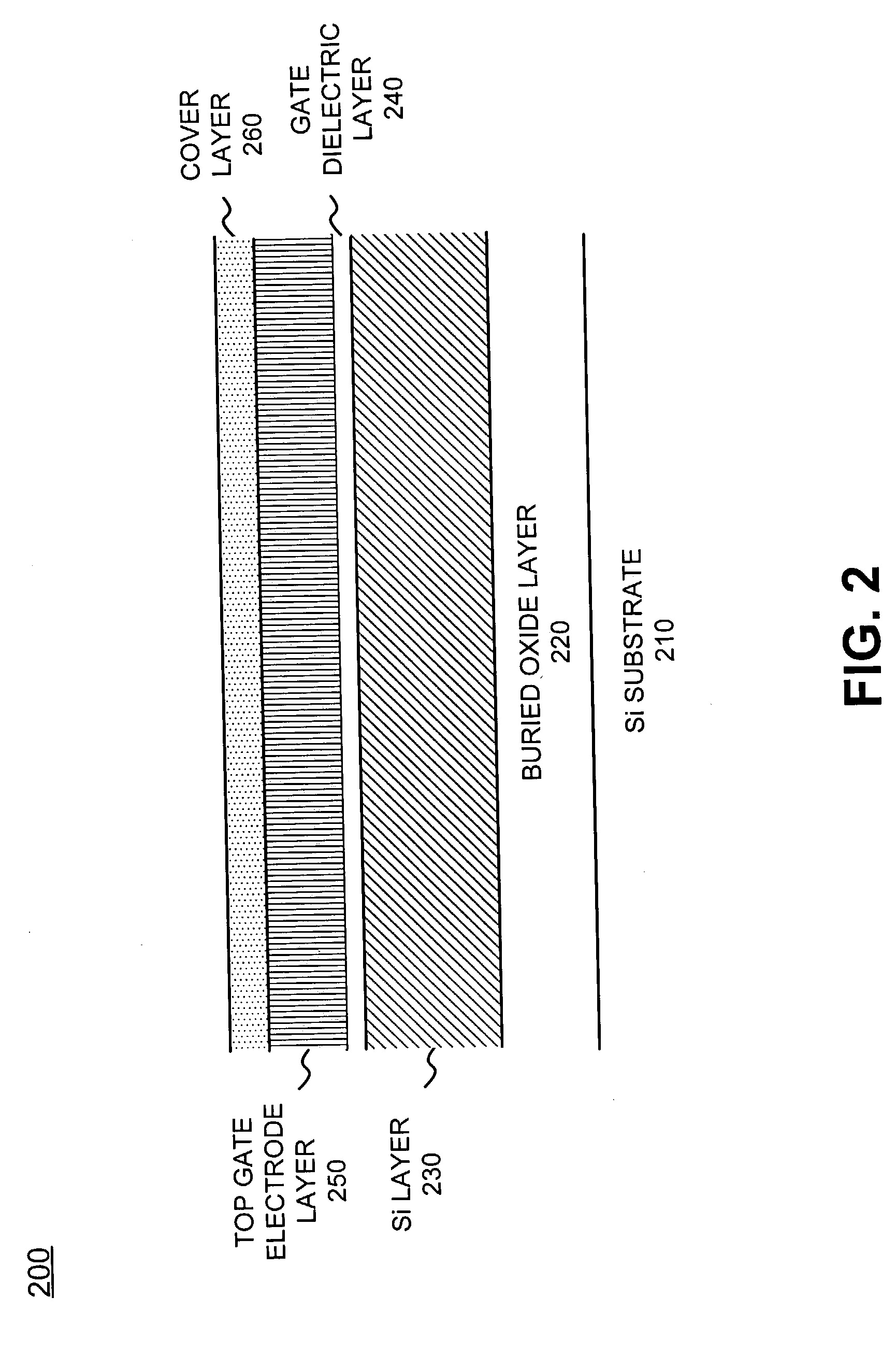

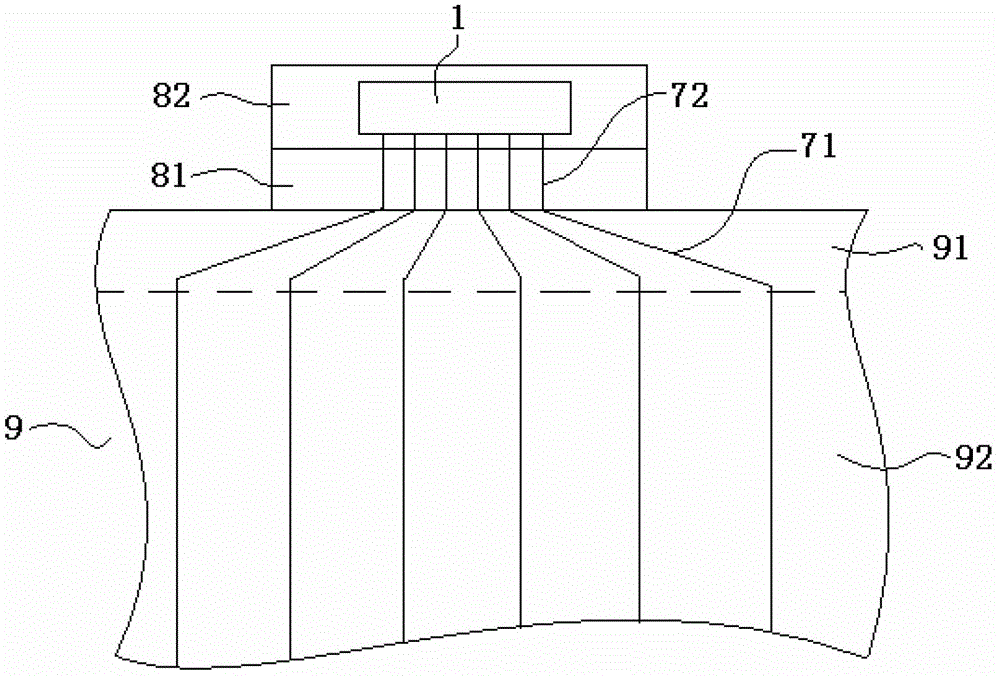

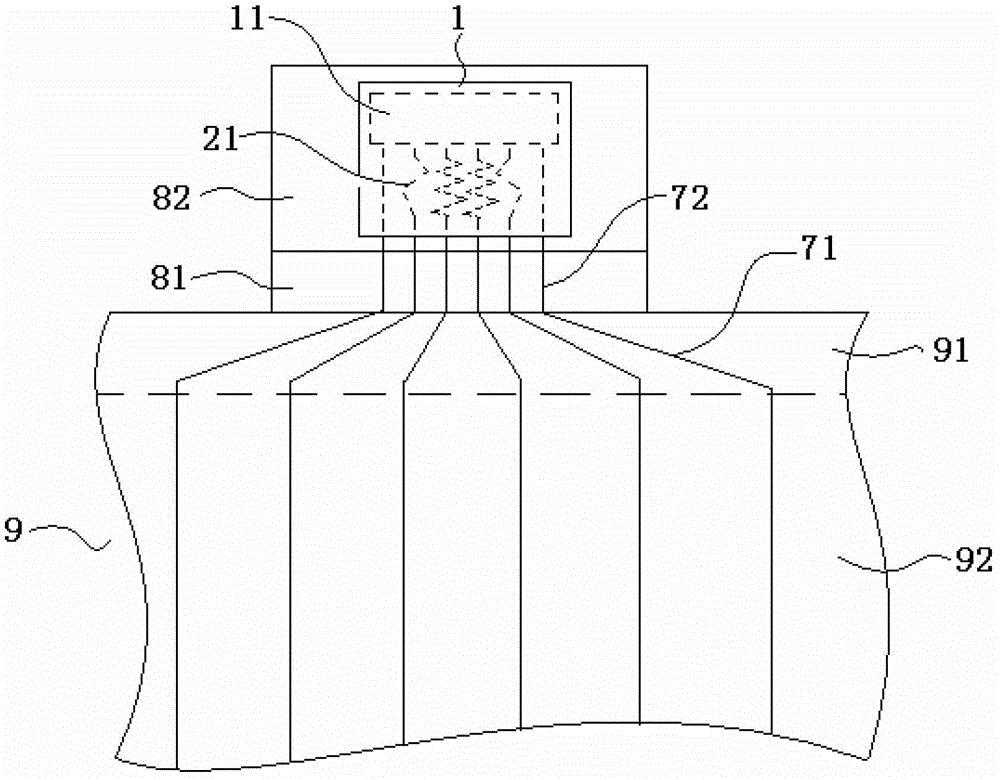

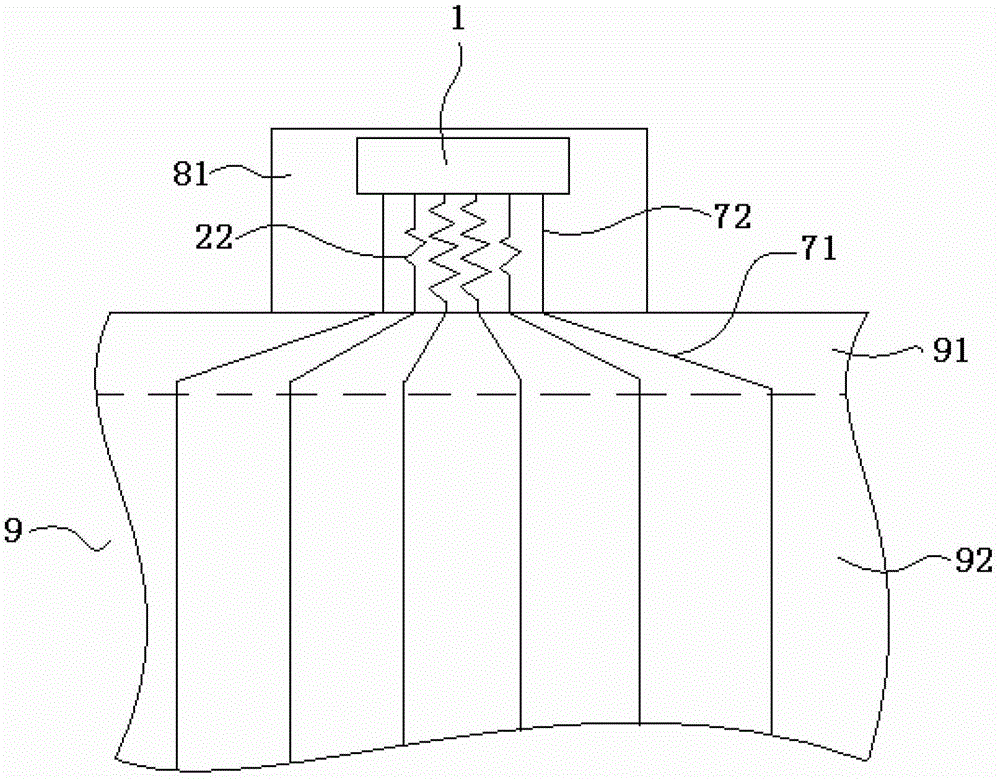

Tri-gate and gate around MOSFET devices and methods for making same

A triple gate metal-oxide semiconductor field-effect transistor (MOSFET) includes a fin structure, a first gate formed adjacent a first side of the fin structure, a second gate formed adjacent a second side of the fin structure opposite the first side, and a top gate formed on top of the fin structure. A gate around MOSFET includes multiple fins, a first sidewall gate structure formed adjacent one of the fins, a second sidewall gate structure formed adjacent another one of the fins, a top gate structure formed on one or more of the fins, and a bottom gate structure formed under one or more of the fins.

Owner:ADVANCED MICRO DEVICES INC

Display drive chip, display drive chip assembly and display device

InactiveCN103337233AAchieve narrow bezel designReduce or eliminate impedance mismatchStatic indicating devicesNon-linear opticsLED displayDisplay device

The invention provides a display drive chip, a display drive chip assembly and a display device, belongs to the field of the display technology, and can solve the problem, caused by unmatched impedances, of poor displaying of the conventional display device. The display drive chip provided by the invention comprises a plurality of output ports and a drive circuit, wherein the output port are used for outputting drive signals; the drive circuit is used for generating drive signals and connected with the output ports; a chip impedance matching unit with a certain impedance is arranged between at least one output port and the drive circuit. The invention can be used in a display device adopting an active drive array such as an LCD device and an organic LED display device, is particularly applicable to display devices adopting technologies of narrow frame, dual gate, triple gate and high frequency drive.

Owner:BOE TECH GRP CO LTD +1

Double and triple gate MOSFET devices and methods for making same

A double gate metal-oxide semiconductor field-effect transistor (MOSFET) includes a fin, a first gate and a second gate. The first gate is formed on top of the fin. The second gate surrounds the fin and the first gate. In another implementation, a triple gate MOSFET includes a fin, a first gate, a second gate, and a third gate. The first gate is formed on top of the fin. The second gate is formed adjacent the fin. The third gate is formed adjacent the fin and opposite the second gate.

Owner:ADVANCED MICRO DEVICES INC

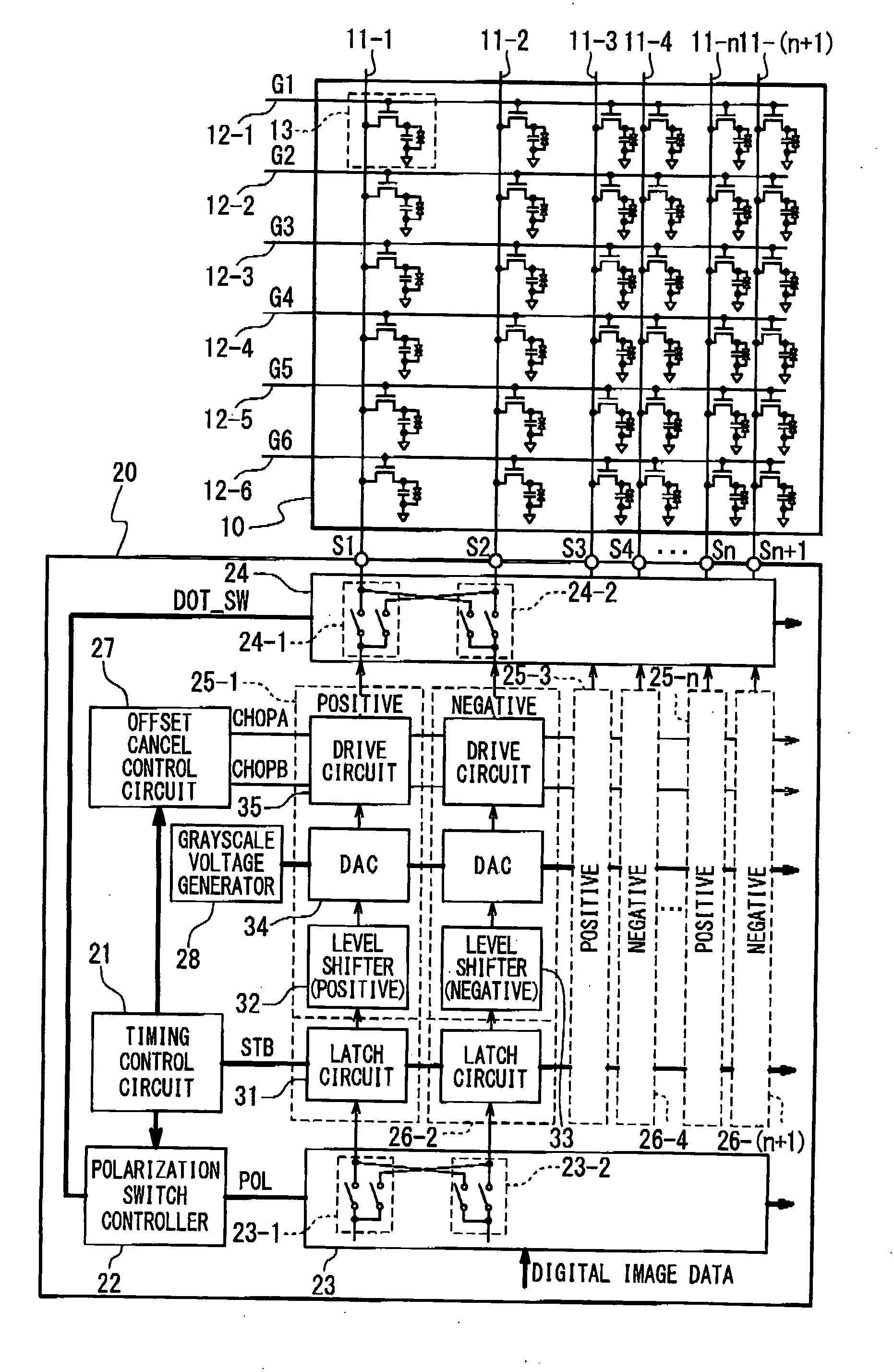

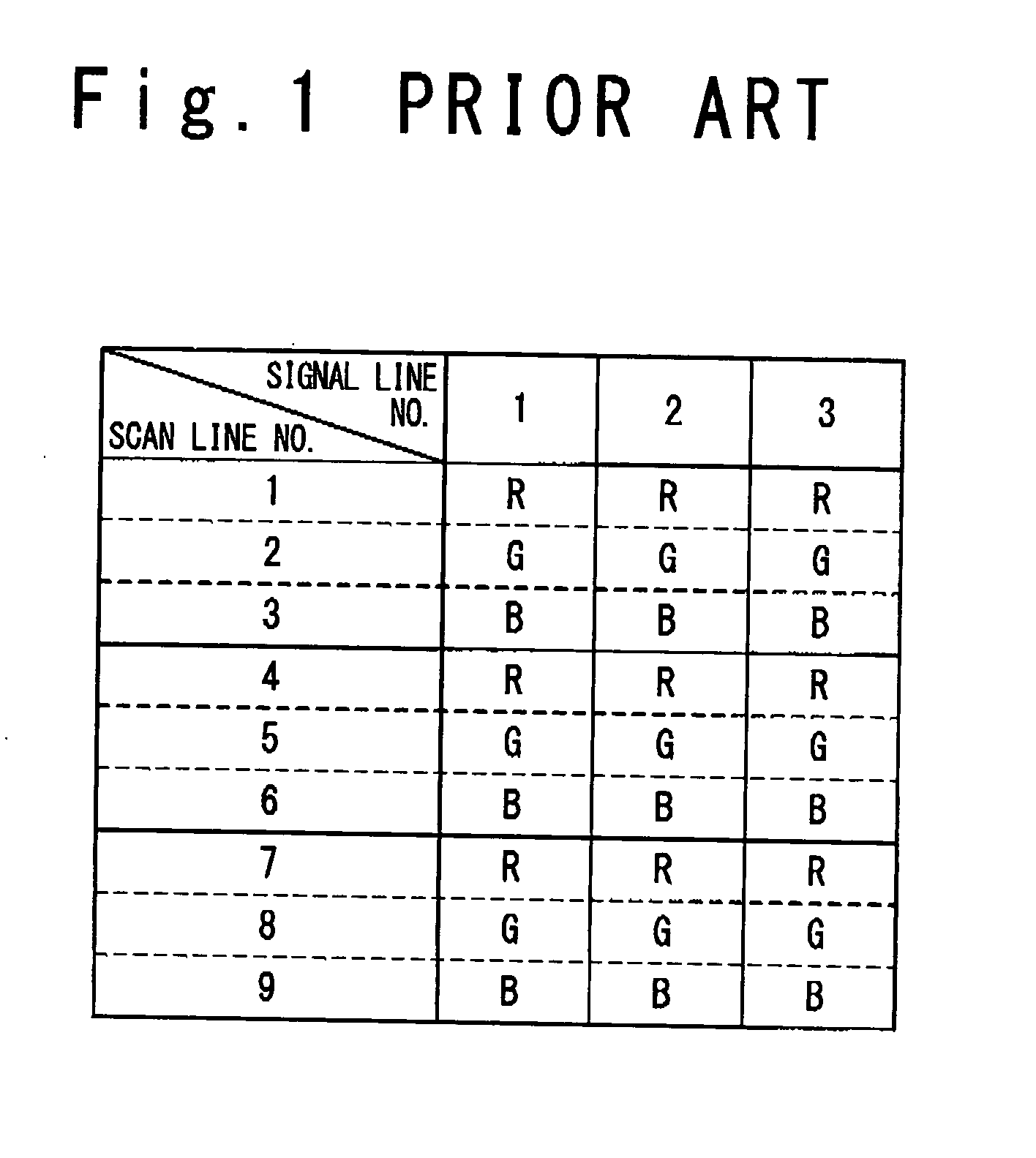

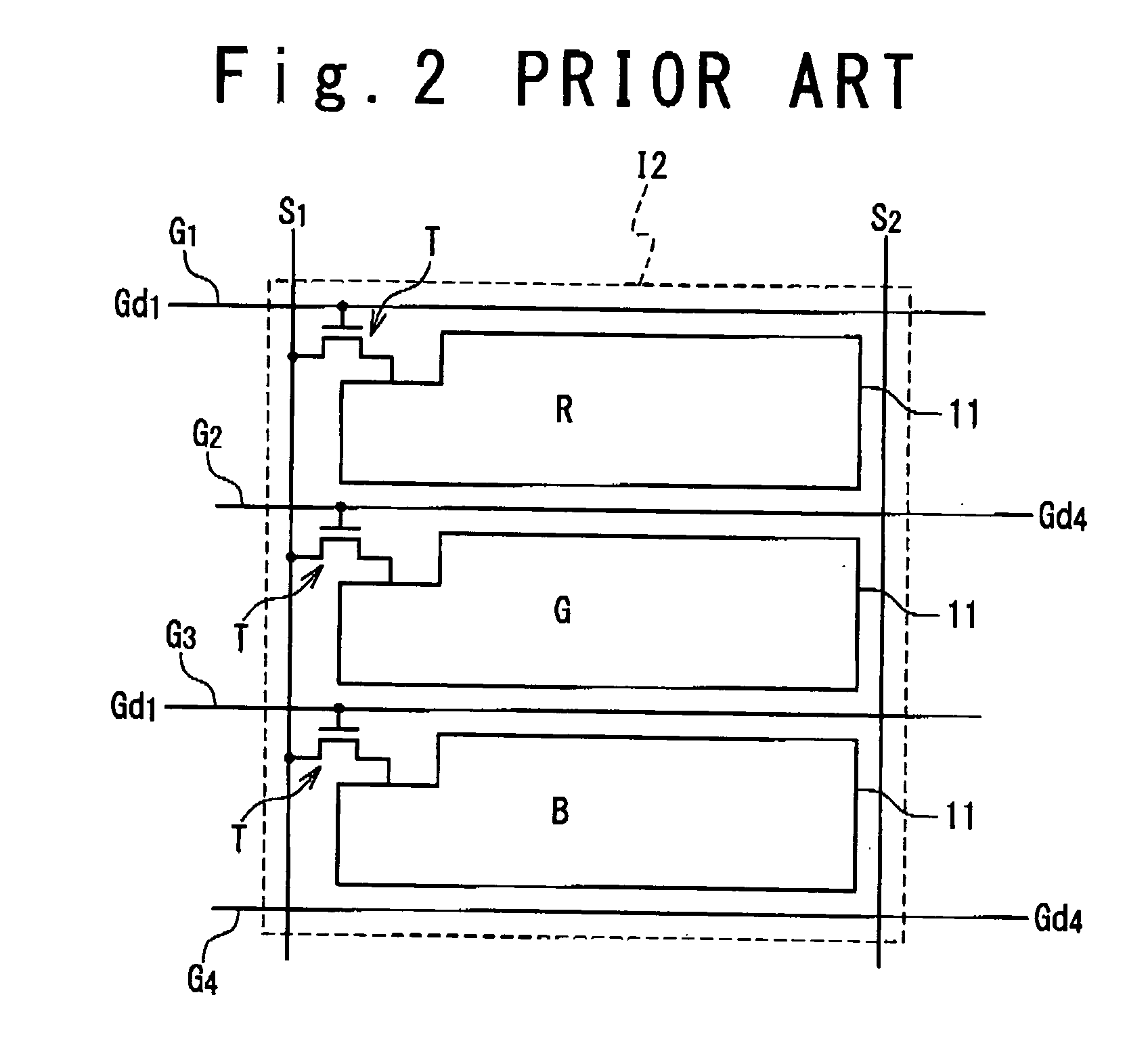

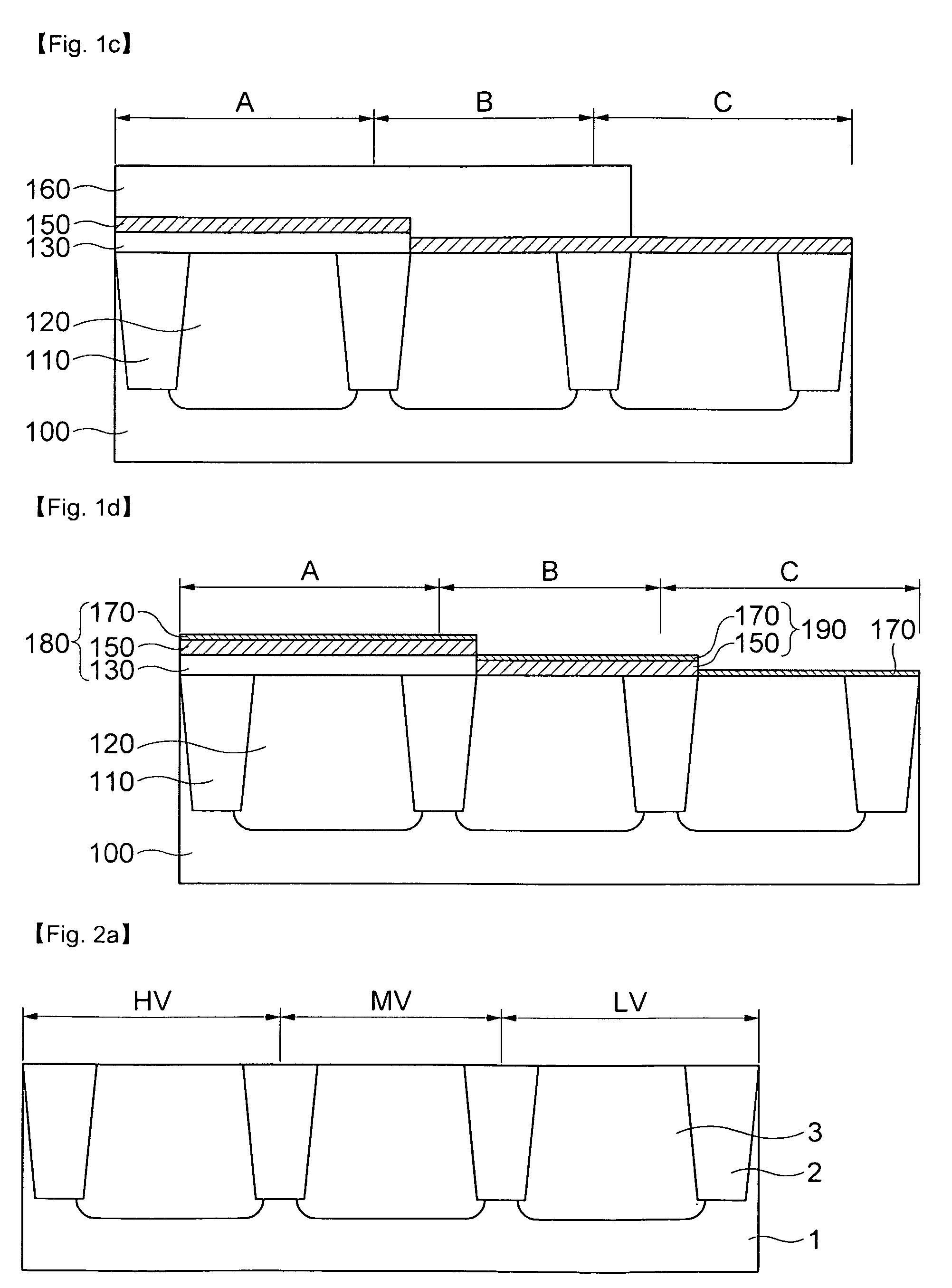

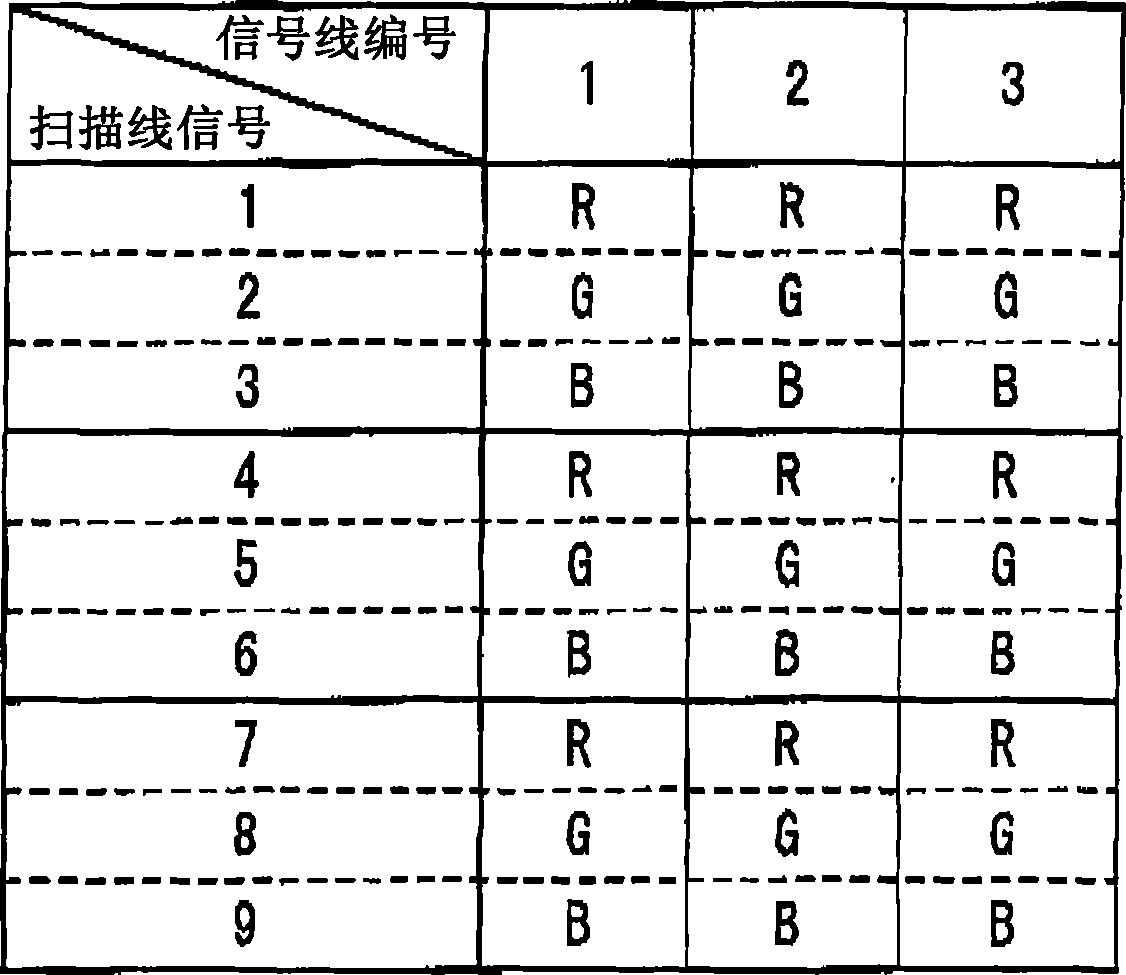

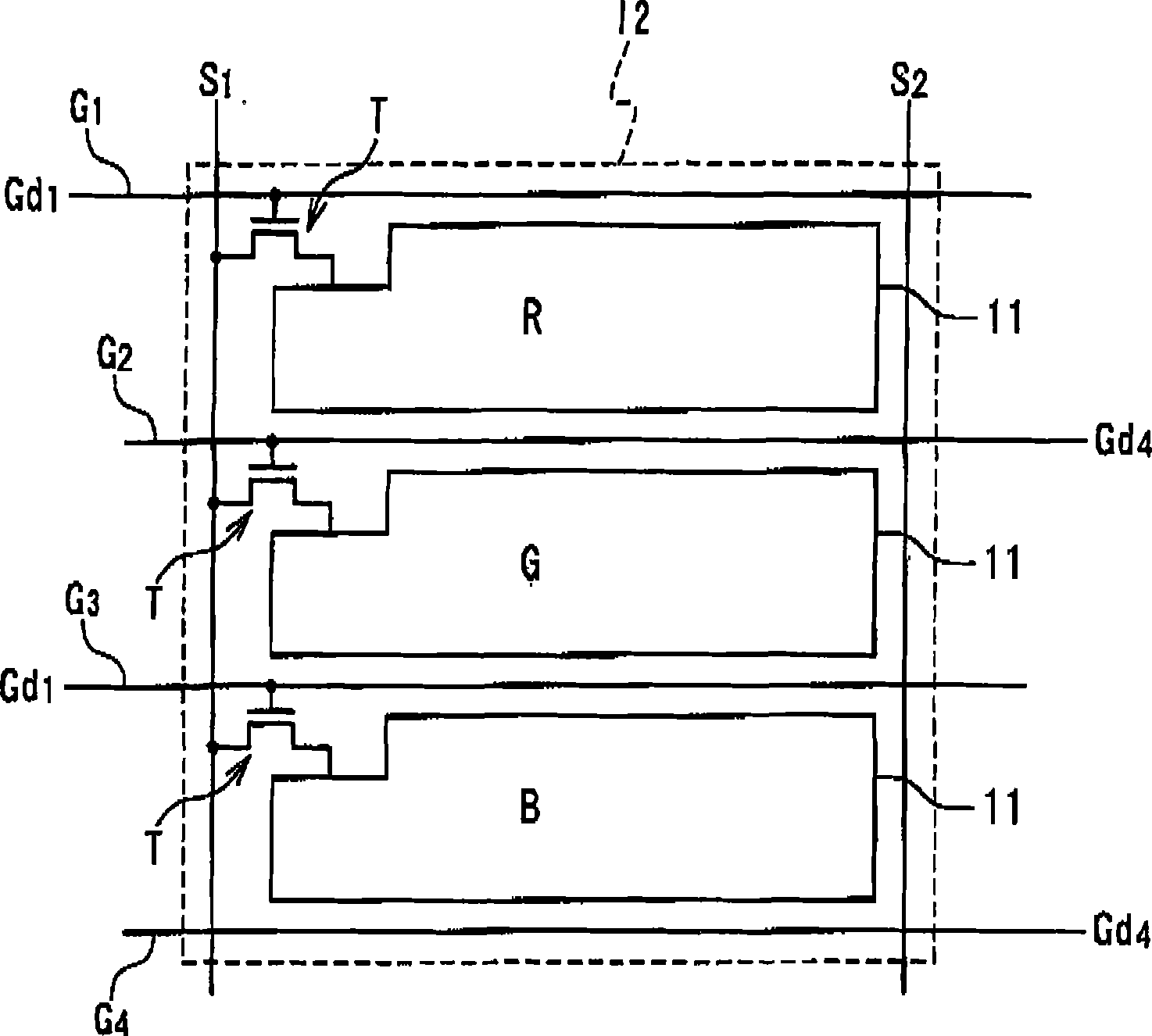

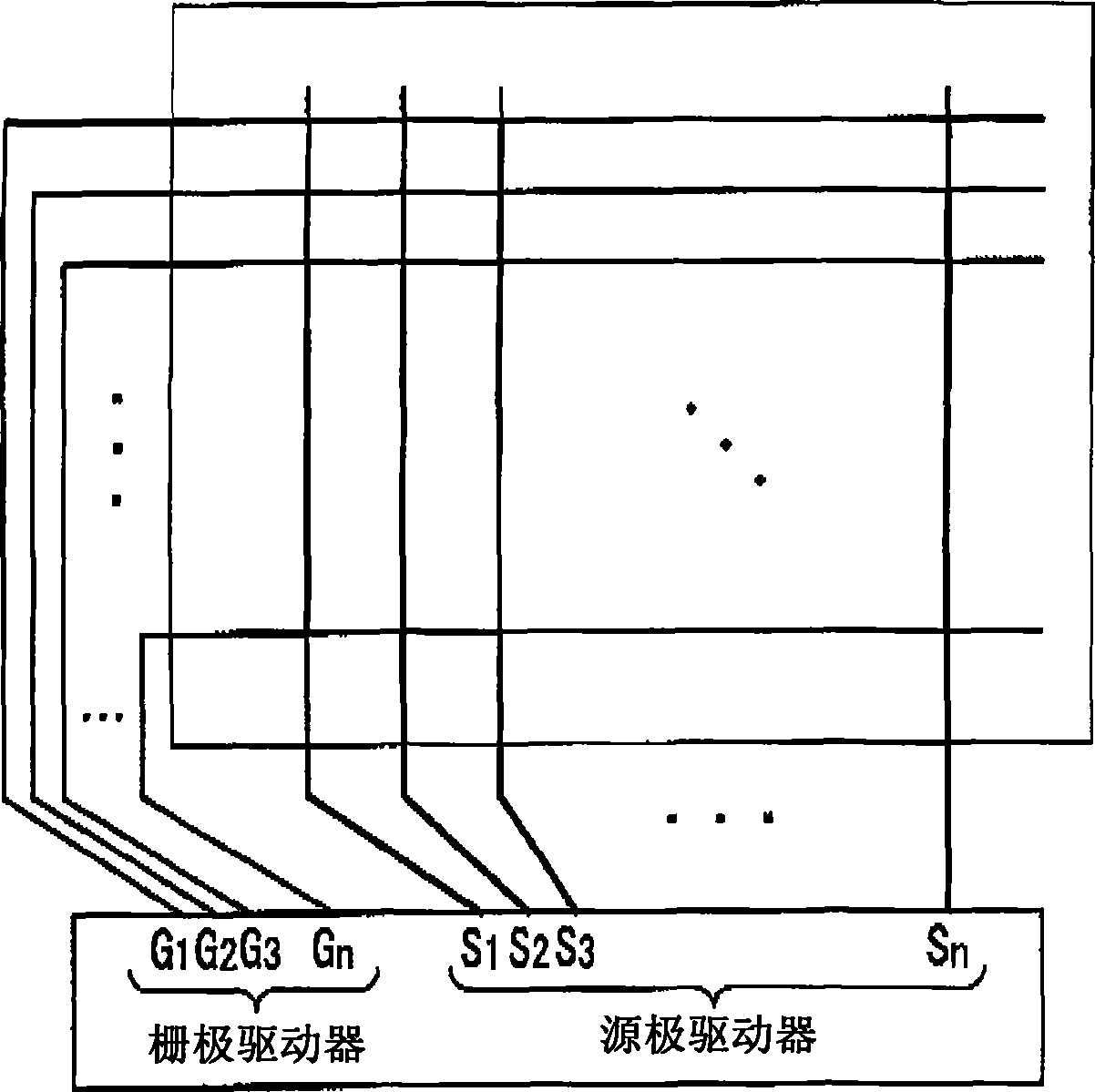

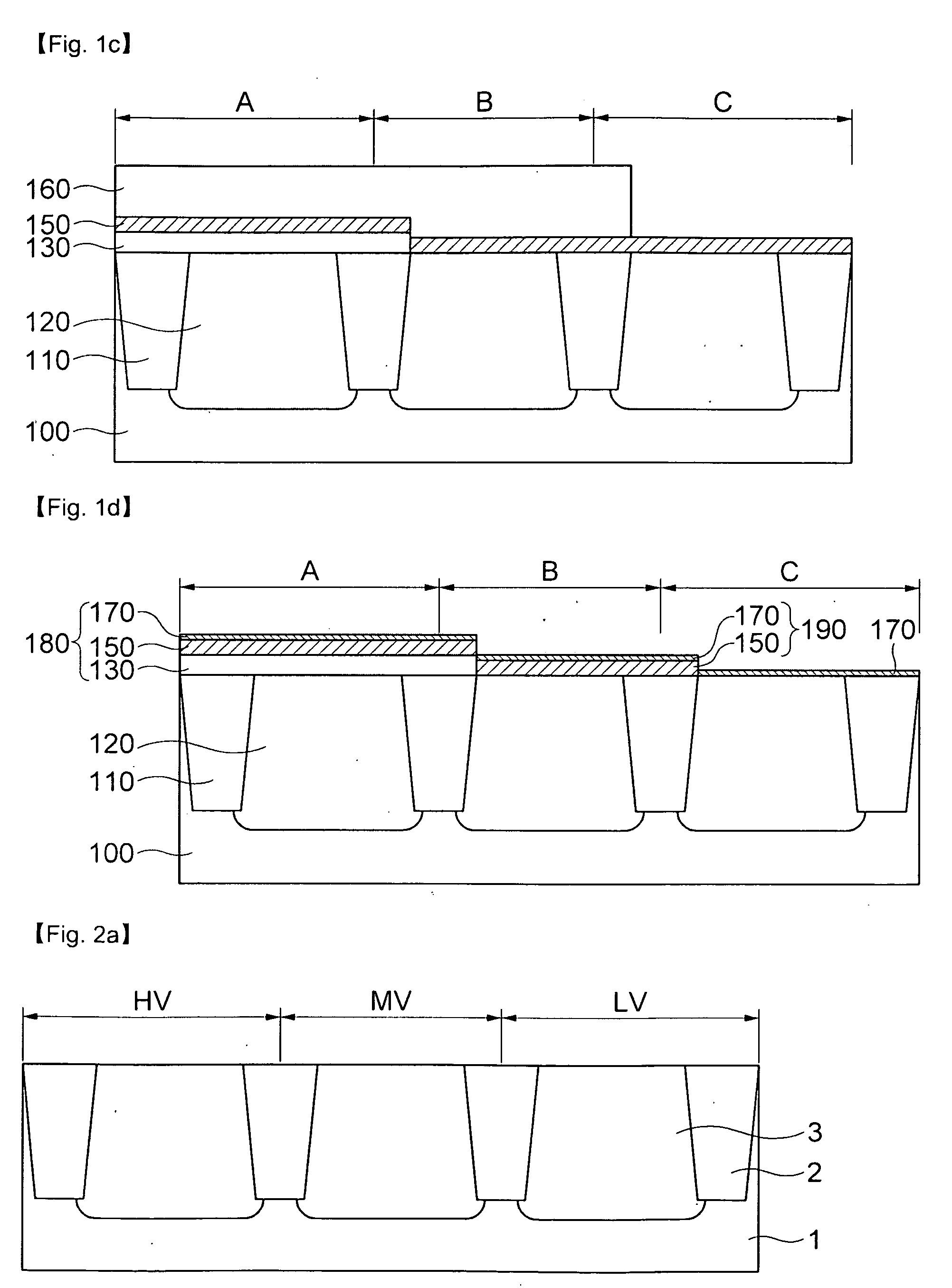

Method for driving liquid crystal display panel with triple gate arrangement

InactiveUS20090102777A1Static indicating devicesNon-linear opticsAudio power amplifierLiquid-crystal display

A method is provided for driving a liquid crystal display panel in which each pixel includes a plurality of sub-pixels arranged in a specific direction, the method including feeding drive voltages to sub-pixels within the liquid crystal display panel by using operational amplifiers. The polarities of the drive voltages fed to each of the sub-pixels are inverted between two adjacent frame periods. The offset polarities of the operational amplifiers are inverted for every a predetermined number of successive sub-pixels. The number of the sub-pixels within each pixel is coprime to the predetermined number of successive sub-pixels.

Owner:RENESAS ELECTRONICS CORP

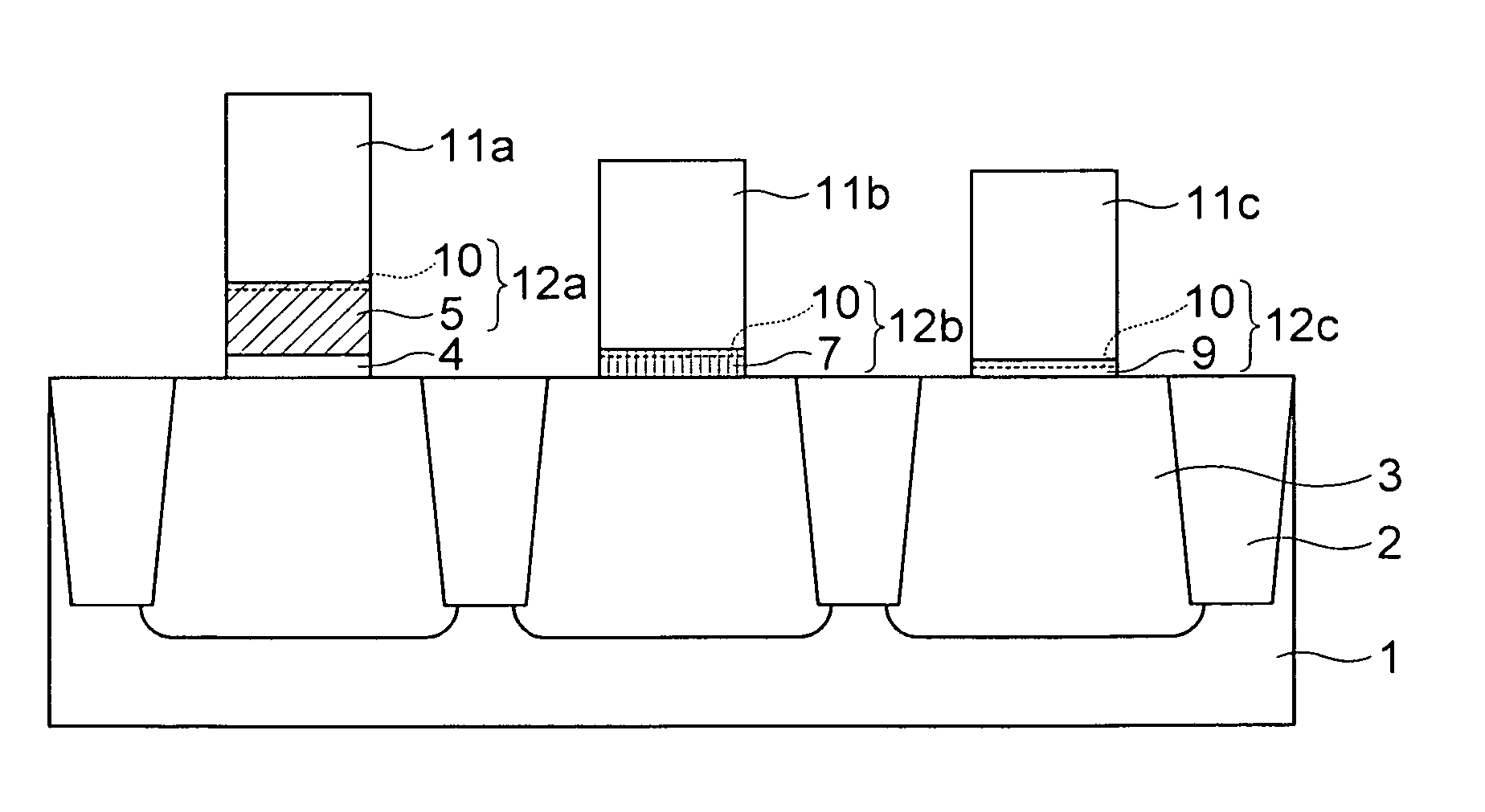

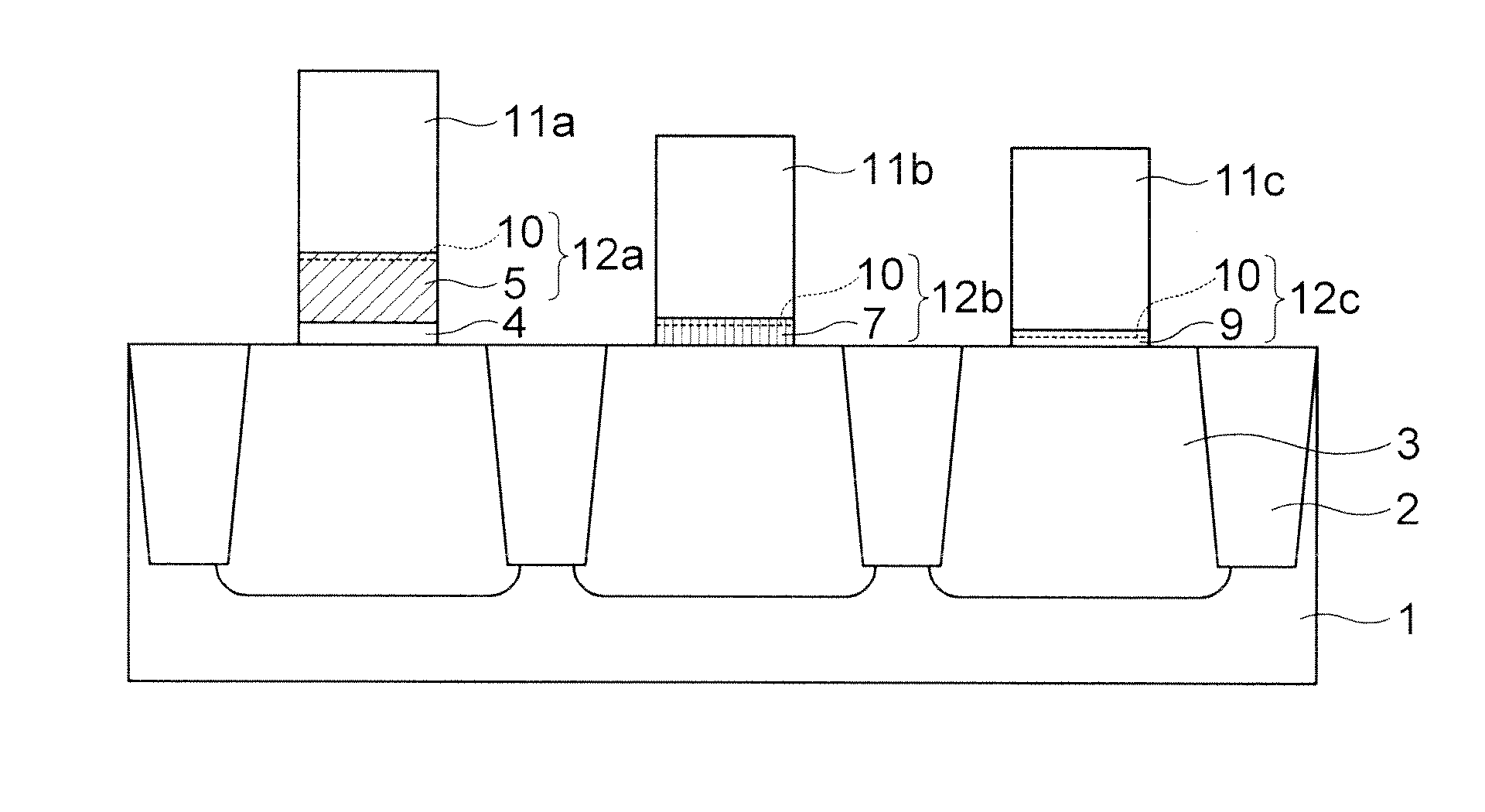

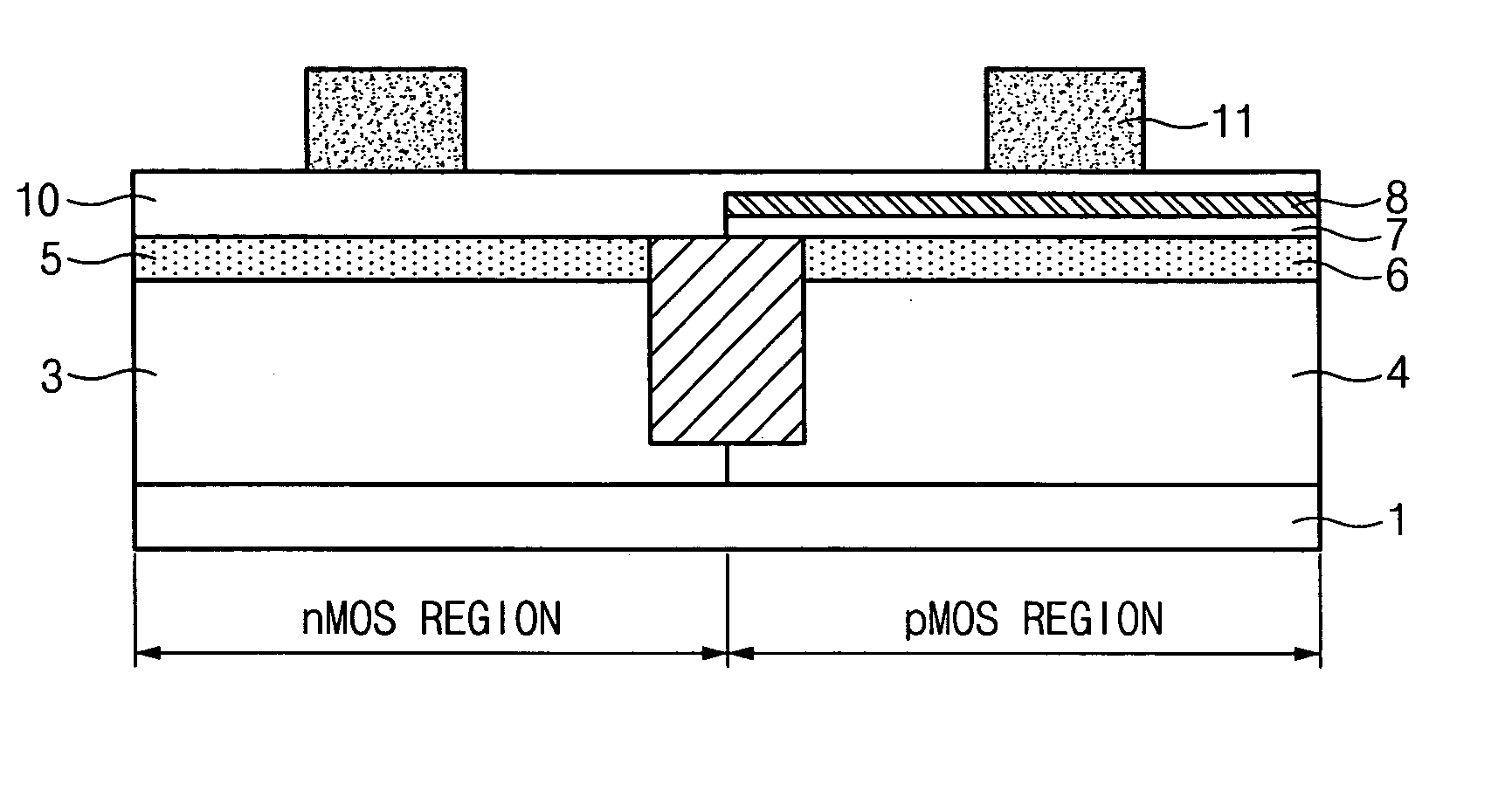

Semiconductor device and fabrication methods thereof

ActiveCN105514165AImprove performanceImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricElectrical conductor

The invention provides a semiconductor device and fabrication methods thereof. The semiconductor device includes a substrate having a logic device region including logic devices thereon, and an input / output (I / O) device region including I / O devices thereon adjacent the logic device region. A first fin field-effect transistor (FinFET) on the logic device region includes a first semiconductor fin protruding from the substrate, and a triple-gate structure having a first gate dielectric layer and a first gate electrode thereon. A second FinFET on the I / O device region includes a second semiconductor fin protruding from the substrate, and a double-gate structure having a second gate dielectric layer and a second gate electrode thereon. The first and second gate dielectric layers have different thicknesses. Related devices and fabrication methods are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

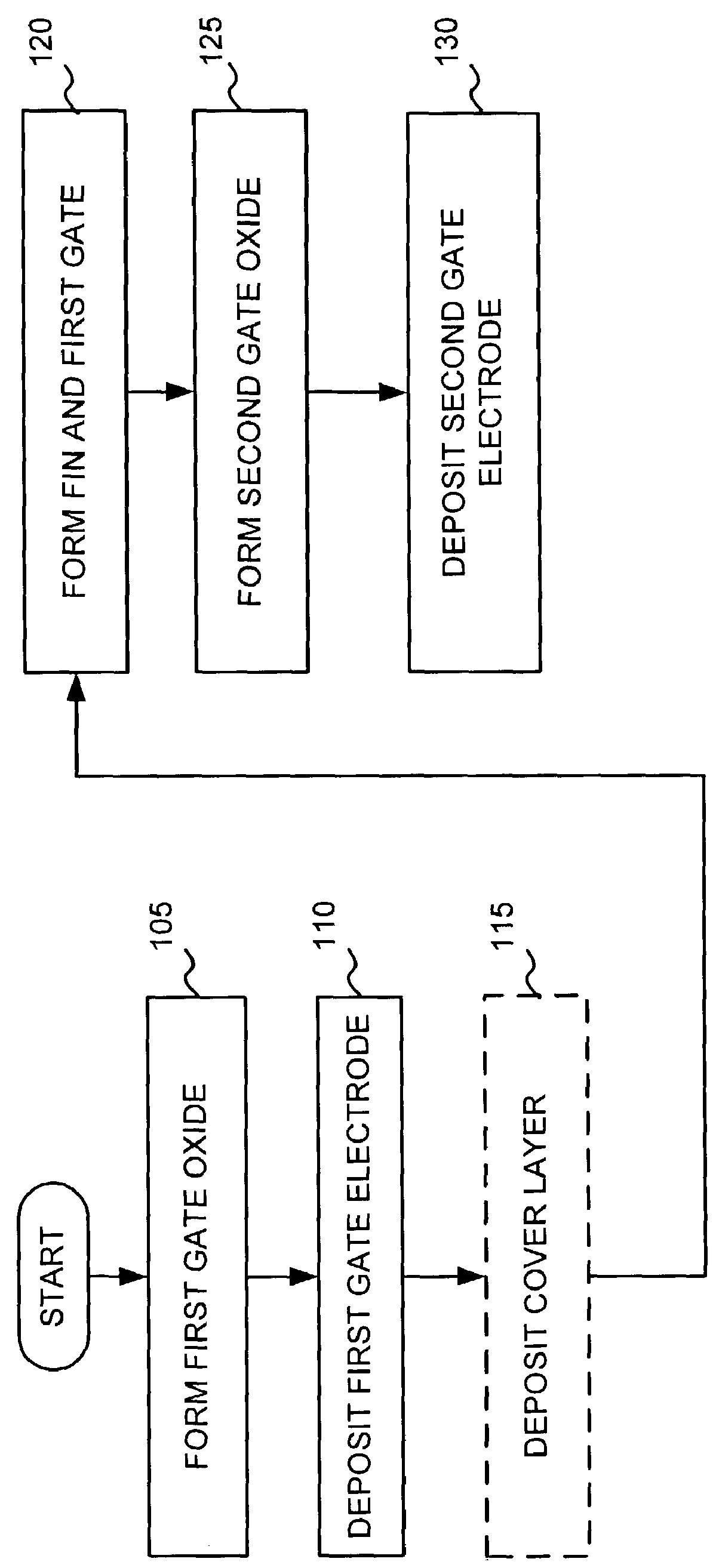

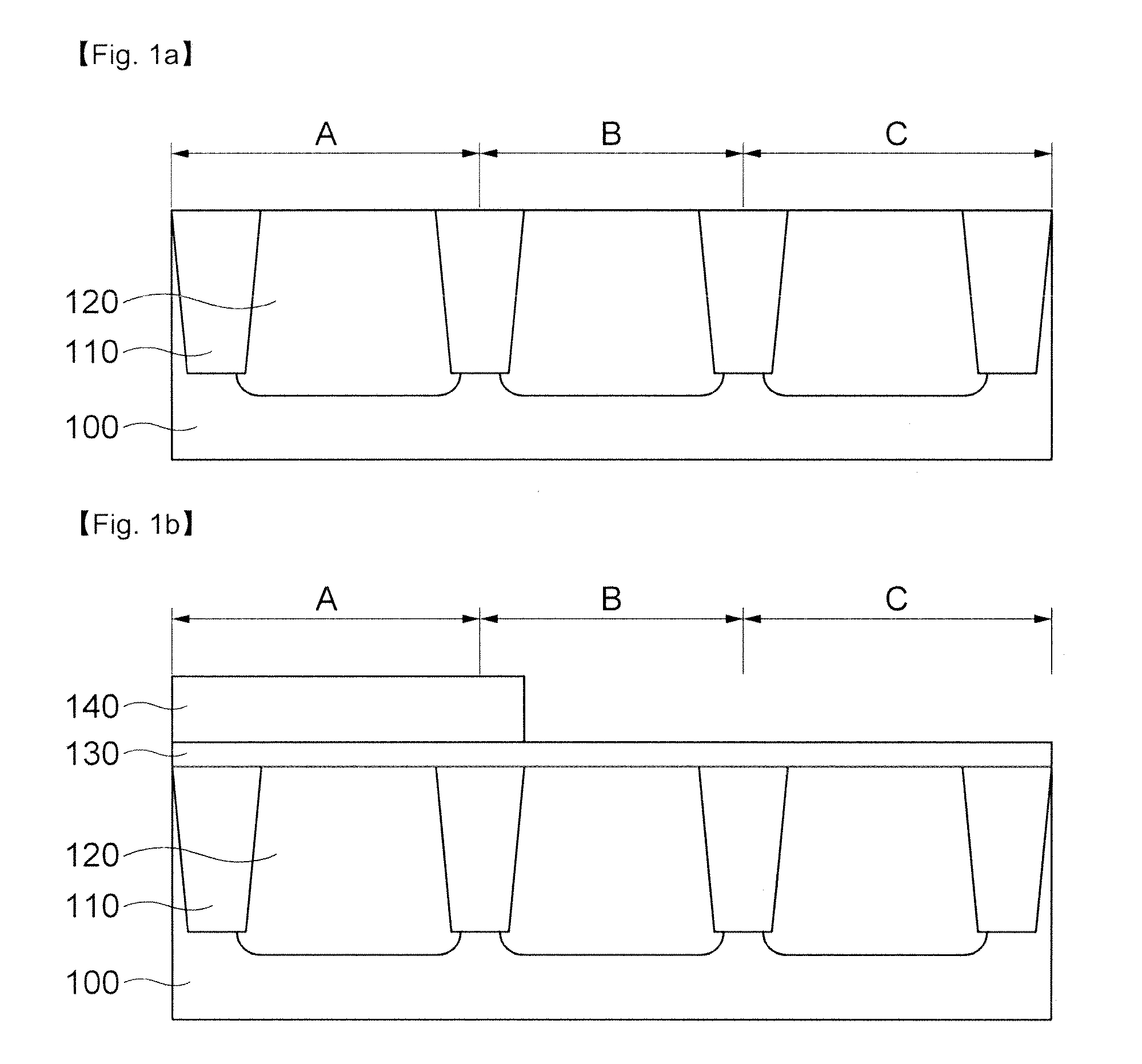

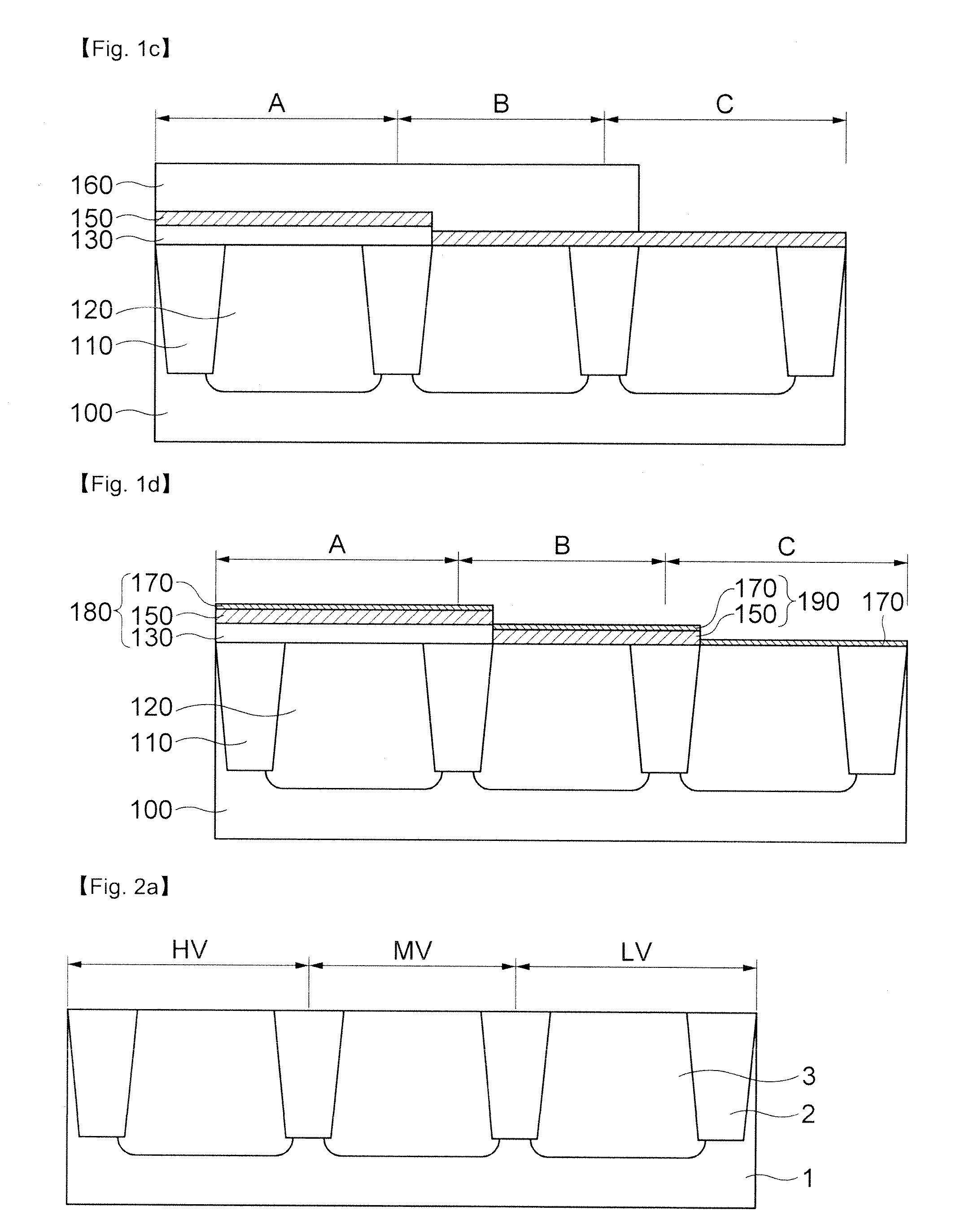

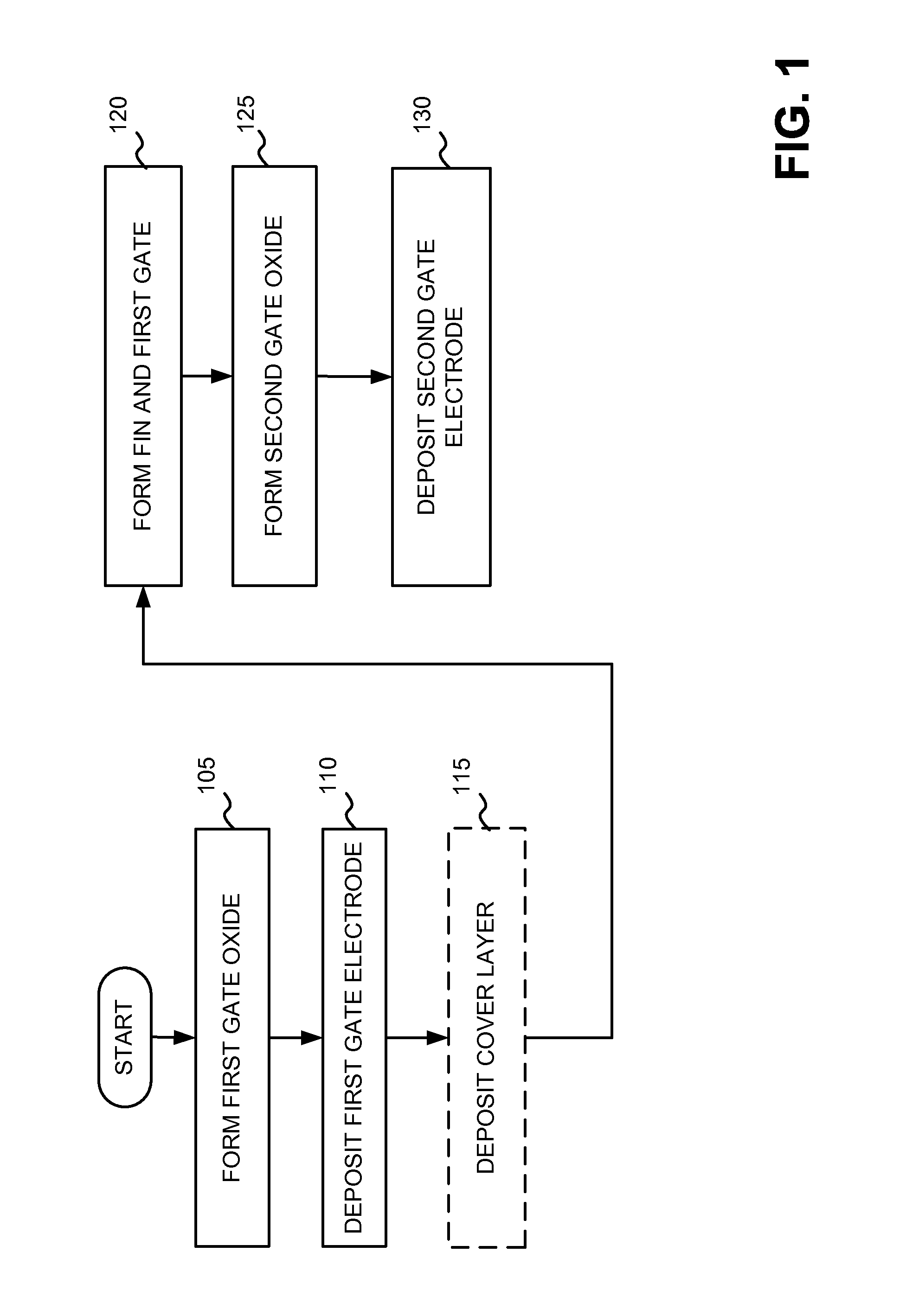

Method of integrating triple gate oxide thickness

ActiveUS20080124872A1Reduce formationNarrow downSemiconductor/solid-state device manufacturingOptoelectronicsGate oxide

A method for forming TGO structures includes providing a substrate containing regions of first, second and third kinds in which devices with respective first, second and third gate oxide layers of different thicknesses are to be formed. The second gate oxide layer is formed over the substrate and then removed from regions of the first kind where the first gate oxide layer is subsequently grown. A first conductive layer is deposited over the substrate. The first conductive layer and second gate oxide layer are subsequently removed from regions of the third kind. The third gate oxide layer followed by deposition of a second conductive layer is formed over the substrate and then removed except from over regions of the third kind.

Owner:TAIWAN SEMICON MFG CO LTD

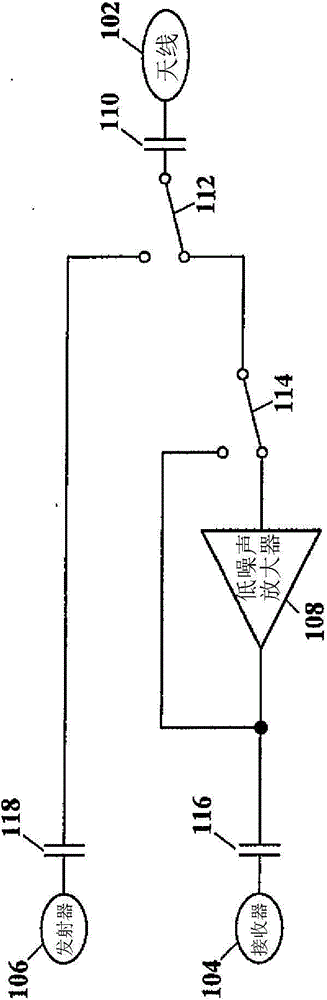

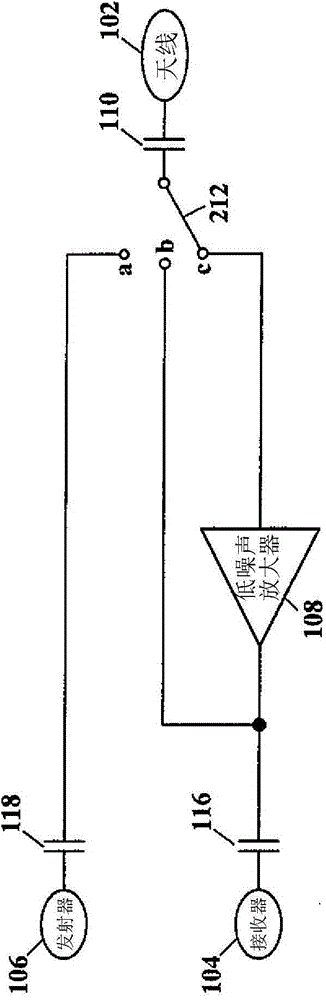

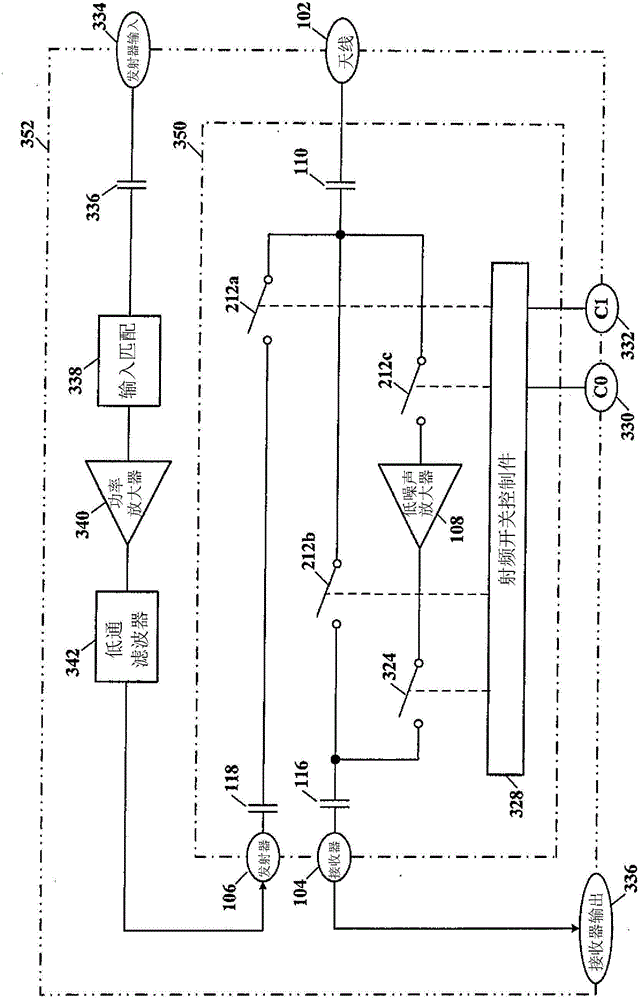

Reducing insertion loss in LNA bypass mode by using a single-pole-triple-throw switch in a RF front end module

A microwave radio frequency (RF) front end module (FEM) having a low noise amplifier (LNA) with a bypass mode uses a single-pole-triple-throw RF switch that reduces insertion loss to about 1 dB and thereby improves RF receiver sensitivity over existing technology two series connected single-pole-double throw RF switches. The single-pole-triple-throw RF switch may be three metal oxide semiconductor field effect transistor (MOSFET) RF switches that may be arranged with a common source input and isolated independent drain outputs. The RF switches may be single, double or triple gate MOSFET RF switches. The MOSFET RF switches may also be configured as complementary metal oxide semiconductor (CMOS) field effect transistor (FET) RF switches.

Owner:MICROCHIP TECH INC

Method for forming gate of semiconductor device

InactiveCN101604628ASemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGas phase

A method for forming a triple gate of a semiconductor device is provided. The method includes: forming a buffer layer and a hard mask over a substrate; etching the hard mask and the buffer layer to form a hard mask pattern and a buffer pattern; forming first and second trenches spaced apart within the substrate by partially etching the substrate by a vapor etching process using the hard mask pattern as an etching barrier layer; forming a buried insulation layer to fill the first and second trenches; removing the hard mask pattern and the buffer pattern; forming a gate insulation layer over the substrate between the first trench and the second trench; forming a conductive layer to cover the gate insulation layer; and etching the conductive layer to form a gate electrode.

Owner:KEY FOUNDRY CO LTD

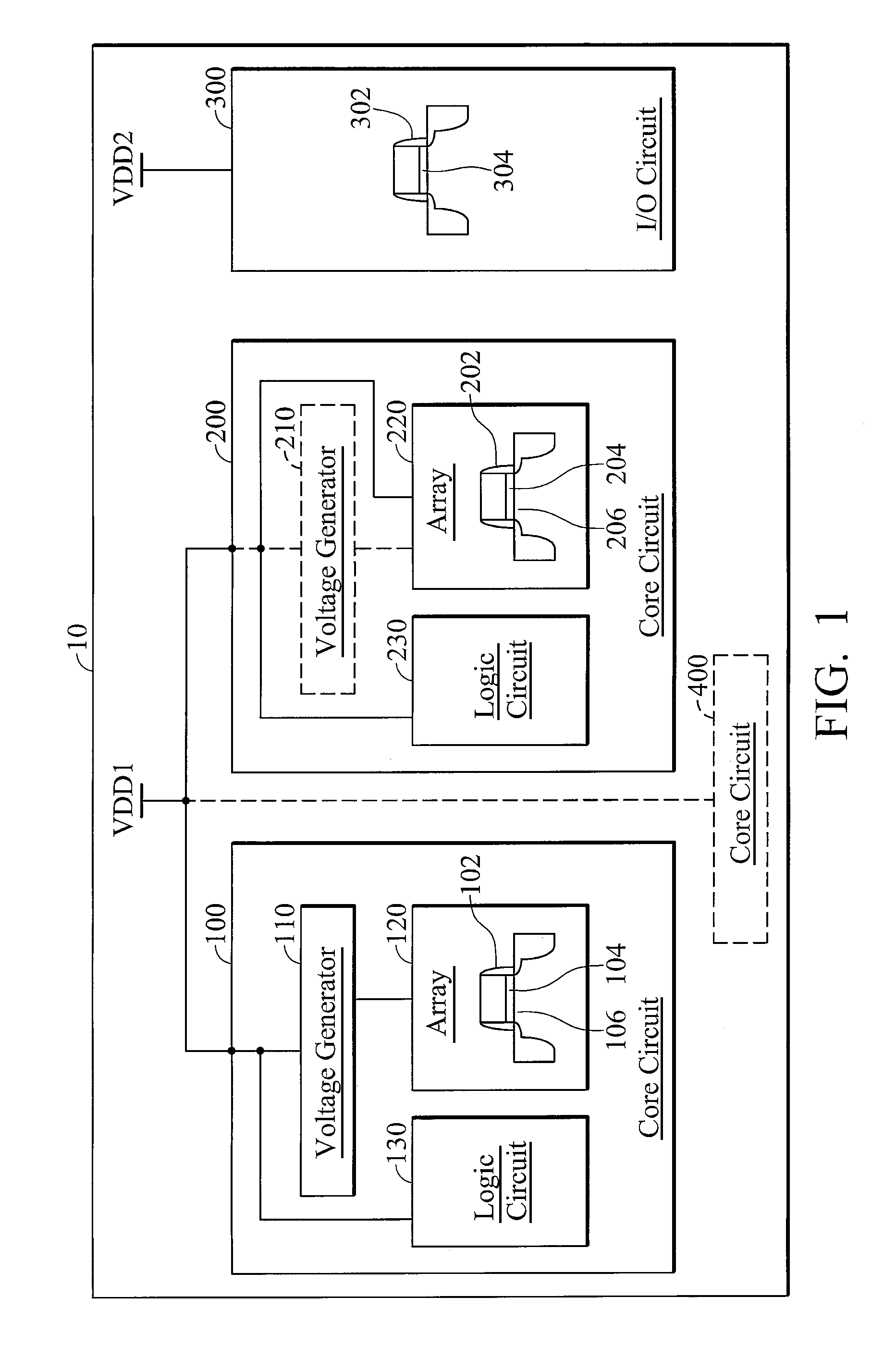

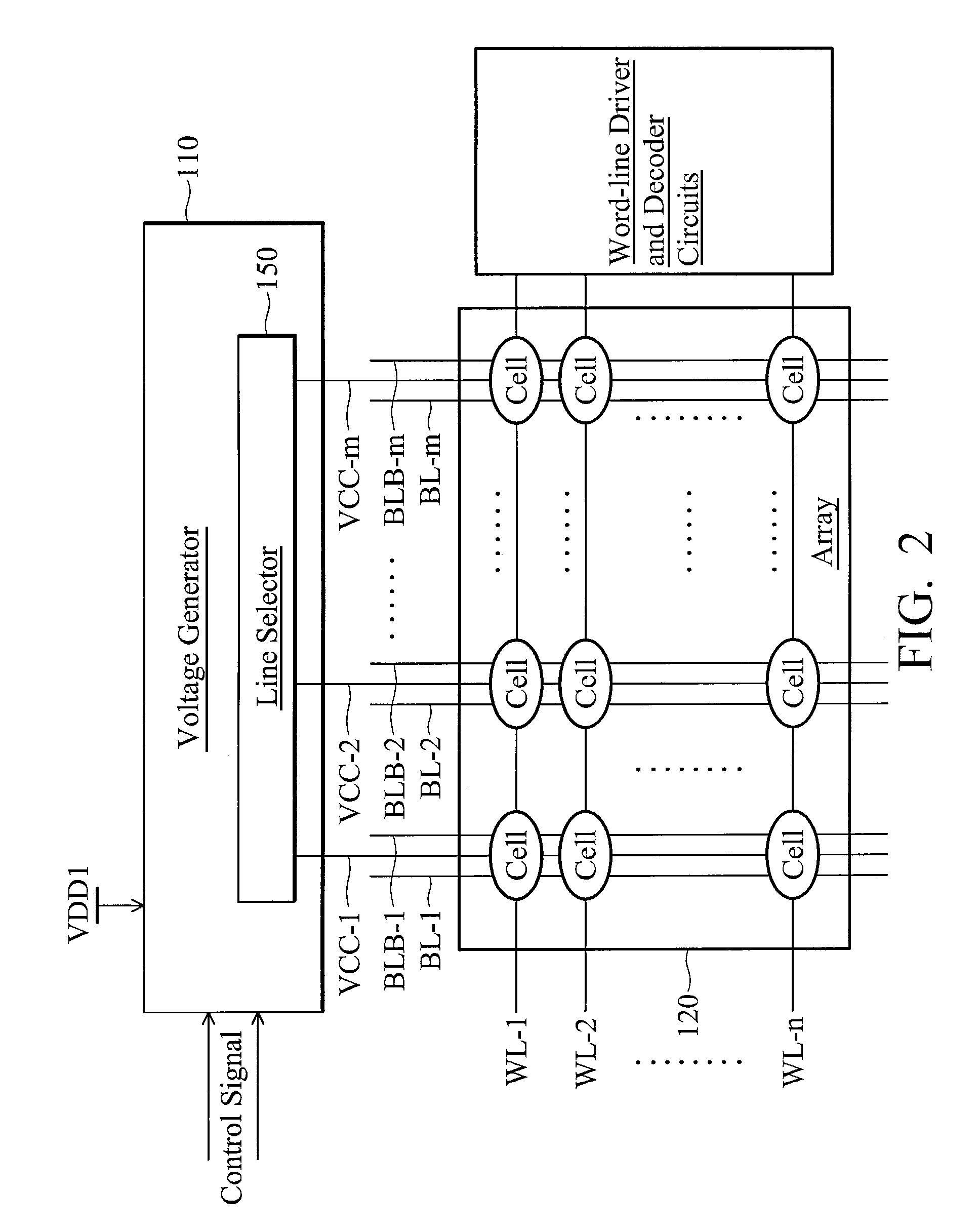

Design solutions for integrated circuits with triple gate oxides

An integrated circuit includes a first core circuit and a second core circuits. The first core circuit includes a first MOS device, wherein a first gate dielectric of the first MOS device has a first thickness. The second core circuit includes a second MOS device, wherein a second gate dielectric of the second MOS device has a second thickness less than the first thickness. A first power supply line having a first power supply voltage is connected to the first and the second core circuits a first power supply voltage.

Owner:TAIWAN SEMICON MFG CO LTD

Method for forming gate oxide of semiconductor device

ActiveUS7892960B2Improve uniformityImprove characteristic and uniformitySemiconductor/solid-state device detailsSolid-state devicesRegioselectivityGate oxide

Owner:KEY FOUNDRY CO LTD

Method for driving liquid crystal display panel with triple gate arrangement

A method is provided for driving a liquid crystal display panel in which each pixel includes a plurality of sub-pixels arranged in a specific direction, the method including feeding drive voltages to sub-pixels within the liquid crystal display panel by using operational amplifiers. The polarities of the drive voltages fed to each of the sub-pixels are inverted between two adjacent frame periods. The offset polarities of the operational amplifiers are inverted for every a predetermined number of successive sub-pixels. The number of the sub-pixels within each pixel is coprime to the predetermined number of successive sub-pixels.

Owner:RENESAS ELECTRONICS CORP

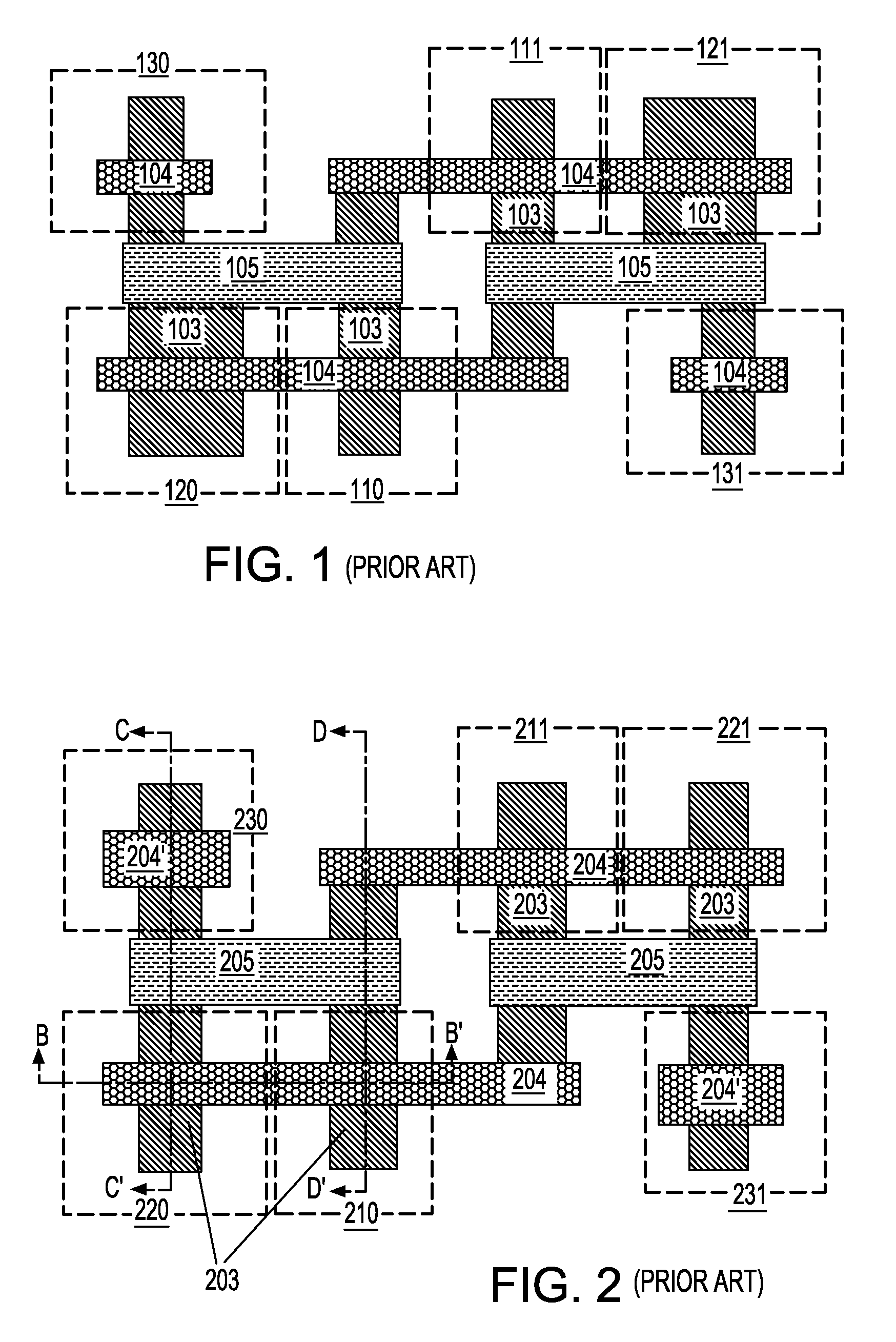

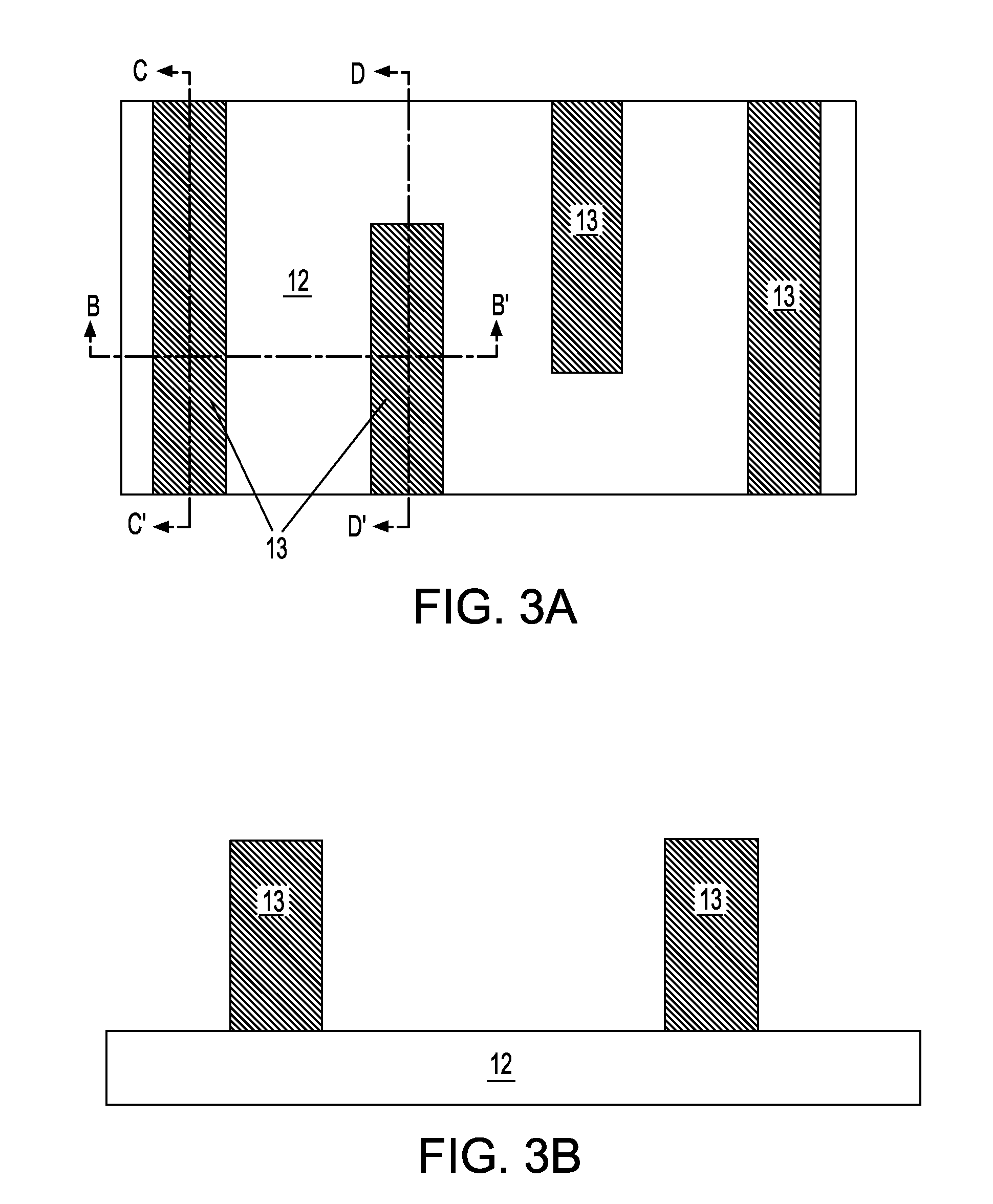

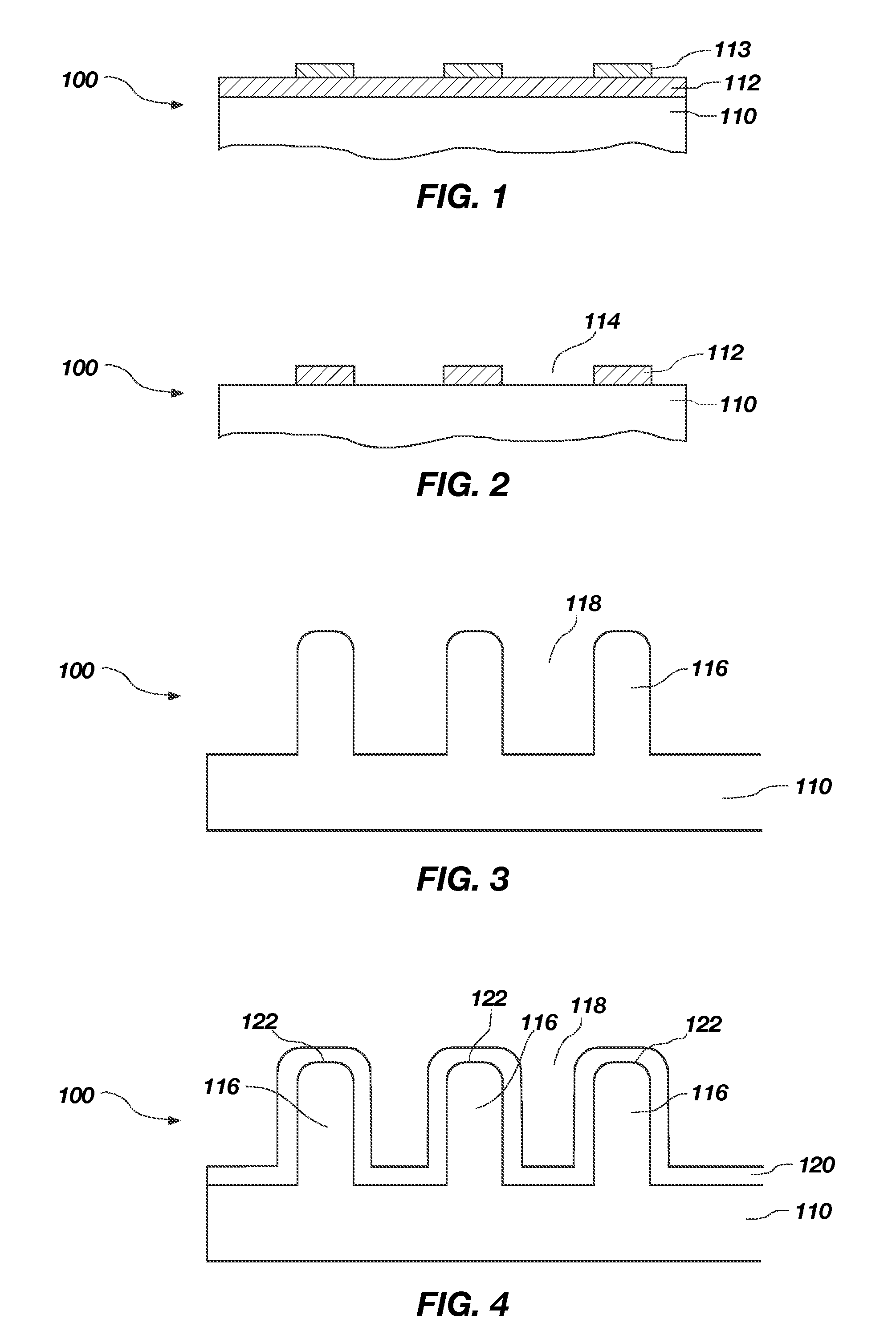

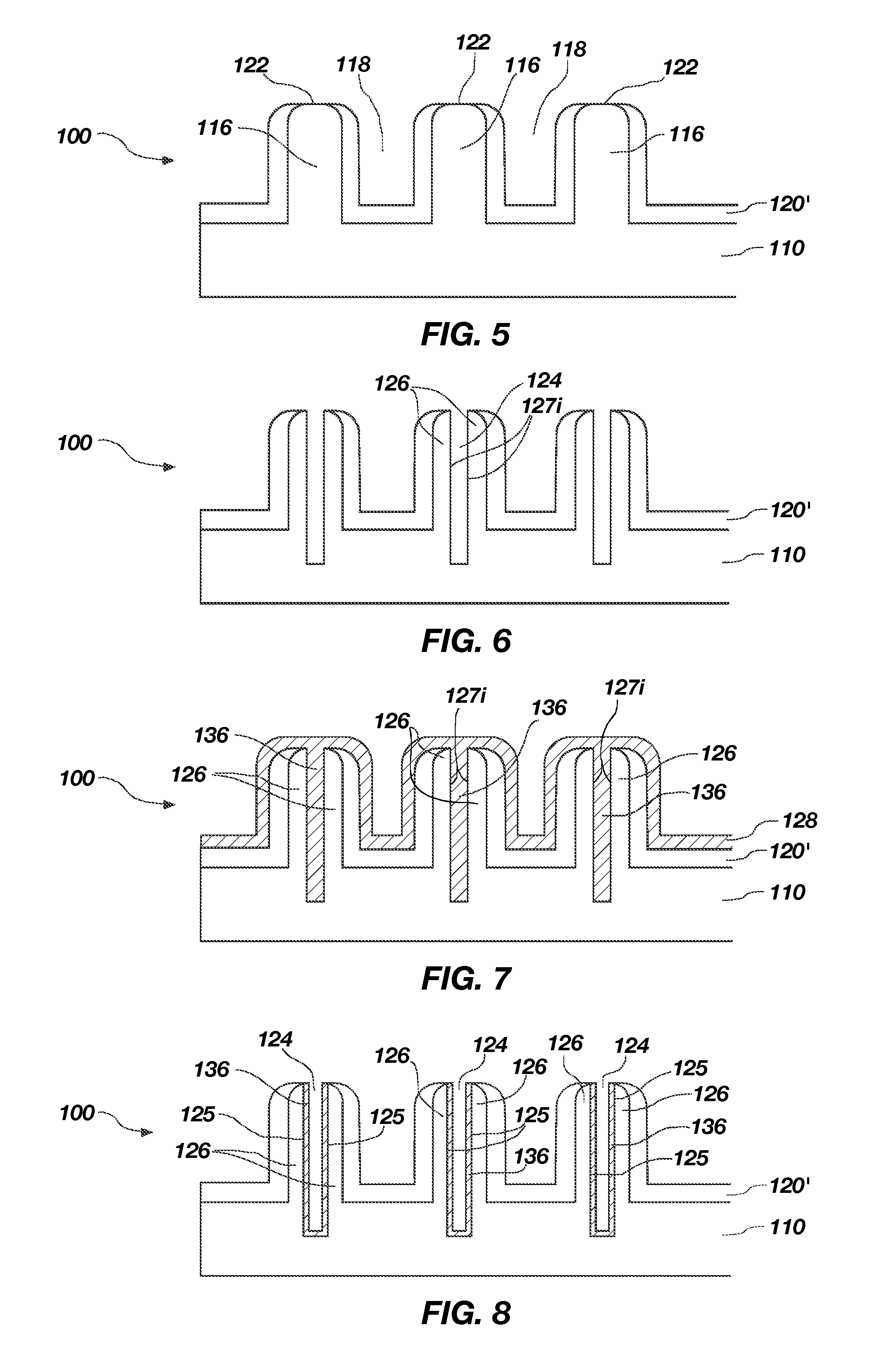

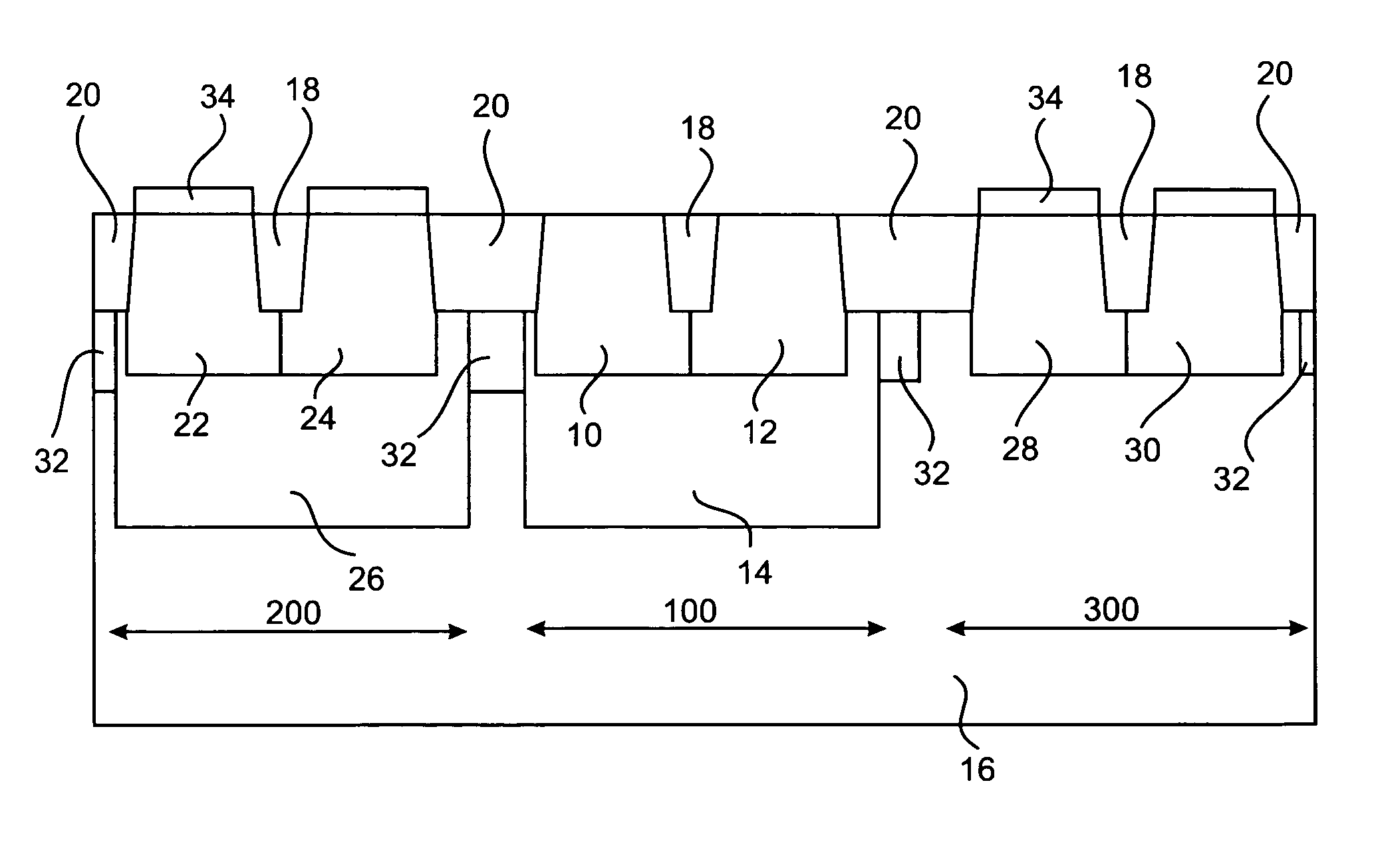

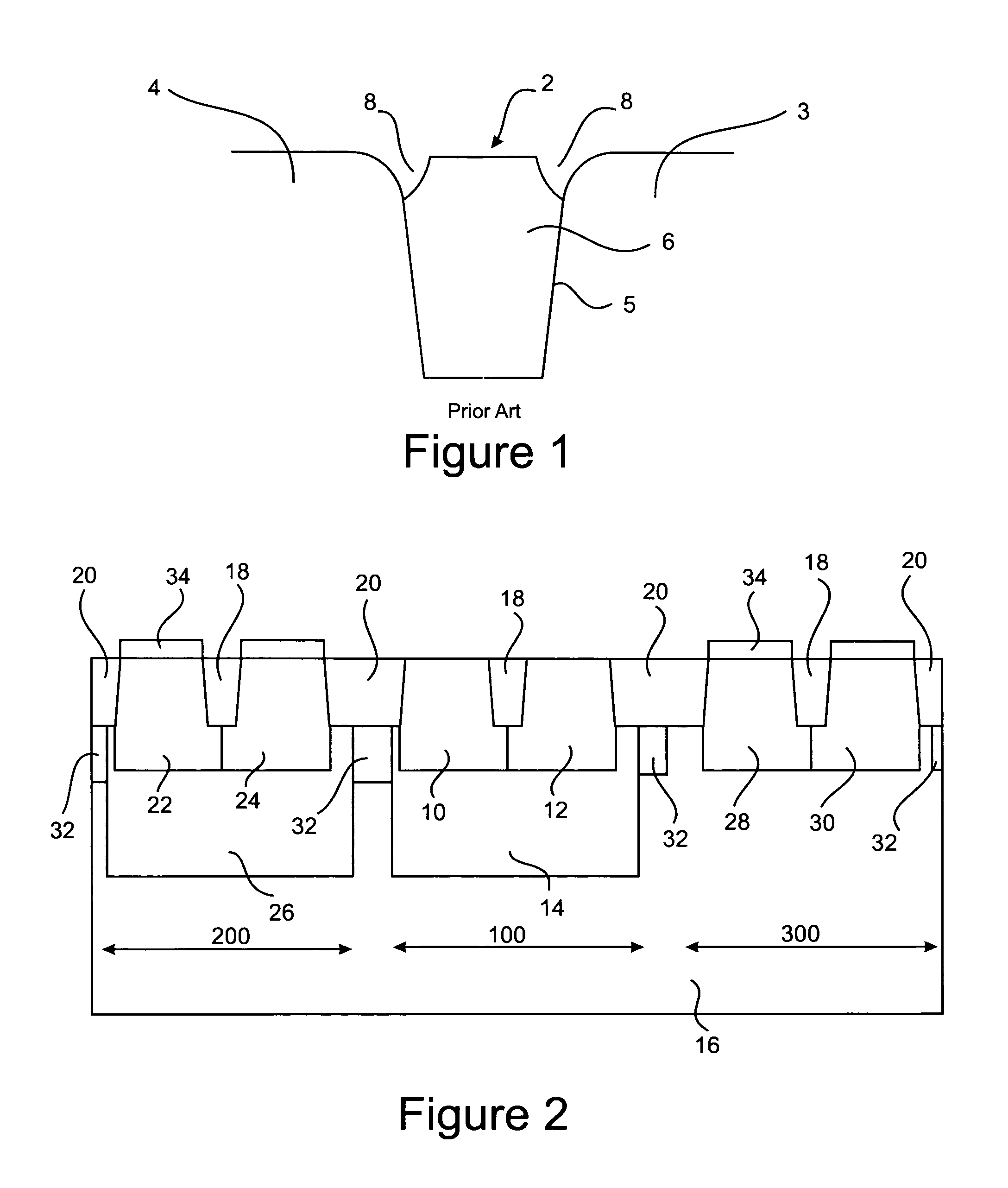

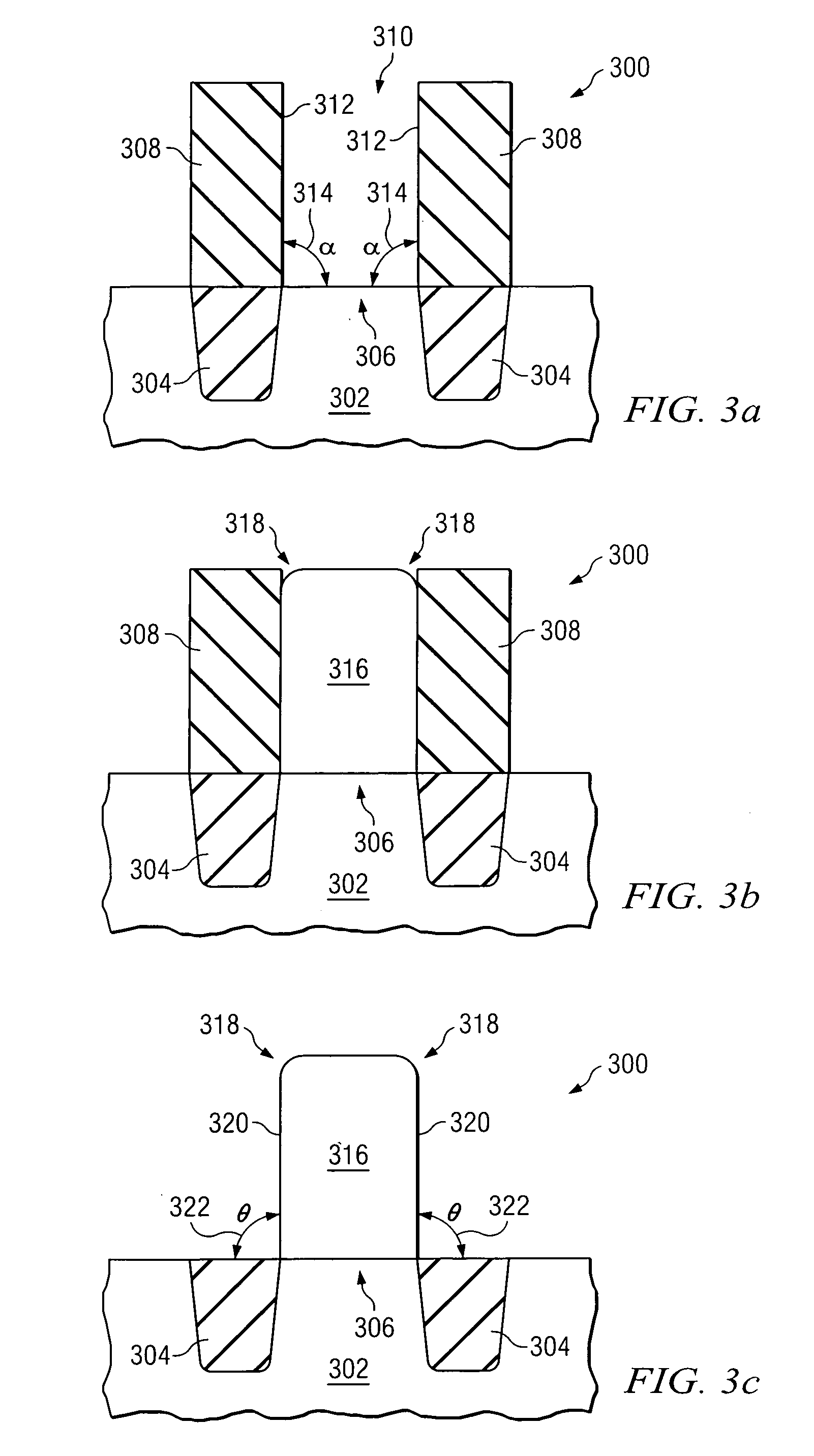

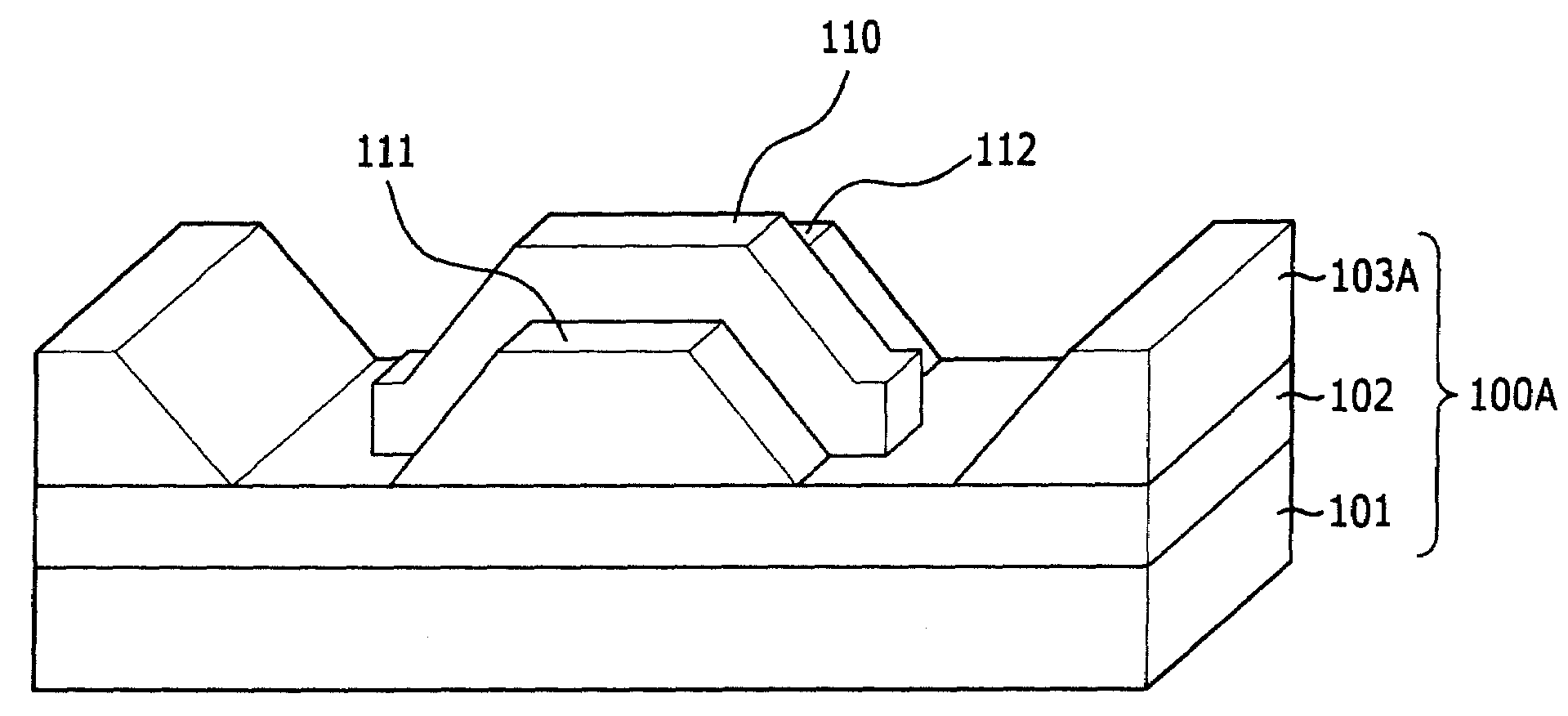

Methods of fabricating dual fin structures and semiconductor device structures with dual fin structures

ActiveUS20090032866A1Semiconductor/solid-state device manufacturingSemiconductor devicesElectronic systemsDevice material

Fin-FET devices and methods of fabrication are disclosed. The Fin-FET devices include dual fins that may be used to provide a trench region between a source region and a drain region. In some embodiments, the dual fins may be formed by forming a trench with fin structures on opposite sides in a protruding region of a substrate. The dual fins may be useful in forming single-gate, double-gate or triple-gate fin-FET devices. Electronic systems including such fin-FET devices are also disclosed.

Owner:MICRON TECH INC

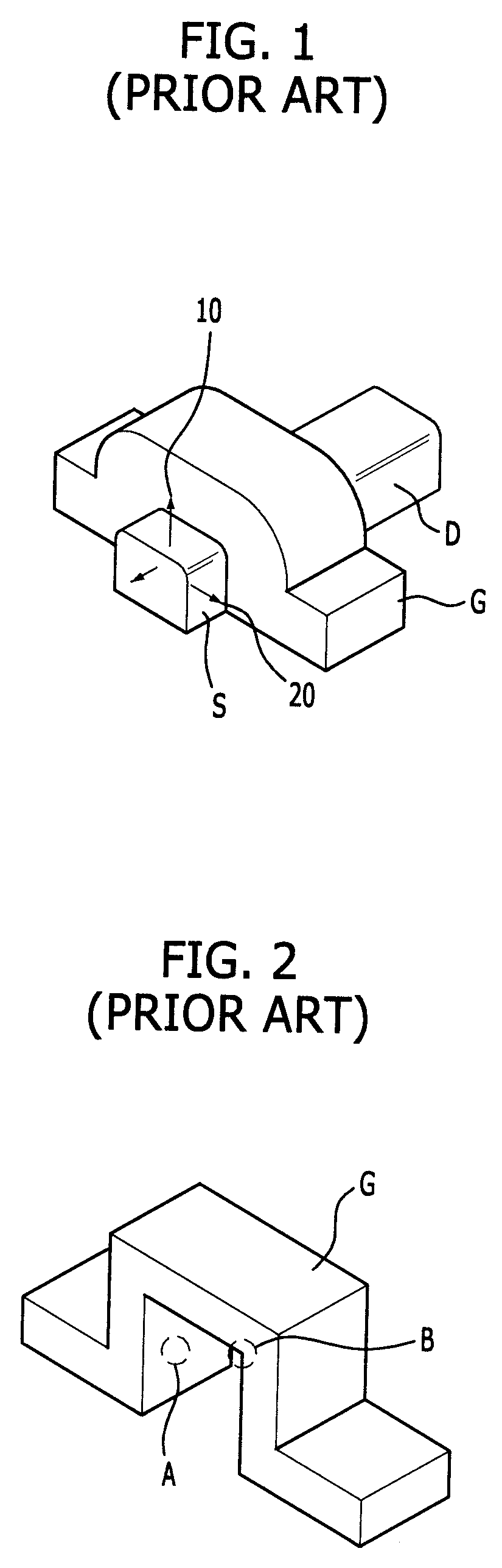

Triple-gate mosfet transistor and methods for fabricating the same

ActiveUS20050095764A1TransistorSemiconductor/solid-state device manufacturingCondensed matter physicsSemiconductor

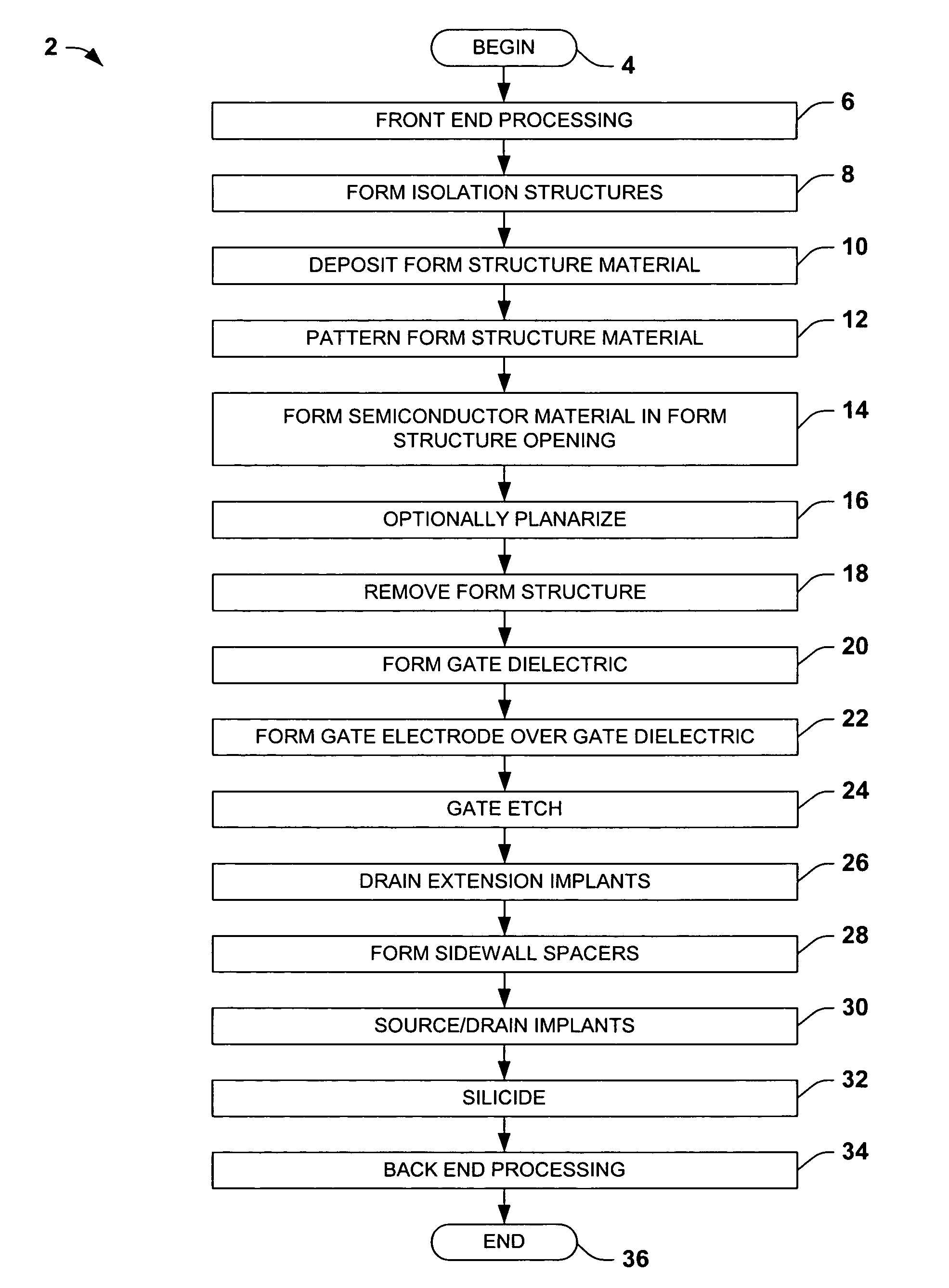

Fabrication methods are presented in which a semiconductor body is deposited in a cavity of a temporary form structure above a semiconductor starting structure. The formed semiconductor body can be epitaxial silicon deposited in the form cavity over a silicon substrate, and includes three body portions, two of which are doped to form source / drains, and the other forming a transistor channel that overlies the starting structure. A gate structure is formed along one or more sides of the channel body portion to create a MOS transistor.

Owner:TEXAS INSTR INC

Method for forming gate oxide of semiconductor device

ActiveUS20090179255A1Excellent characteristicsImprove uniformitySemiconductor/solid-state device detailsSolid-state devicesRegioselectivityGate oxide

The method for forming a triple gate oxide of a semiconductor device includes the steps of defining a first region, a second region and a third region, forming a first oxide film and forming a second oxide film on the first oxide film, blocking the first region and selectively removing portions the second oxide film and the first oxide film, forming a third oxide film on the semiconductor substrate, blocking the first region and the second region and selectively removing a portion of the third oxide film and forming a fourth oxide film on the semiconductor substrate and then forming a nitride film thereon, wherein a gate oxide having a triple structure is formed in the first region, a gate oxide having a double structure is formed in the second region and a gate oxide having a double structure is formed in the third region.

Owner:KEY FOUNDRY CO LTD

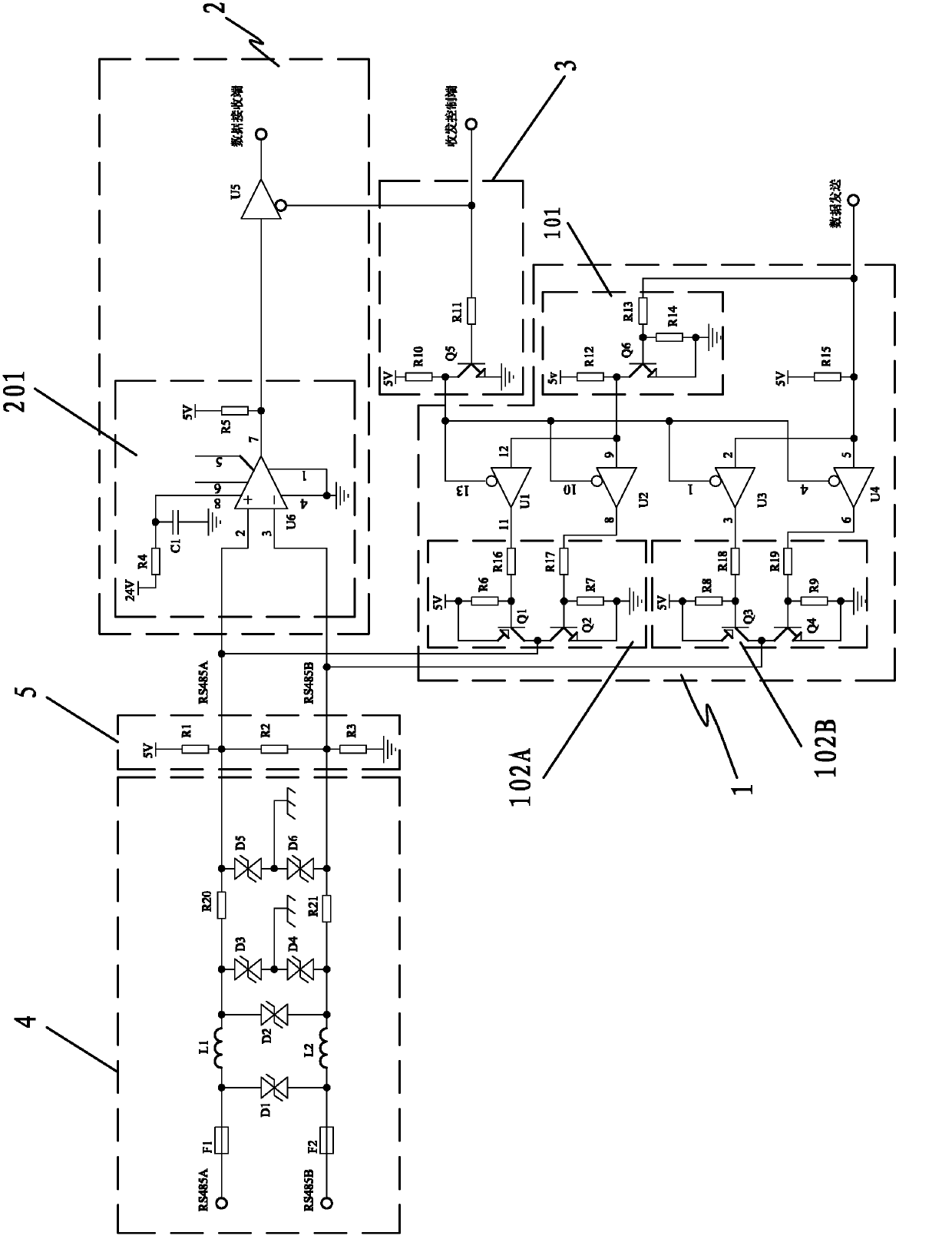

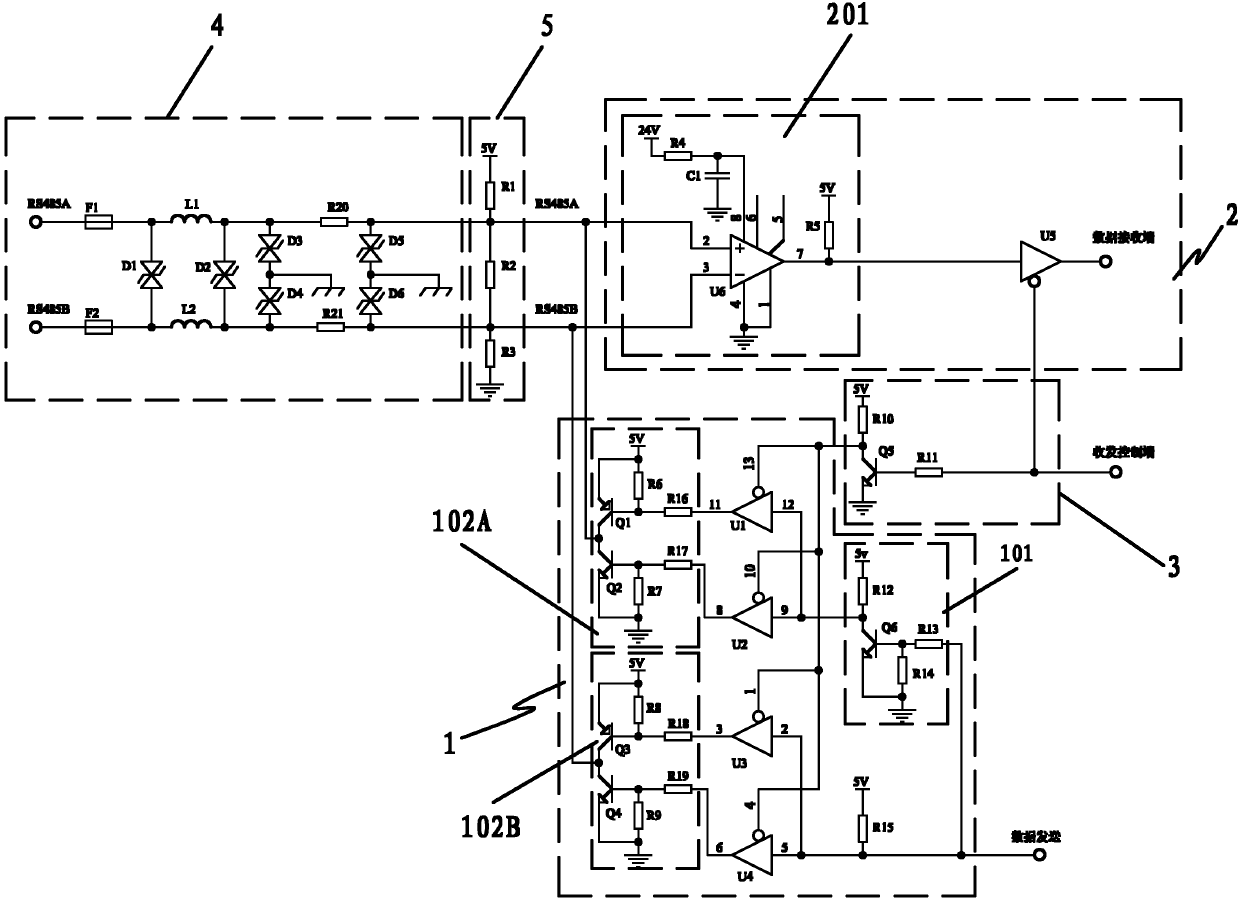

RS485 bus interface circuit

InactiveCN102169472AIncrease powerRealize signal outputElectric digital data processingTransceiverDifferential signaling

The invention relates to the technical field of communication of RS485 buses, in particular to an RS485 bus interface circuit. The technical scheme is that: a differential signal transmission circuit section of an RS485 interface consists of a triode inverter, two sets of push-pull type inverting amplifiers and four triple gates, wherein the output end of the triode inverter is connected to the two push-pull signal input ends of a first set of push-pull type inverting amplifier through a first triple gate and a second triple gate respectively; the output end of the first set of push-pull typeinverting amplifier is connected with a first differential signal wire RS485A; and a direct signal of a second set of push-pull type inverting amplifier is communicated with the input end of the triode inverter and a second differential signal wire RS485B. Through the two sets of push-pull type inverting amplifiers, an RS485 differential signal can be output, and the power of an output signal is effectively improved, so that the communication distance in the scheme can reach 2,000 m, 64 transceivers can be hung, and the communication rate can reach 9,600 bps.

Owner:QUANZHOU WANHUA TECH

Method for forming gate oxide of semiconductor device

ActiveUS20110057252A1Improve uniformityImprove characteristic and uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideNitride

Disclosed herein is a method for forming a triple gate oxide of a semiconductor device. The method for forming a triple gate oxide of a semiconductor device includes the steps of defining a first region where a gate oxide having a first thickness will be formed, a second region where a gate oxide having a second thickness will be formed and a third region where a gate oxide having a third thickness will be formed on a semiconductor substrate, forming a first oxide film through wet oxidation on the semiconductor substrate and forming a second oxide film on the first oxide film, blocking the first region and selectively removing portions the second oxide film and the first oxide film, which are formed on the second region and the third region, forming a third oxide film through thermal oxidation on the semiconductor substrate, blocking the first region and the second region and selectively removing a portion of the third oxide film, which is formed on the third region, and forming a fourth oxide film through thermal oxidation on the semiconductor substrate and then forming a nitride film thereon, wherein a gate oxide having a triple structure of the first oxide film / second oxide film / nitride film is formed in the first region, a gate oxide having a double structure of the third oxide film / nitride film is formed in the second region and a gate oxide having a double structure of the fourth oxide film / nitride film is formed in the third region.

Owner:SK KEYFOUNDRY INC

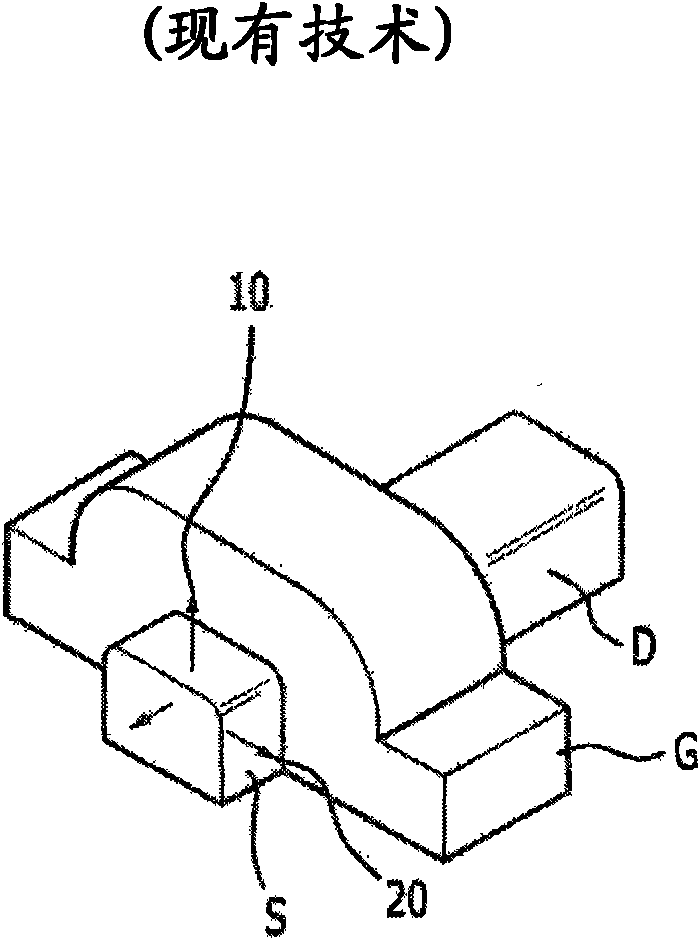

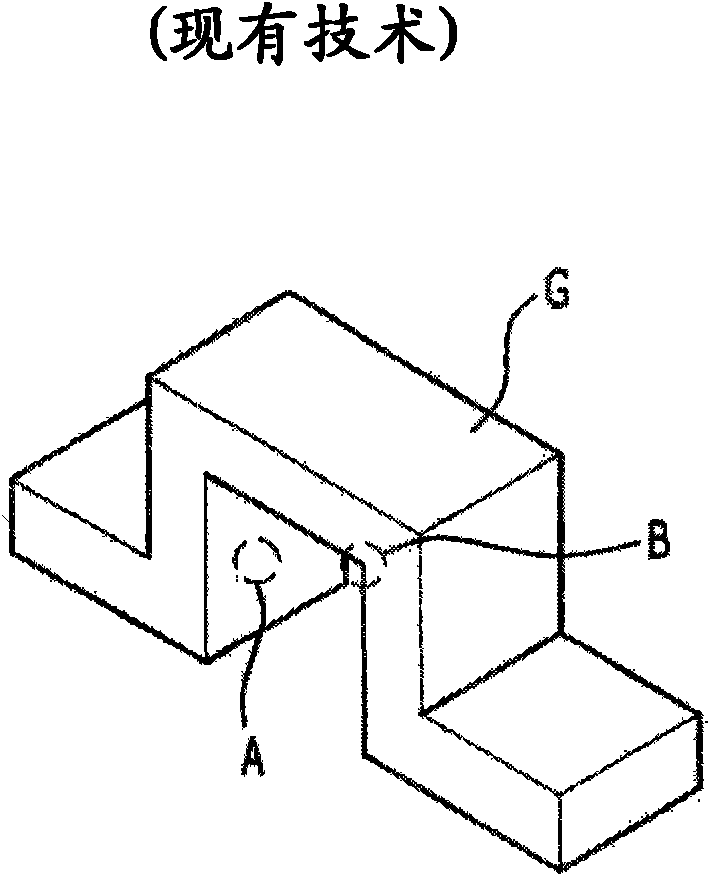

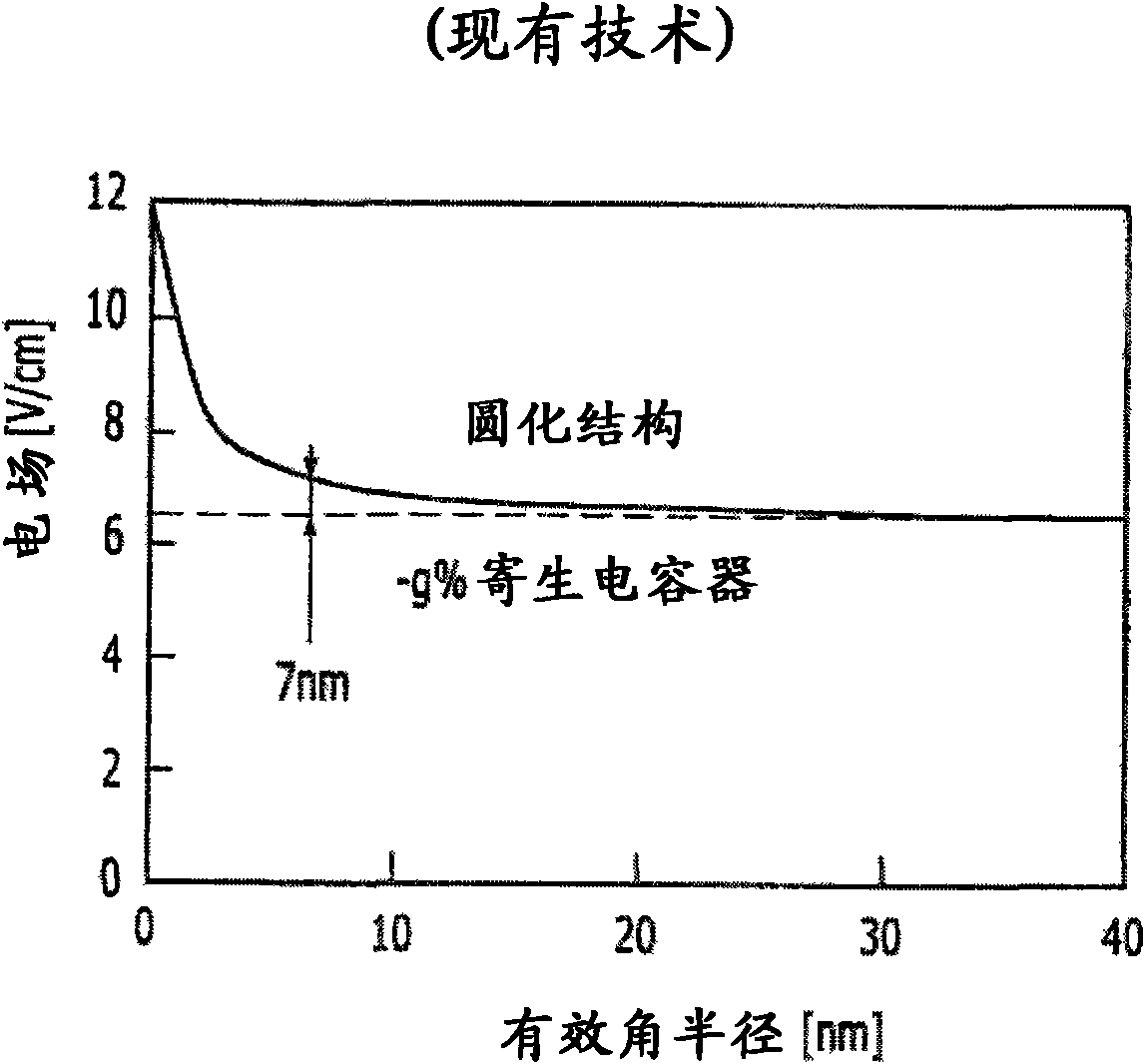

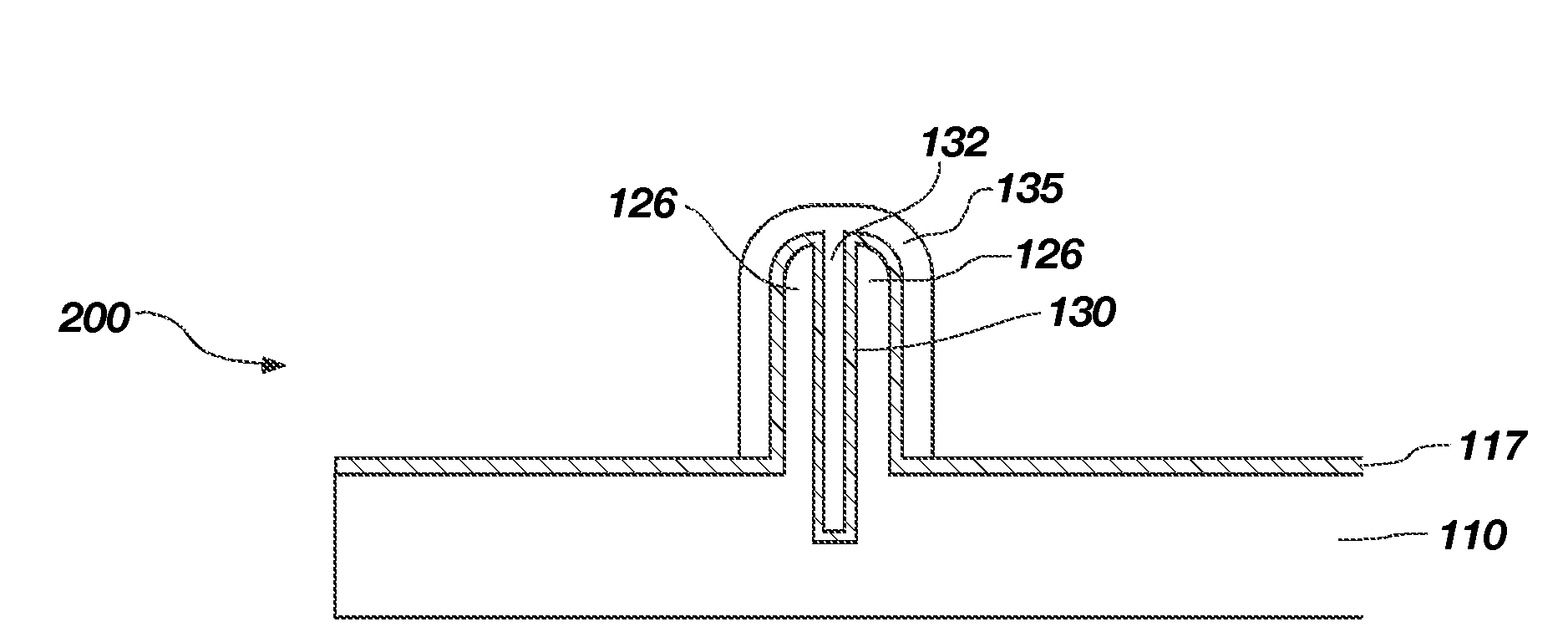

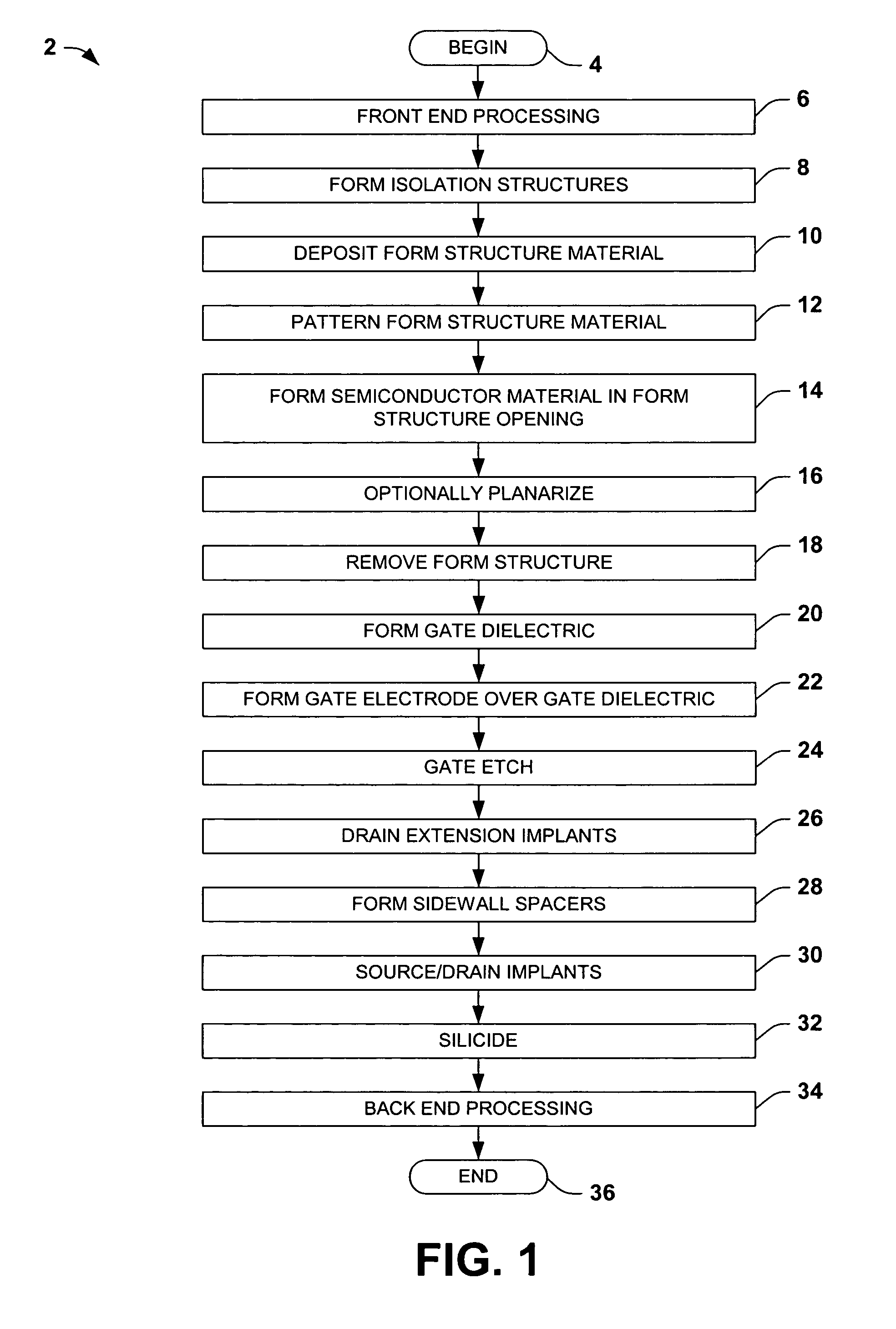

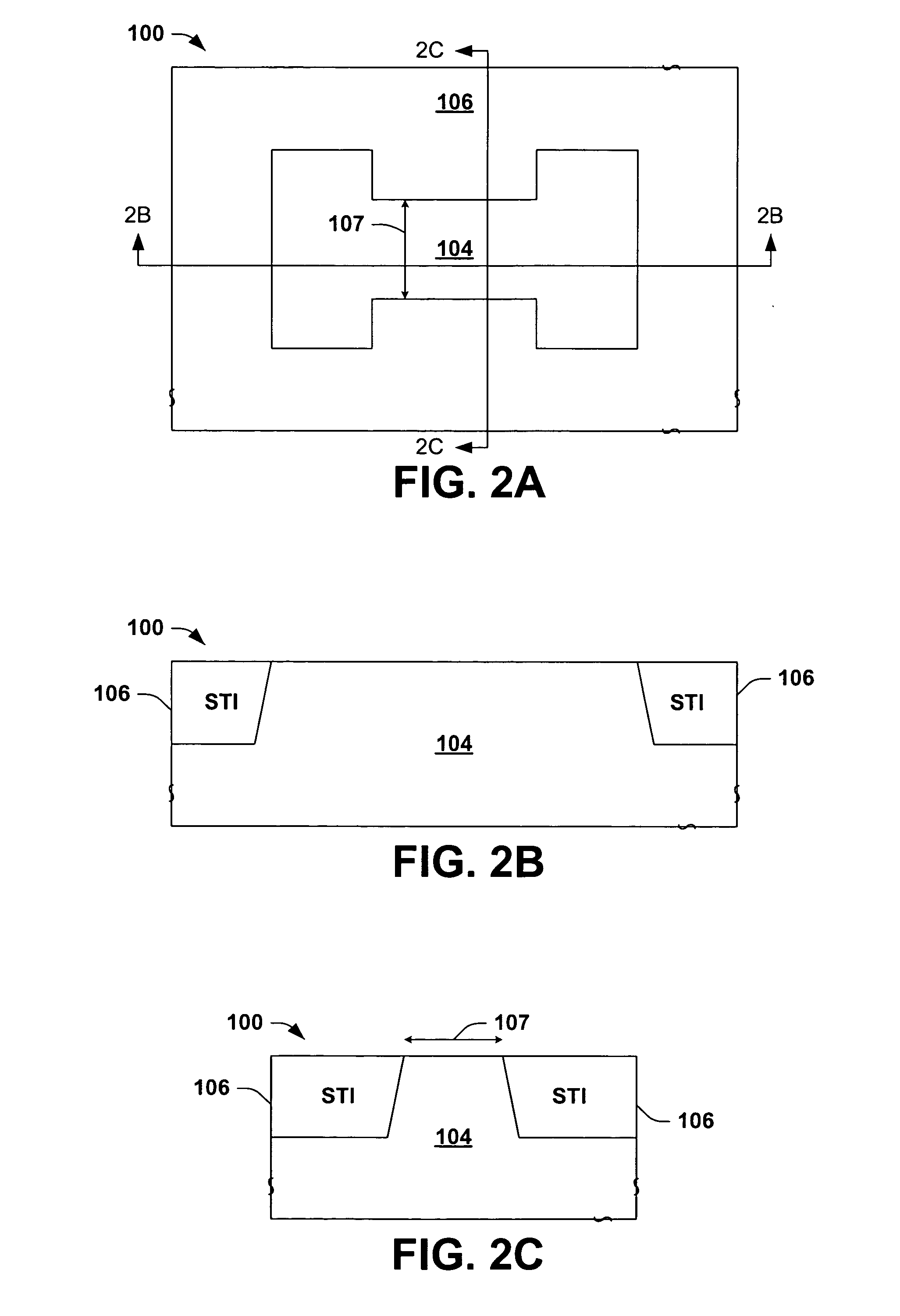

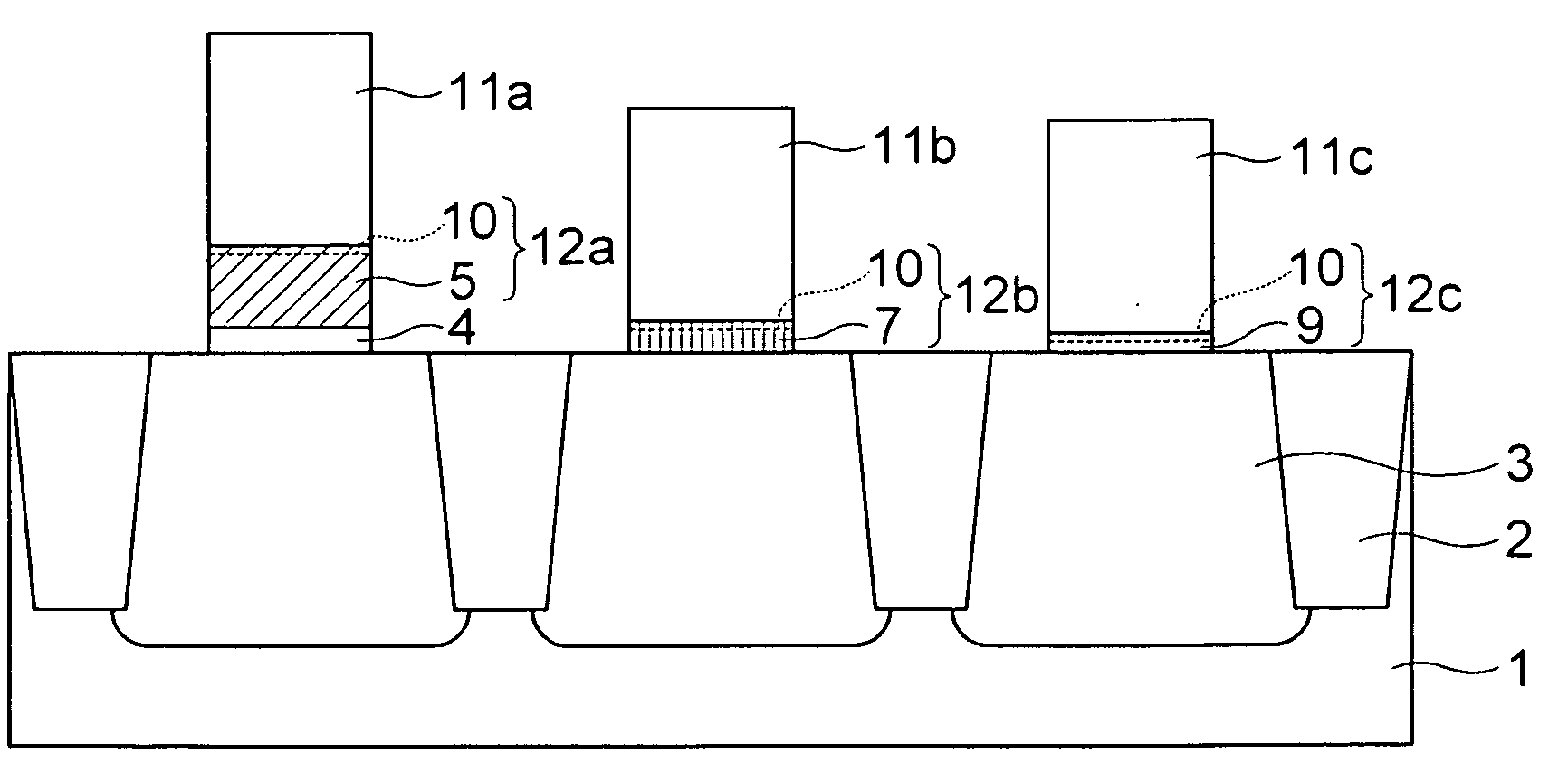

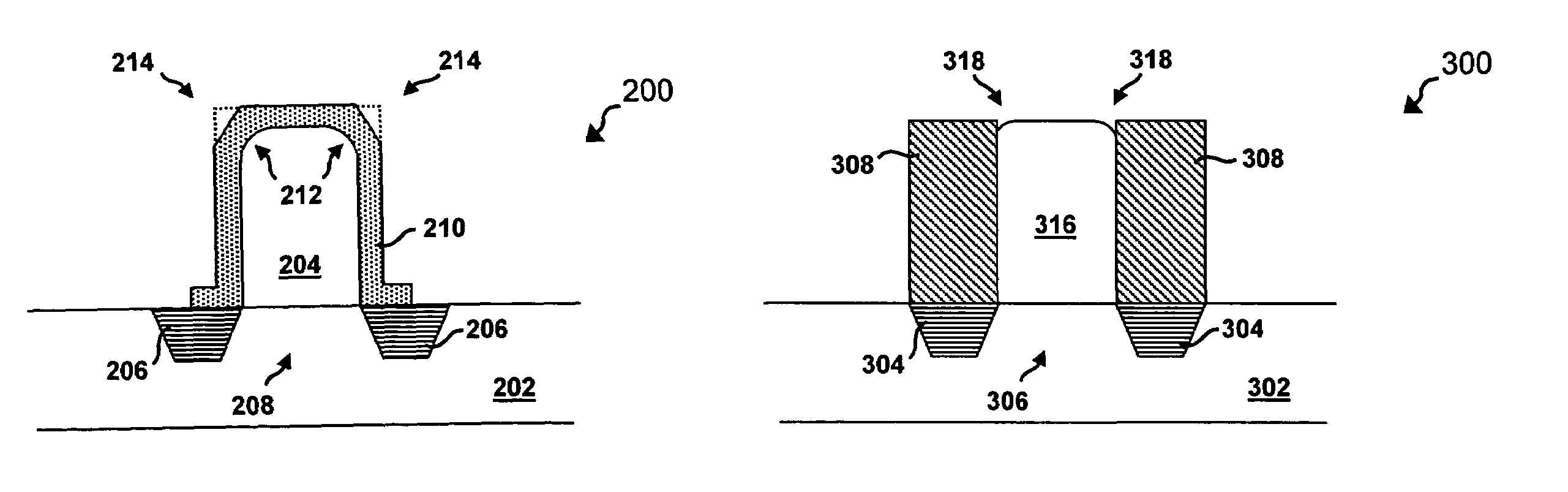

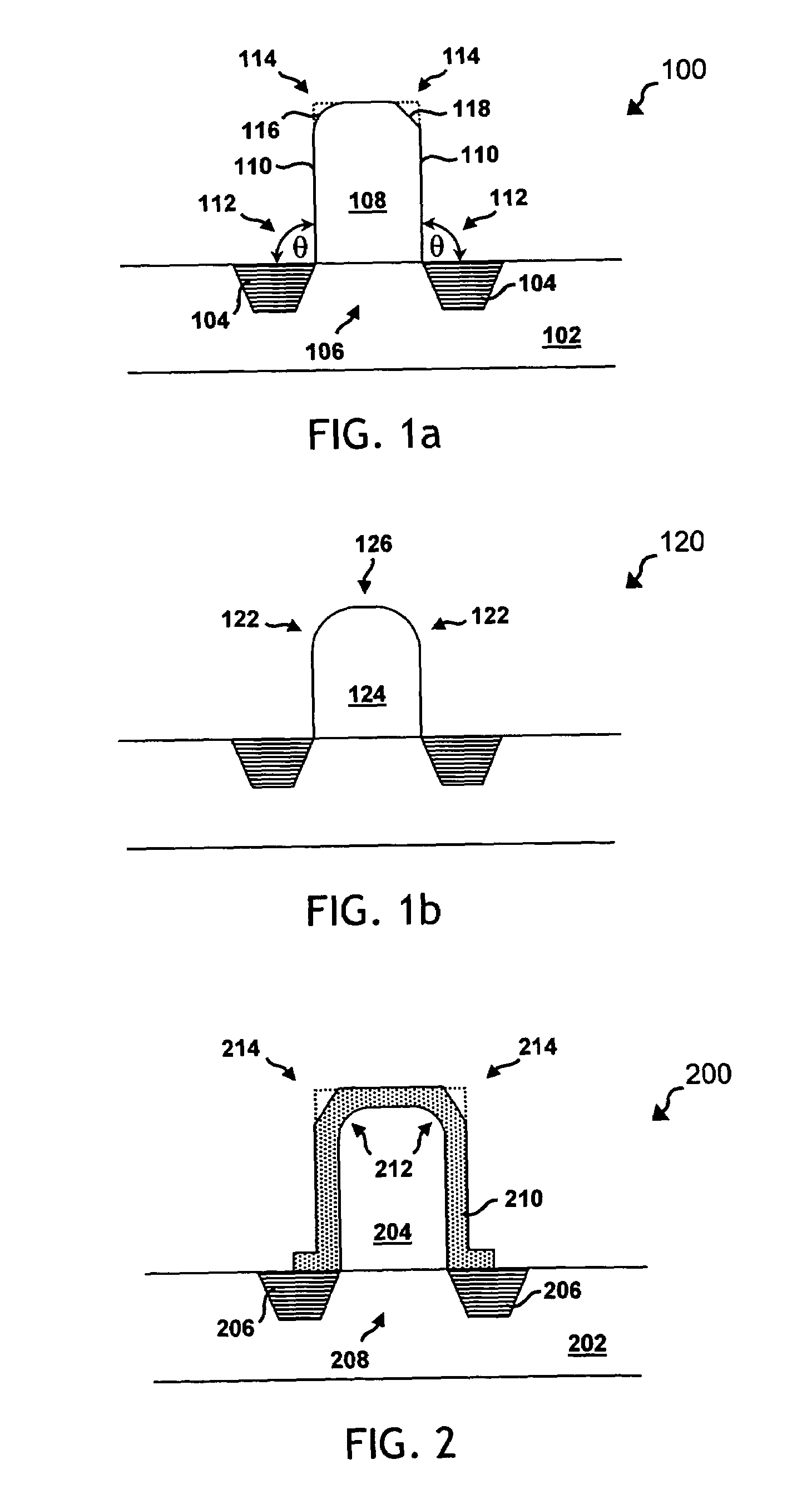

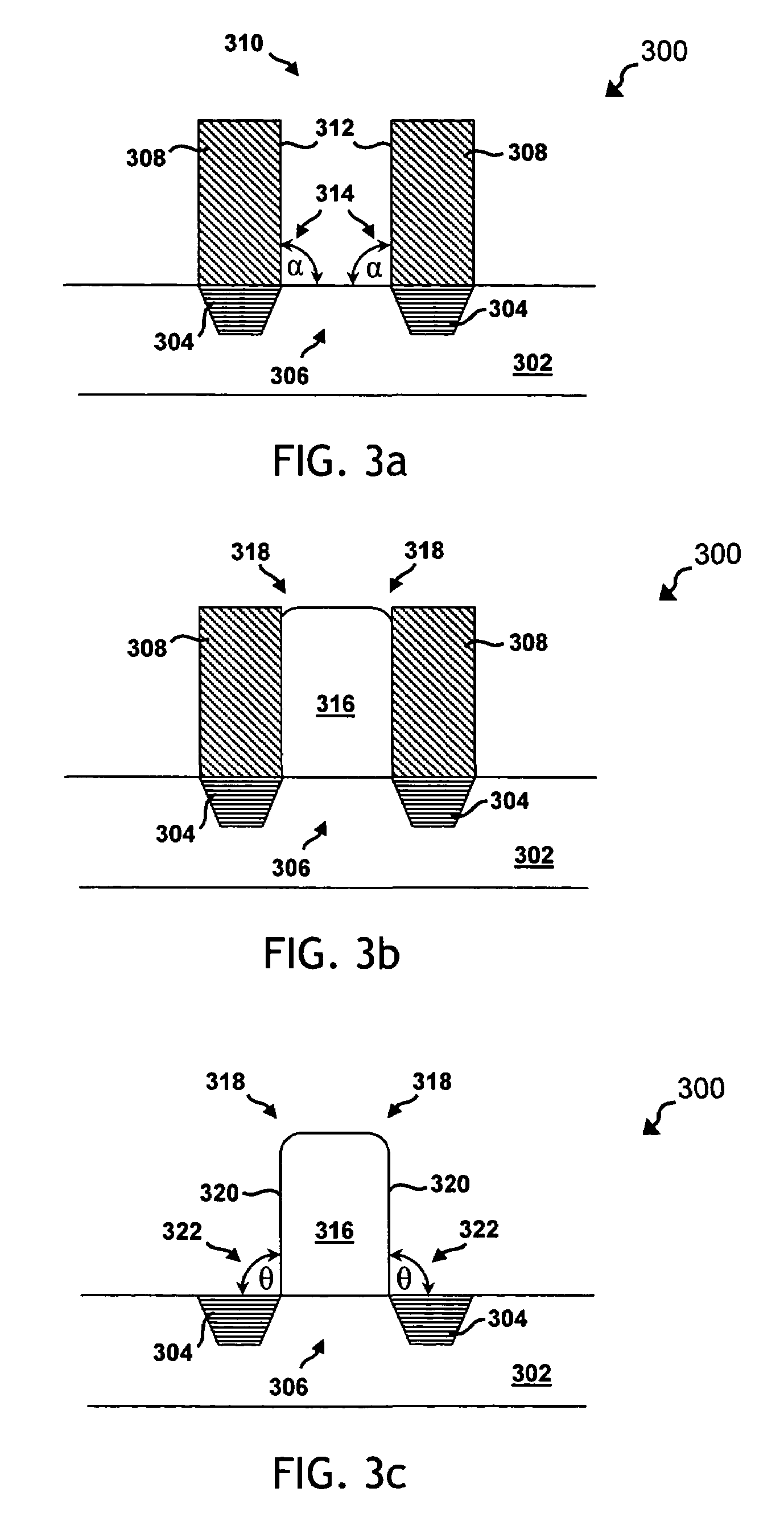

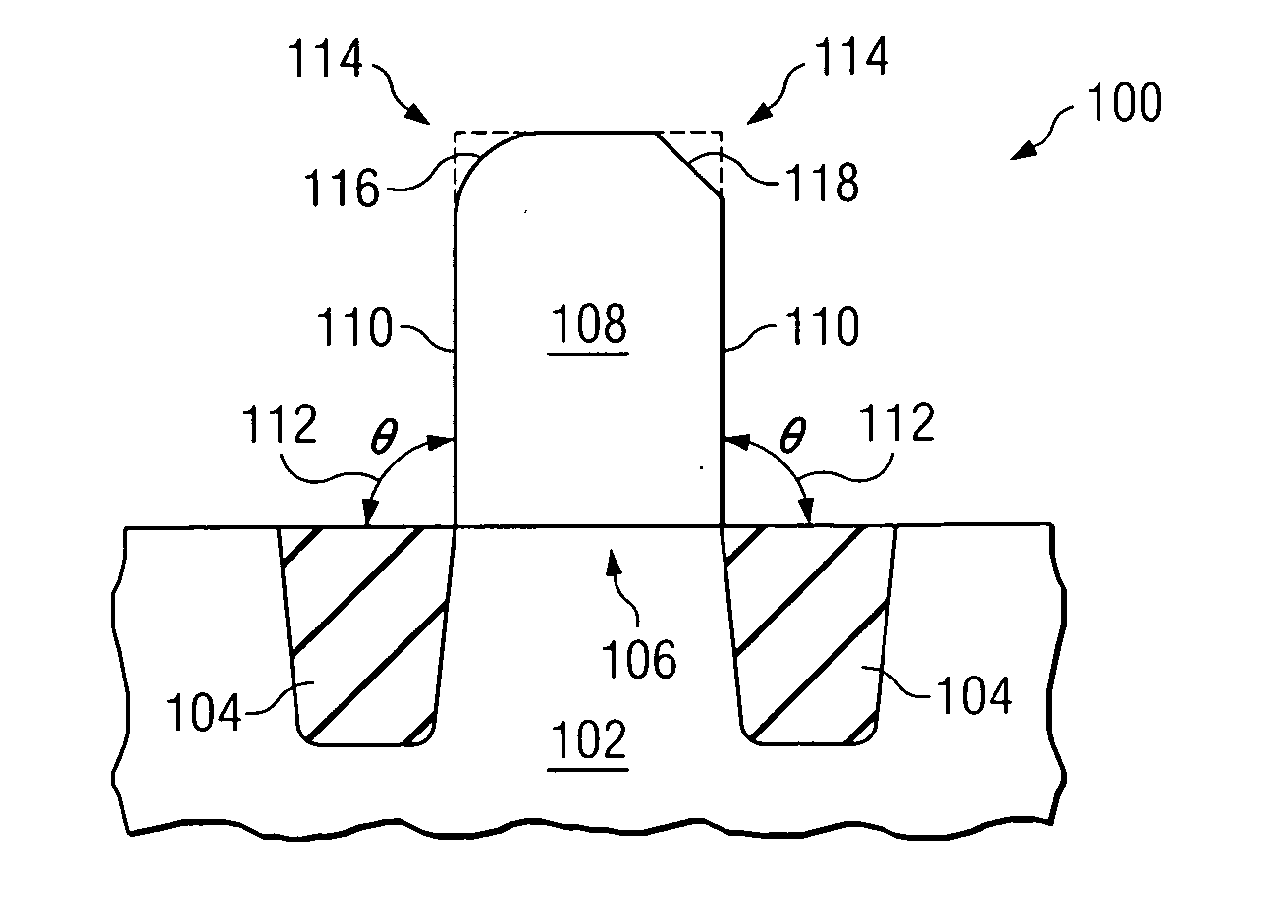

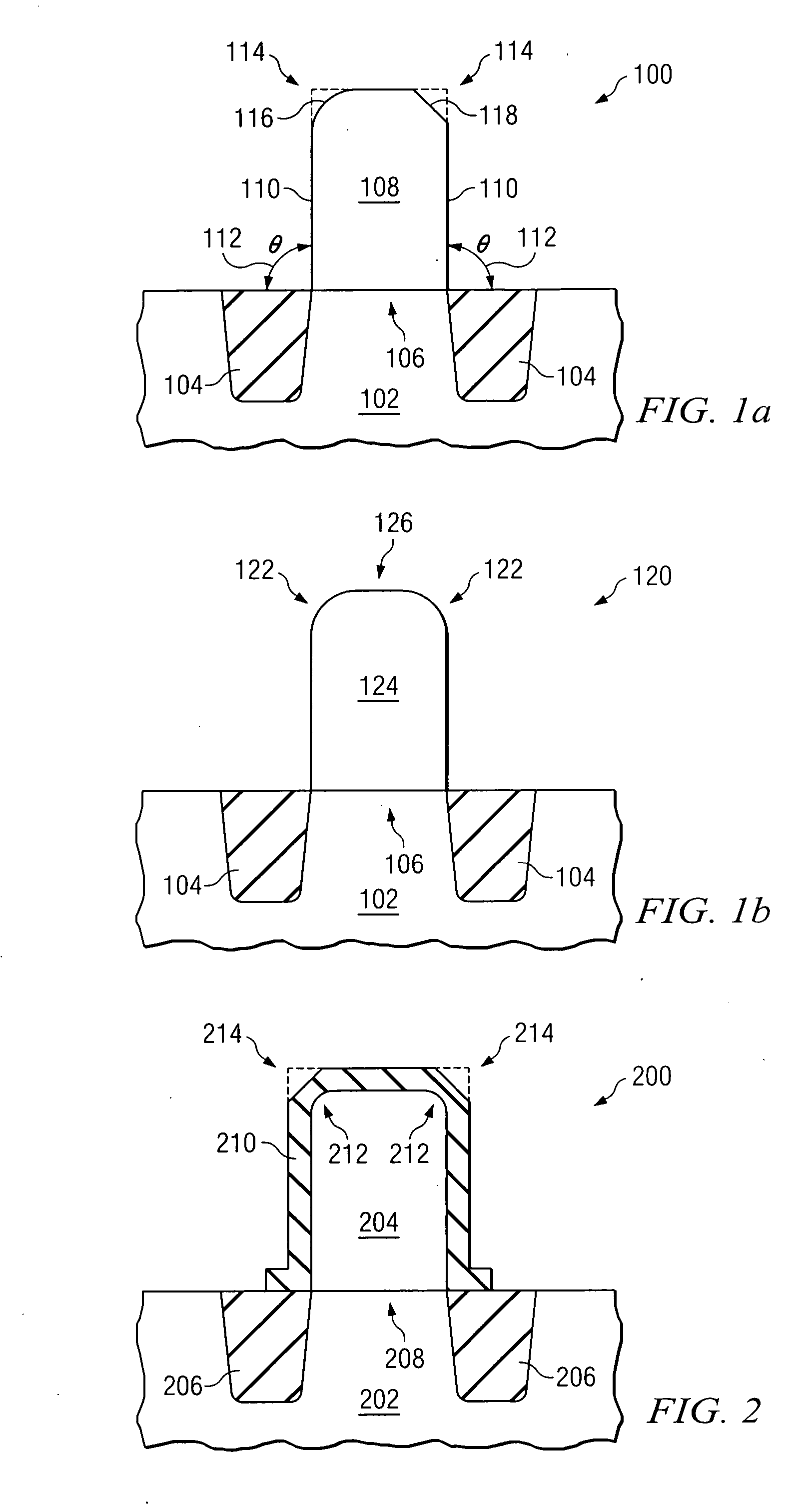

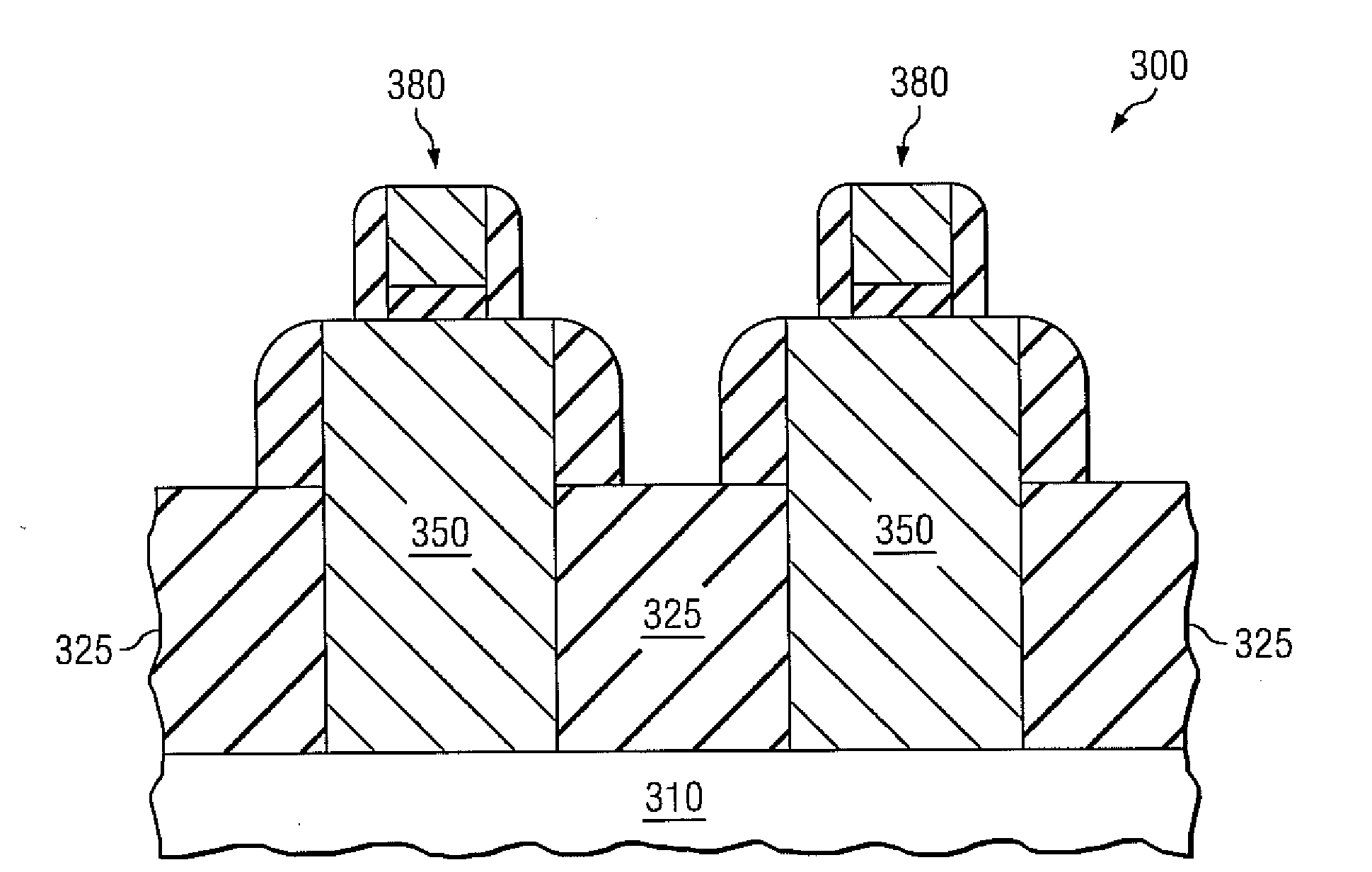

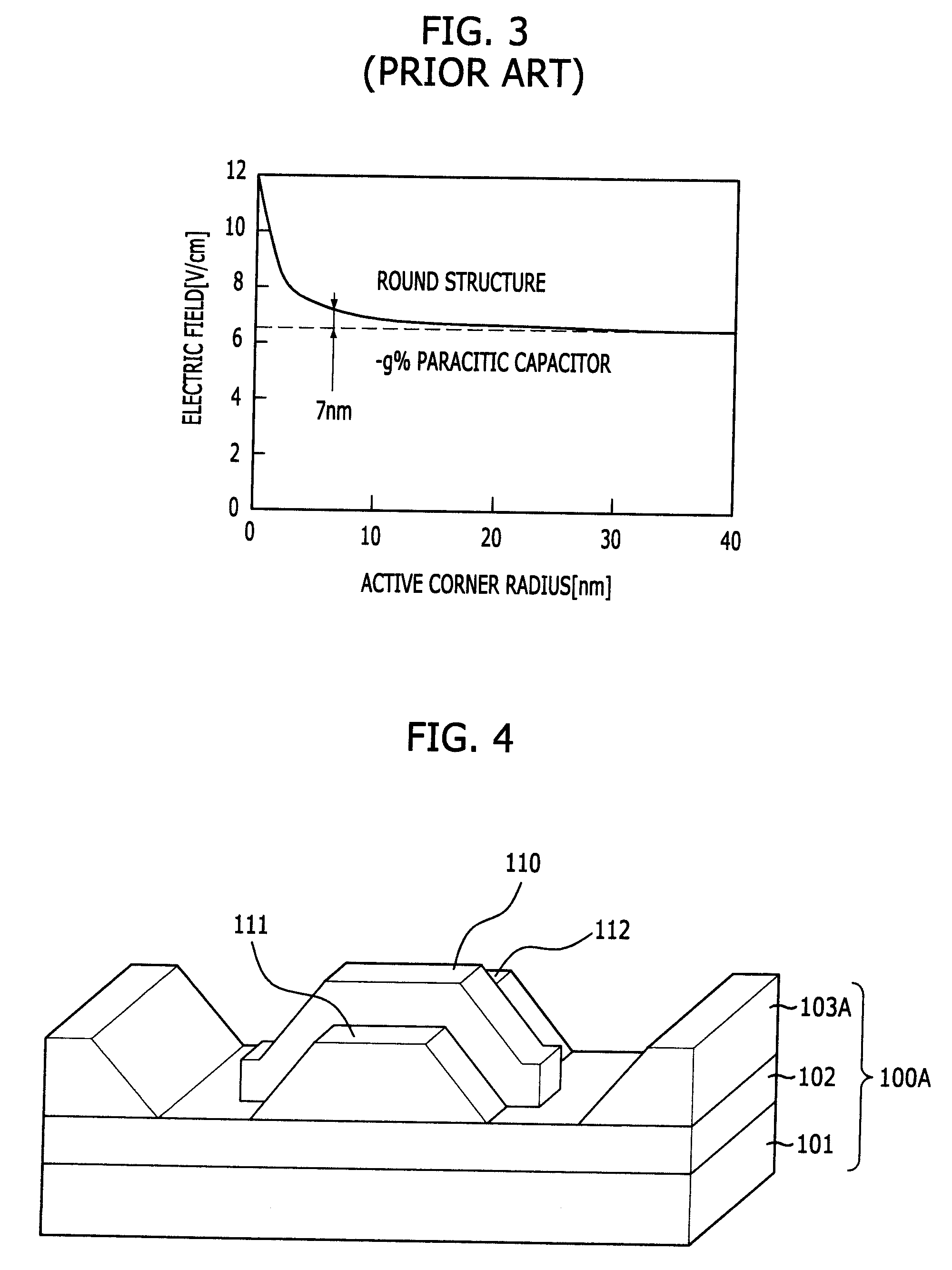

Versatile system for triple-gated transistors with engineered corners

ActiveUS6969644B1Readily implemented in and adaptableImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody areaSeparation relation

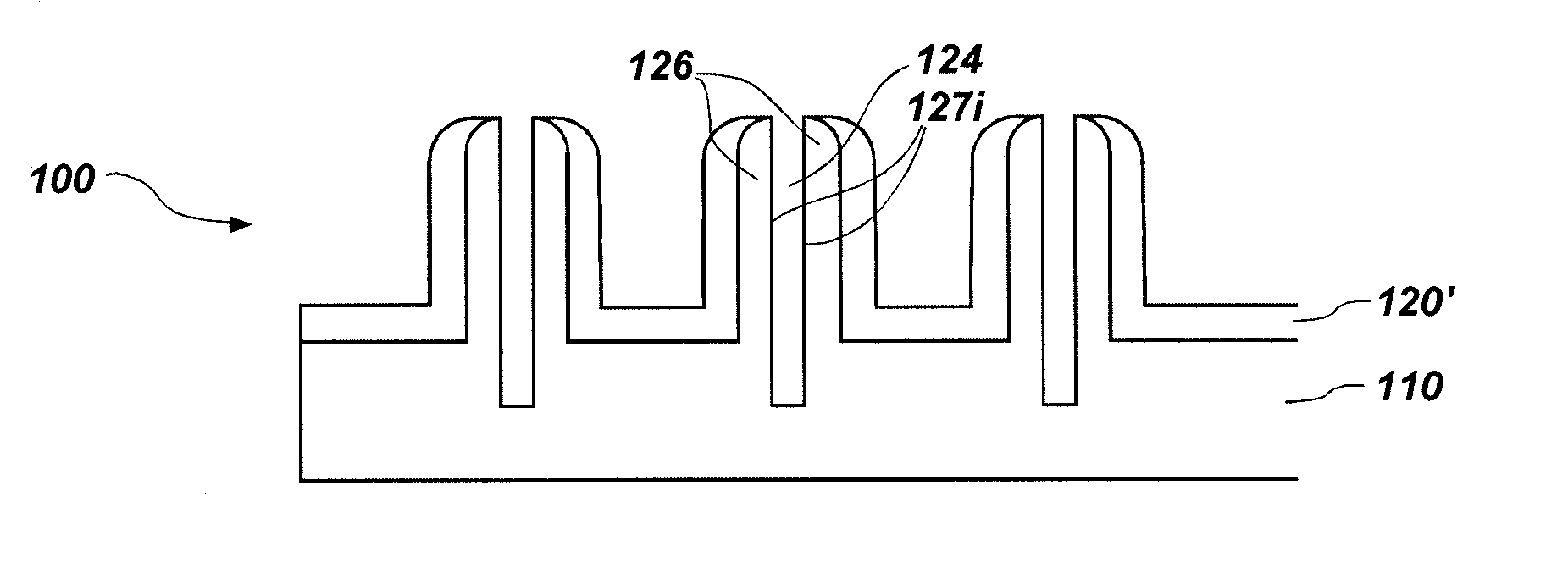

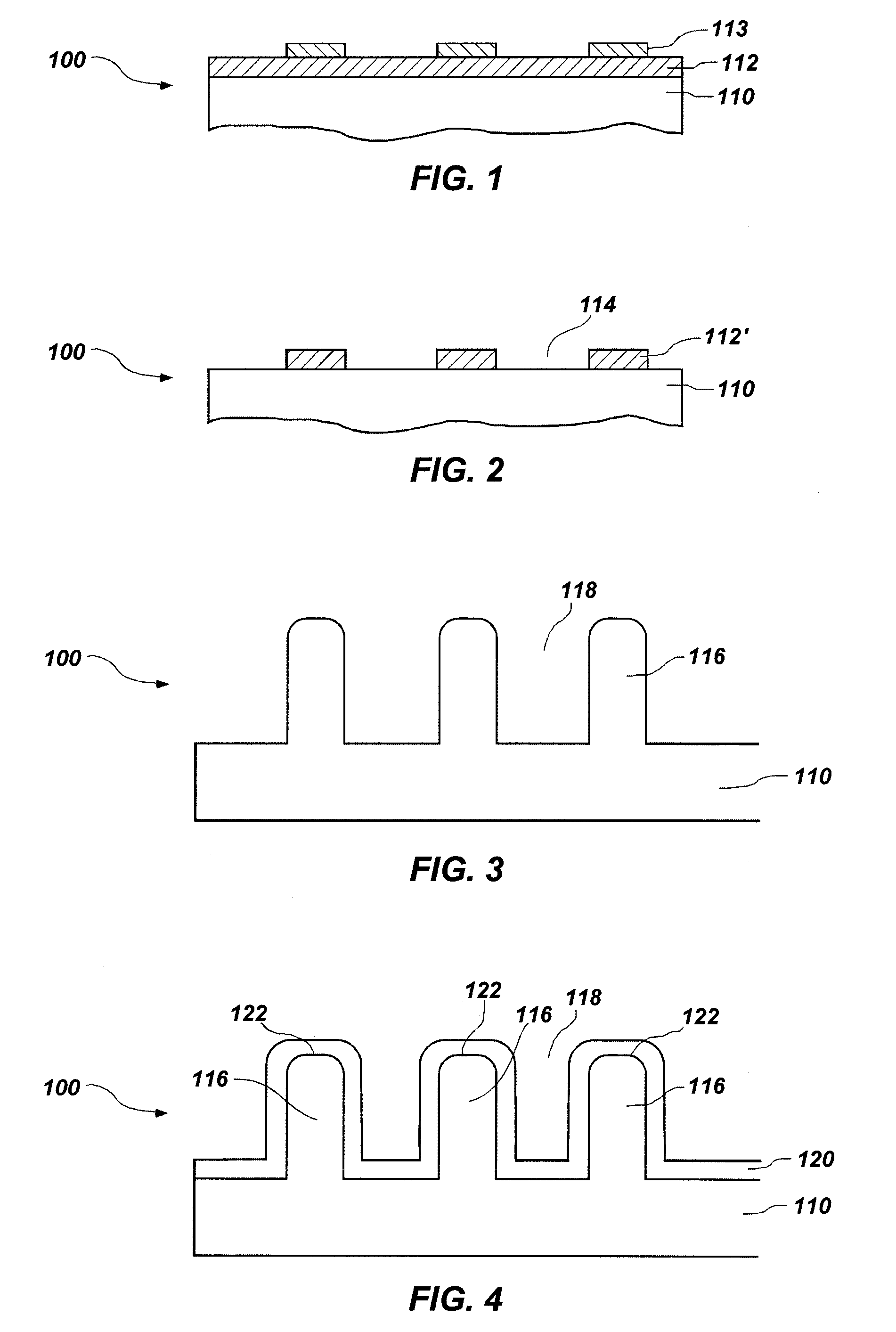

The present invention provides a system for producing a triple-gate transistor segment (300), utilizing a standard semiconductor substrate (302). The substrate has a plurality of isolation regions (304) formed along its upper surface in a distally separate relationship, defining a channel region (306). A form structure (308) is disposed atop the isolation regions, and defines a channel body area (310) over the channel region. A channel body structure (316) is disposed within the channel body area, and is engineered to provide a blunted corner or edge (318) along a perimeter of its upper exposed surface. The form structure is then removed, and subsequent processing is performed.

Owner:TEXAS INSTR INC

Method of integrating triple gate oxide thickness

ActiveUS7410874B2Reduce formationLower areaSemiconductor/solid-state device manufacturingOptoelectronicsGate oxide

A method for forming TGO structures includes providing a substrate containing regions of first, second and third kinds in which devices with respective first, second and third gate oxide layers of different thicknesses are to be formed. The second gate oxide layer is formed over the substrate and then removed from regions of the first kind where the first gate oxide layer is subsequently grown. A first conductive layer is deposited over the substrate. The first conductive layer and second gate oxide layer are subsequently removed from regions of the third kind. The third gate oxide layer followed by deposition of a second conductive layer is formed over the substrate and then removed except from over regions of the third kind.

Owner:TAIWAN SEMICON MFG CO LTD

Versatile system for triple-gated transistors with engineered corners

ActiveUS20060043524A1Readily implemented in and adaptableImprove performanceTransistorSemiconductor/solid-state device manufacturingBody areaEngineering

The present invention provides a system for producing a triple-gate transistor segment (300), utilizing a standard semiconductor substrate (302). The substrate has a plurality of isolation regions (304) formed along its upper surface in a distally separate relationship, defining a channel region (306). A form structure (308) is disposed atop the isolation regions, and defines a channel body area (310) over the channel region. A channel body structure (316) is disposed within the channel body area, and is engineered to provide a blunted corner or edge (318) along a perimeter of its upper exposed surface. The form structure is then removed, and subsequent processing is performed.

Owner:TEXAS INSTR INC

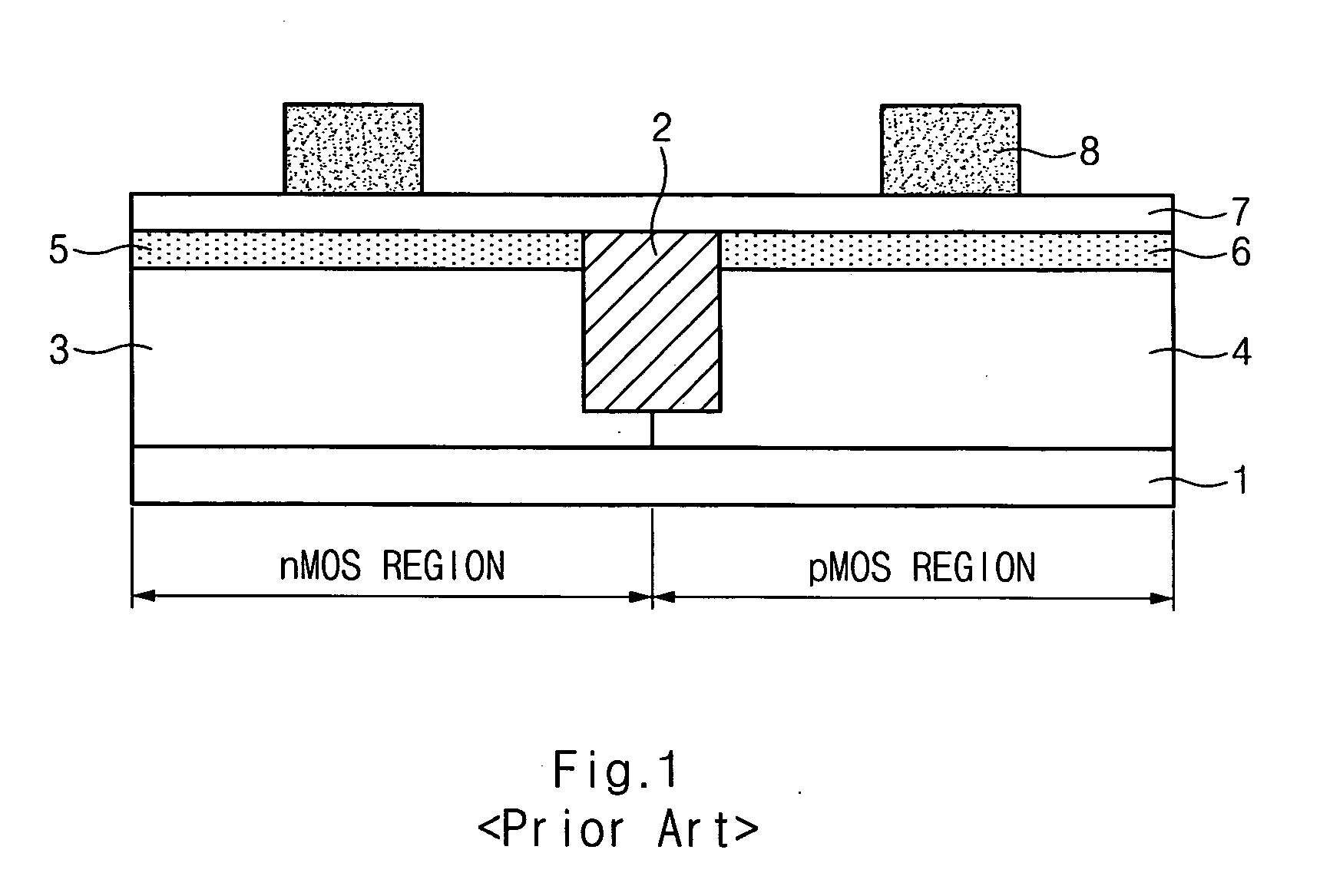

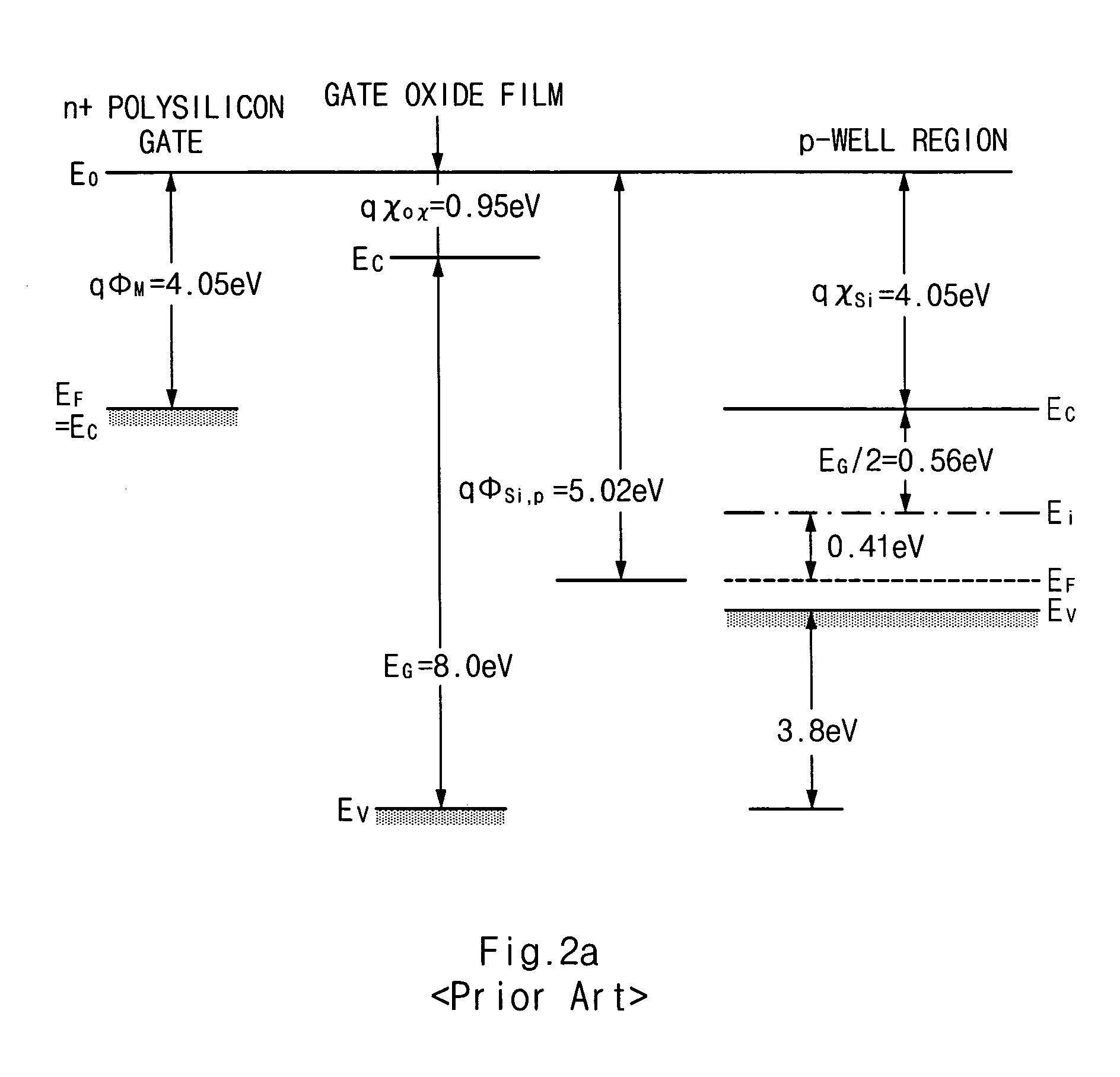

Flash memory cell transistor and method for fabricating the same

A flash memory cell transistor and a method for fabricating the same compensates a work function difference of a MOS and a nMOS with a triple gate insualting film by using electron density trapped in a pMOS gate insulating film. The flash memory cell transistor comprises a p-well region and a n-well region. The nMOS region comprises a nMOS channel ion-implantation region on the p-well region, a second gate oxide film on the nMOS channel ion-implantation region and a first n+ polysilicon gate electrode on the second gate oxide film. The pMOS region comprises a MOS channel ion-implantation region on the n-well region, a first gate oxide film, an insulating film having an electron trap and the second gate oxide film which are sequentially formed on the PMOS channel ion-implantation region, and a second n+ polysilicon gate electrode on the second gate oxide film.

Owner:SK HYNIX INC

Structure and method for a triple-gate transistor with reverse sti

ActiveUS20080268599A1Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDielectric layer

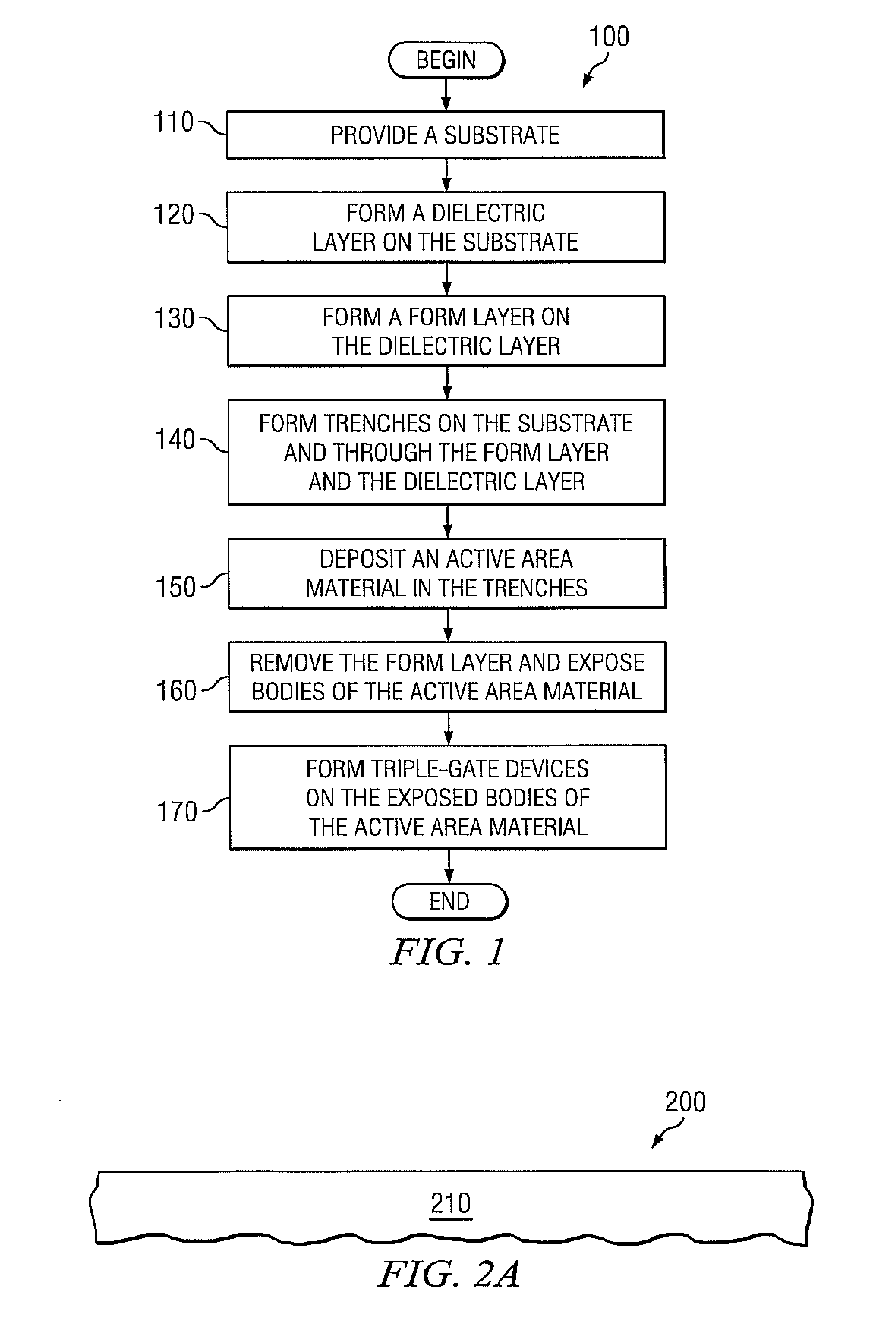

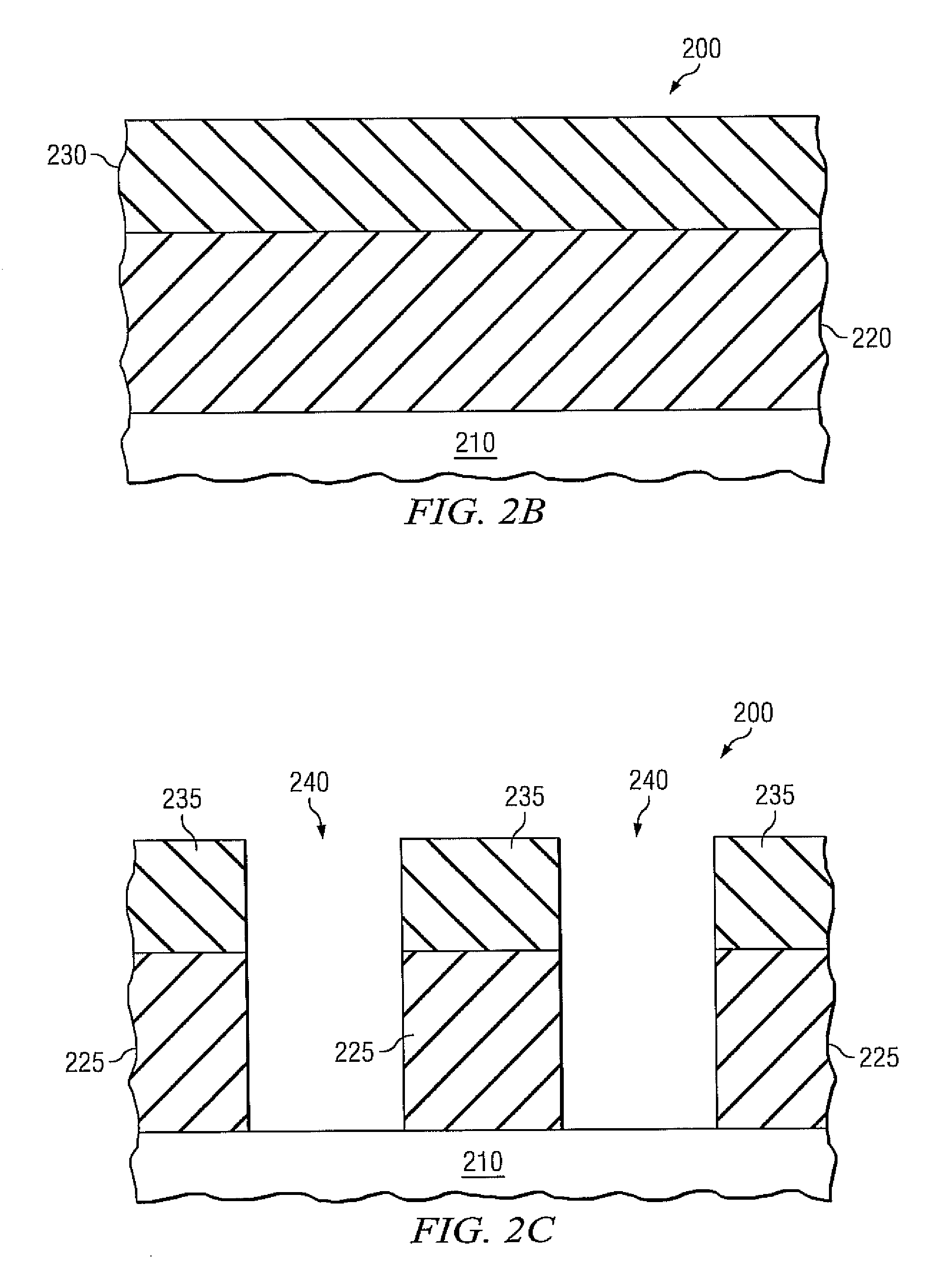

Exemplary embodiments provide triple-gate semiconductor devices isolated by reverse STI structures and methodologies for their manufacture. In an exemplary process, stacked layers including a form layer over a dielectric layer can be formed over a semiconductor substrate. One or more trenches can be formed by etching through the stacked layers. The one or more trenches can be filled by an active area material to form one or more active areas, which can be isolated by remaining portions of the dielectric layer. Bodies of the active area material can be exposed by removing the form layer. One or more triple-gate devices can then be formed on the exposed active area material. The exemplary triple-gate semiconductor devices can control the dimensions for the active areas and provide less isolation spacing between the active areas, which optimizes manufacturing efficiency and device integration quality.

Owner:TEXAS INSTR INC

Methods of fabricating dual fin structures

ActiveUS7902057B2Semiconductor/solid-state device manufacturingSemiconductor devicesElectronic systemsEngineering

Fin-FET devices and methods of fabrication are disclosed. The Fin-FET devices include dual fins that may be used to provide a trench region between a source region and a drain region. In some embodiments, the dual fins may be formed by forming a trench with fin structures on opposite sides in a protruding region of a substrate. The dual fins may be useful in forming single-gate, double-gate or triple-gate fin-FET devices. Electronic systems including such fin-FET devices are also disclosed.

Owner:MICRON TECH INC

Double and triple gate mosfet devices and methods for making same

InactiveUS20120252193A1TransistorSemiconductor/solid-state device manufacturingField-effect transistorDouble gate

A double gate metal-oxide semiconductor field-effect transistor (MOSFET) includes a fin, a first gate and a second gate. The first gate is formed on top of the fin. The second gate surrounds the fin and the first gate. In another implementation, a triple gate MOSFET includes a fin, a first gate, a second gate, and a third gate. The first gate is formed on top of the fin. The second gate is formed adjacent the fin. The third gate is formed adjacent the fin and opposite the second gate.

Owner:ADVANCED MICRO DEVICES INC

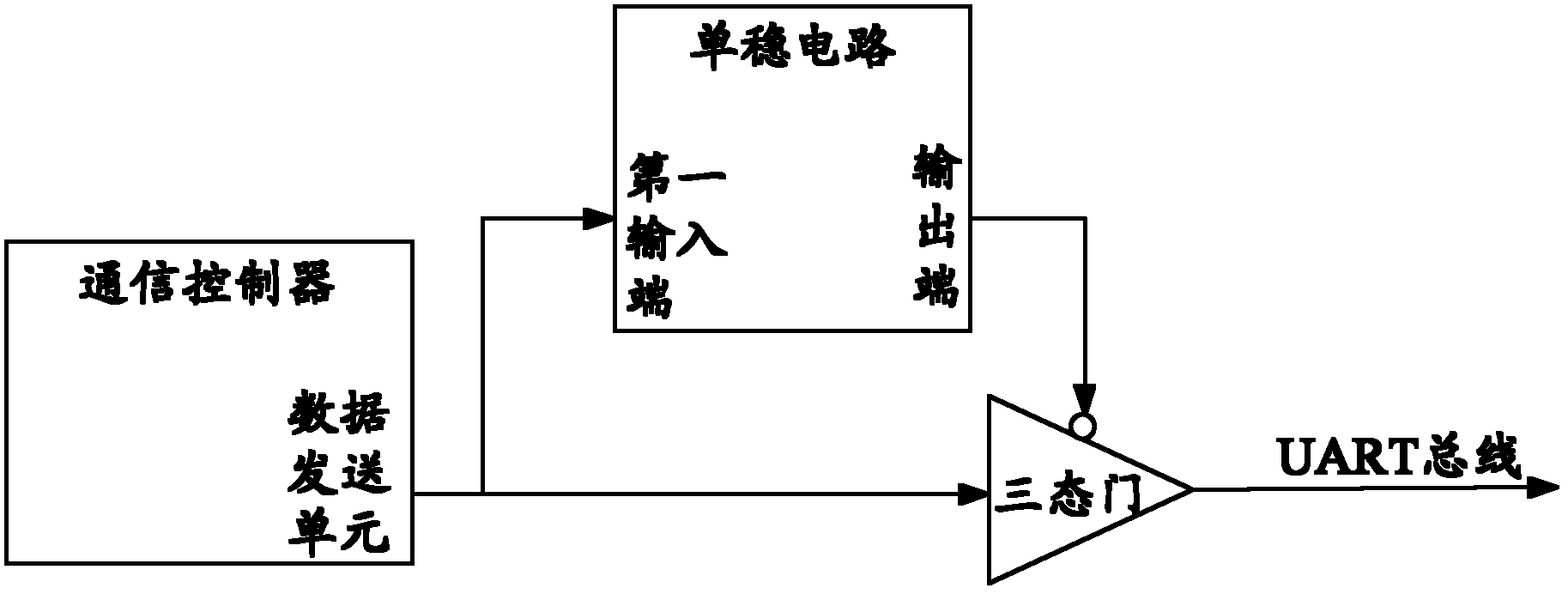

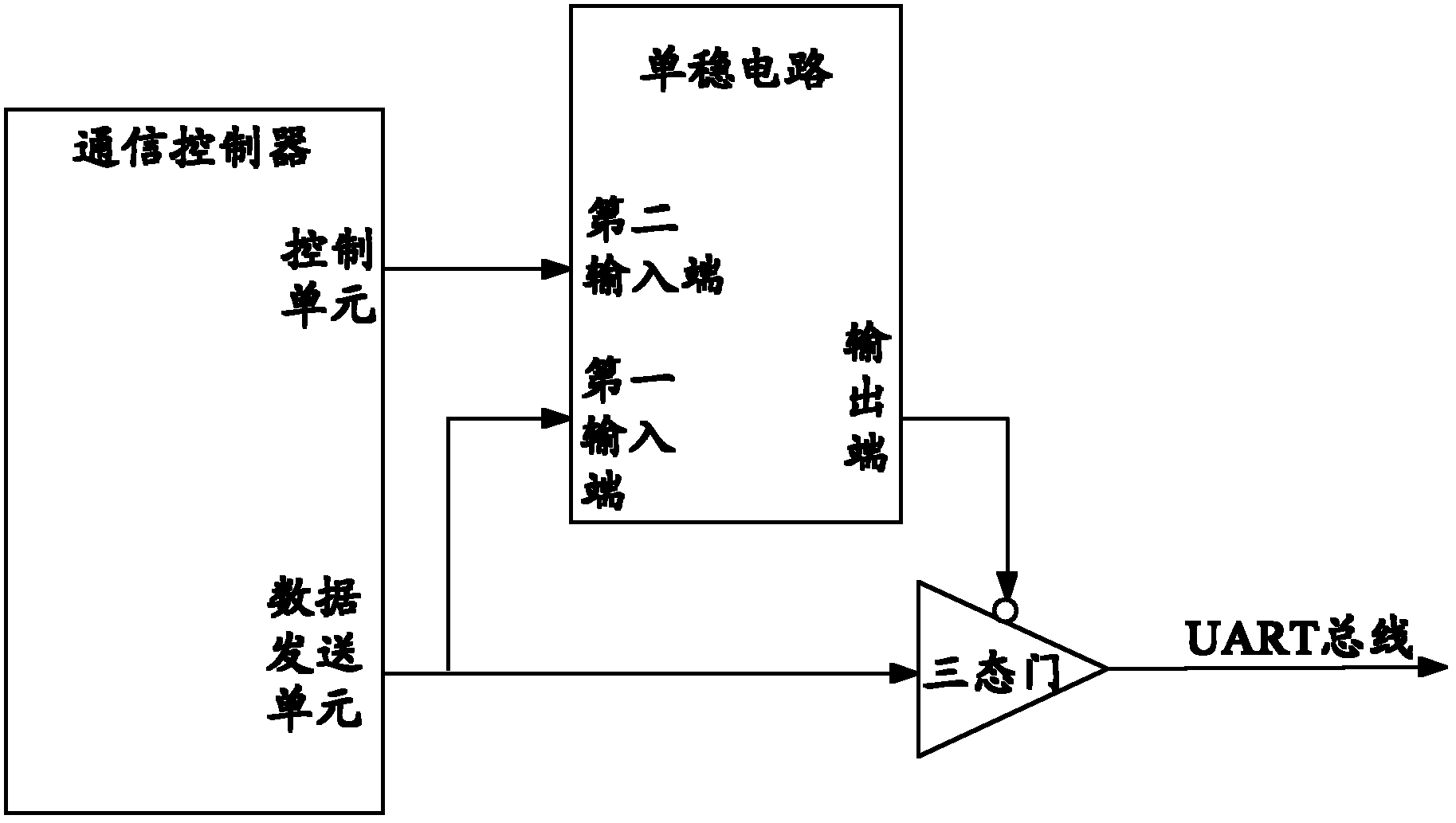

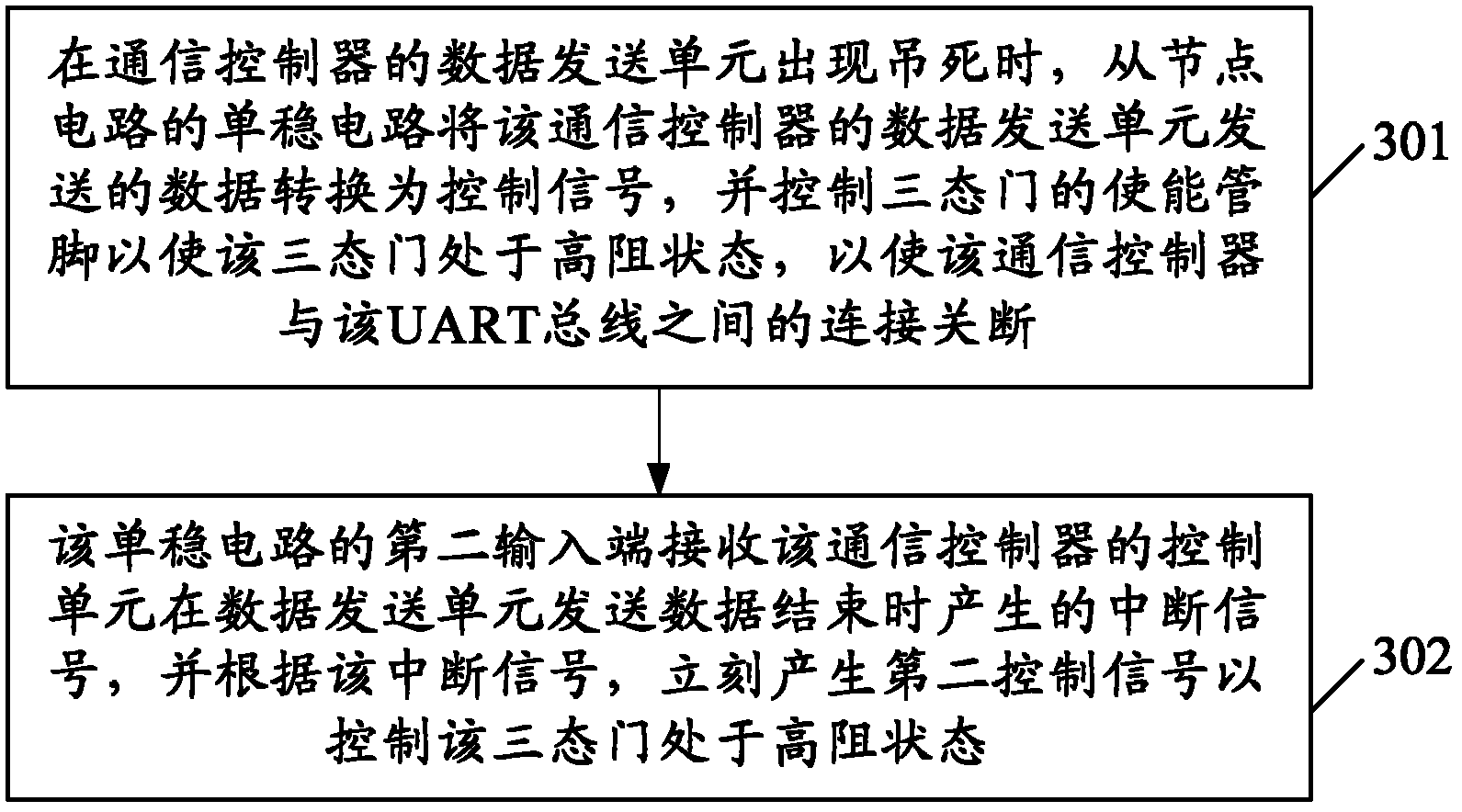

Slave node circuit, communication method and communication device

ActiveCN102609388AGuaranteed normal transmissionPrevent hangingElectric digital data processingCommunication controlData transmission

The invention discloses a slave node circuit, a communication method and a communication device, relating to the communication field. The slave node circuit, the communication method and the communication device are used for preventing a bus from hanging so as to guarantee normal data transmission, wherein the slave node circuit is located between a data sending unit and a universal asynchronism receiver transmitter (UART) bus; the slave node circuit comprises a triple gate and a monostable circuit; an input end of the triple gate is connected with the data sending unit; an output end of the triple gate is connected with the UART bus; the triple gate is used for controlling connection state of the communication controller and the UART bus; the monostable circuit comprises a first input end and an output end; the first input end of the monostable circuit is connected with the data sending unit; the output end of the monostable circuit is connected with an enabling end of the triple gate.

Owner:HUAWEI DIGITAL POWER TECH CO LTD

Double and triple gate MOSFET devices and methods for making same

InactiveUS8580660B2TransistorSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

Owner:ADVANCED MICRO DEVICES INC

Method for forming gate of semiconductor device

ActiveUS20090311854A1Preventing characteristic and reliabilityAvoid electric field concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerSemiconductor

A method for forming a triple gate of a semiconductor device is provided. The method includes: forming a buffer layer and a hard mask over a substrate; etching the hard mask and the buffer layer to form a hard mask pattern and a buffer pattern; forming first and second trenches spaced apart within the substrate by partially etching the substrate by a vapor etching process using the hard mask pattern as an etching barrier layer; forming a buried insulation layer to fill the first and second trenches; removing the hard mask pattern and the buffer pattern; forming a gate insulation layer over the substrate between the first trench and the second trench; forming a conductive layer to cover the gate insulation layer; and etching the conductive layer to form a gate electrode.

Owner:KEY FOUNDRY CO LTD

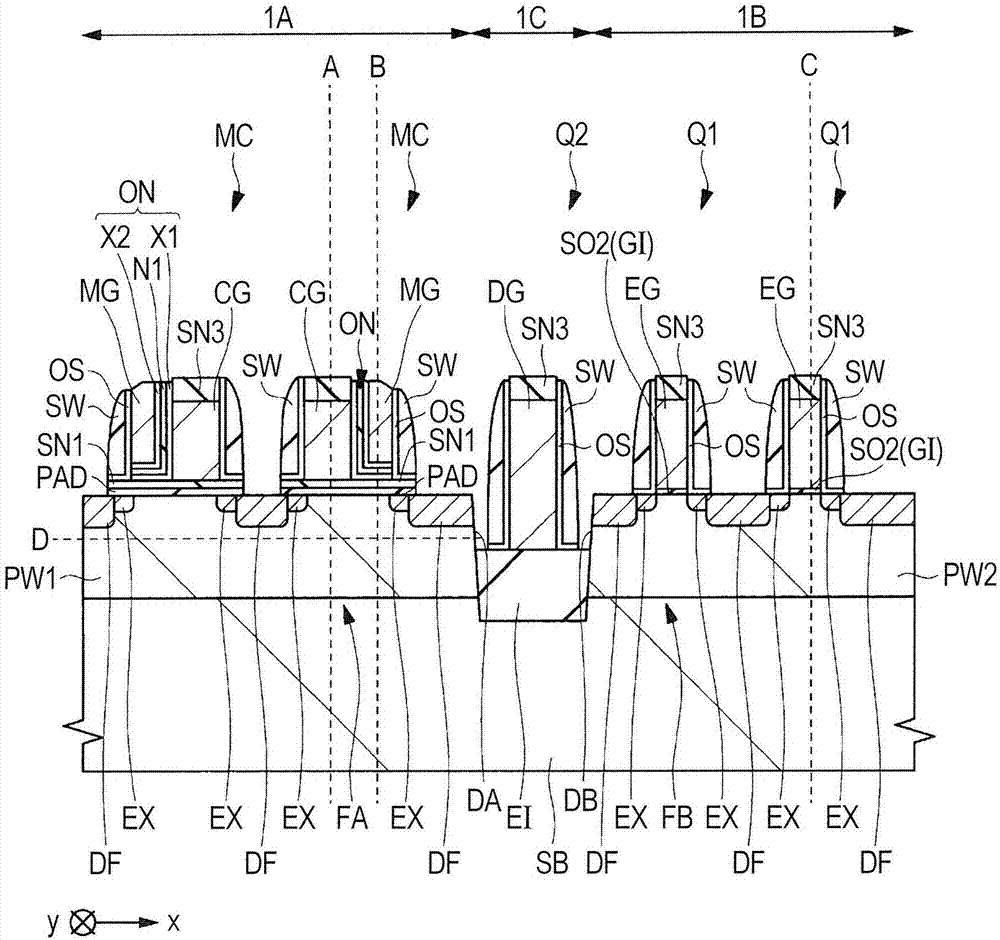

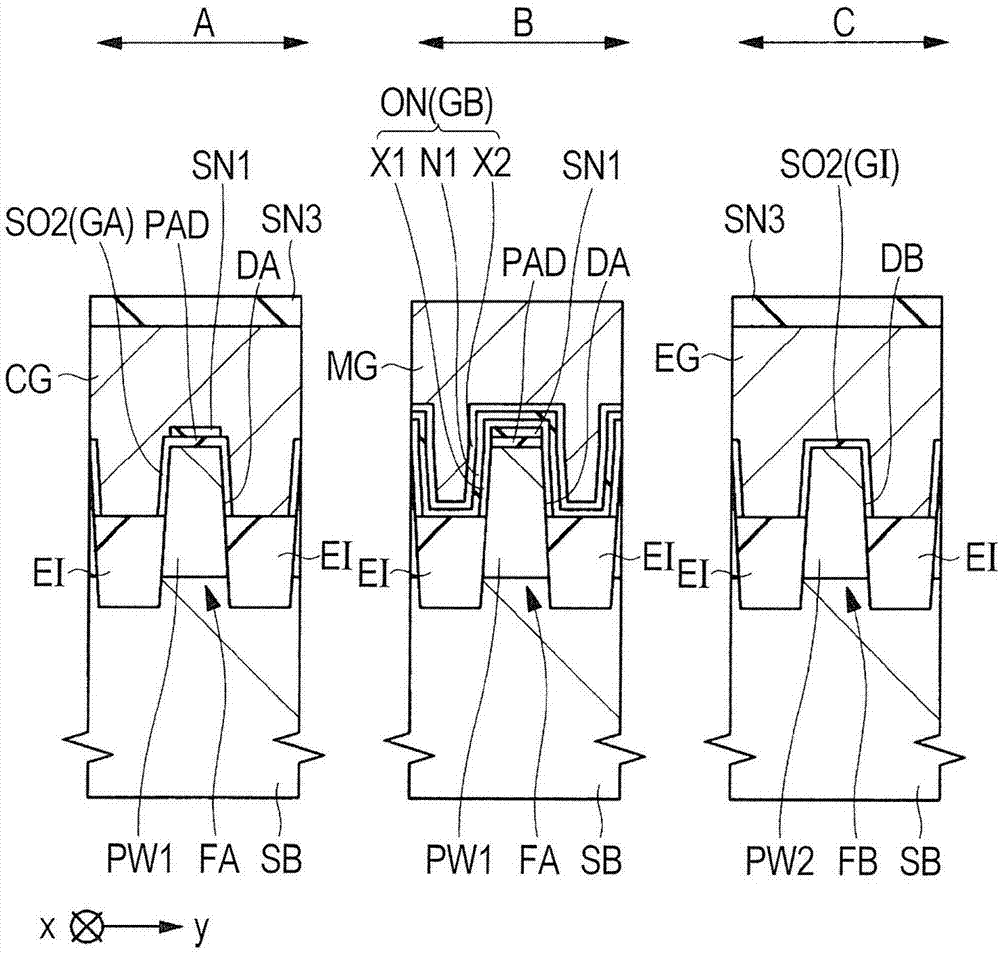

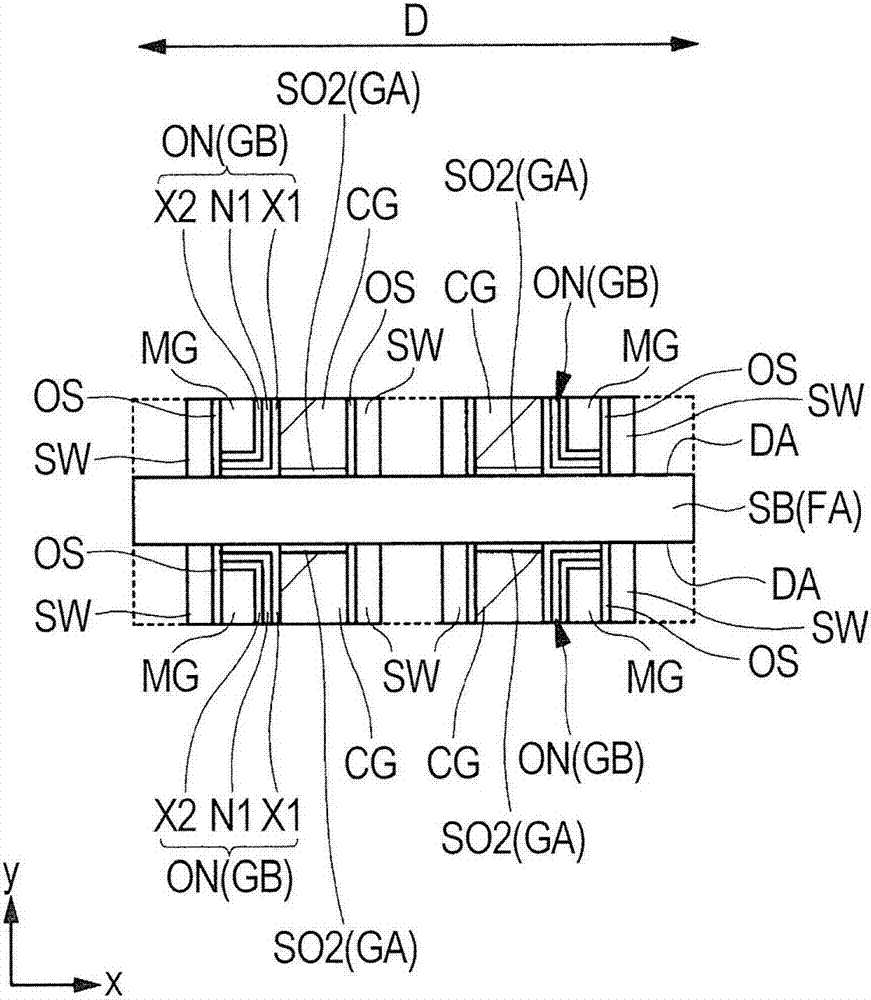

Semiconductor device and manufacturing method of the same

InactiveCN107464815AImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

To improve reliability of a semiconductor device, a control transistor and a memory transistor formed in a memory cell region are configured to have a double-gate structure, and a transistor formed in a peripheral circuit region is configured to have a triple-gate structure. For example, in the memory transistor, a gate insulating film formed by an ONO film is provided between a memory gate electrode and sidewalls of a fin, and an insulating film (a stacked film of a multilayer film of an insulating film / an oxide film and the ONO film) thicker than the ONO film is provided between the memory gate electrode and a top surface of the fin. This configuration can reduce concentration of an electric field onto a tip of the fin, so that deterioration of reliability of the ONO film can be prevented.

Owner:RENESAS ELECTRONICS CORP