Buffer based on source electrode follower

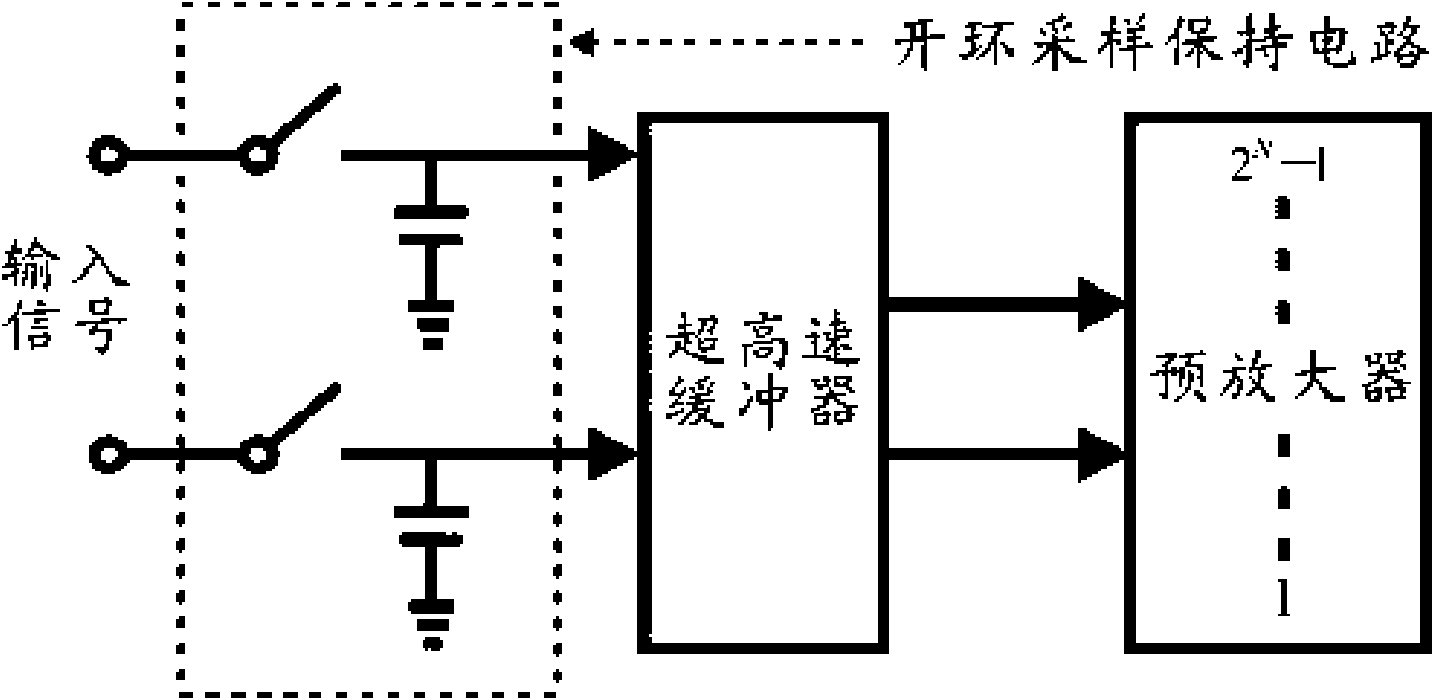

A source follower and buffer technology, applied in amplifiers with impedance circuits, logic circuits using dielectric elements, logic circuits using specific components, etc., can solve the problem of large analog input signal loss, small signal gain, Problems such as poor dynamic performance, to achieve the effect of high unity gain buffer output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

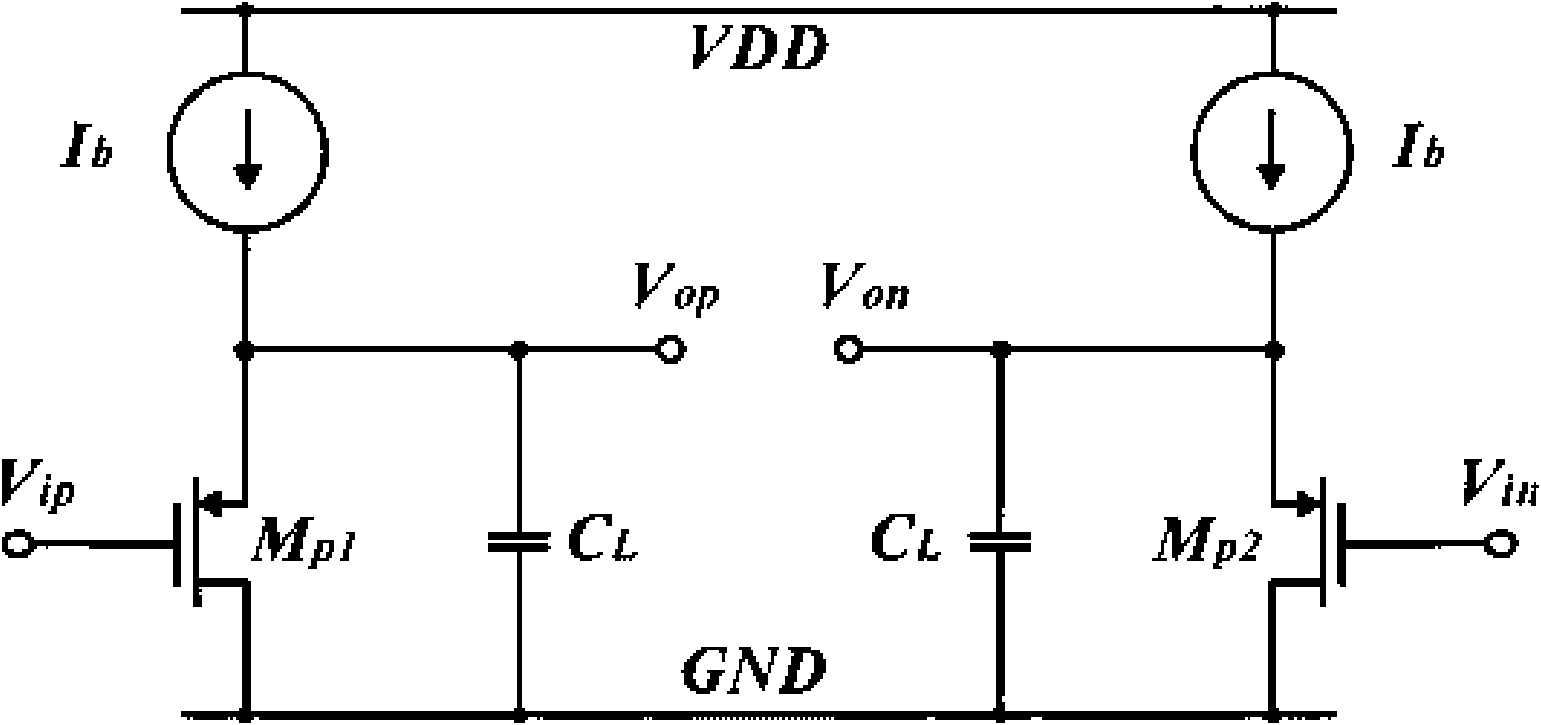

[0032] see Figure 4 , an embodiment of the present invention provides a buffer based on a source follower, the buffer includes:

[0033] a pseudo-differential input stage for receiving a differential input signal;

[0034] A cross-coupled common-source stage connected to a pseudo-differential input stage to form a negative resistance to cancel out the output resistance of the buffer;

[0035] a current source coupled to the pseudo-differential input stage for providing buffer branch current;

[0036] A capacitive load, connected to the pseudo-differential input stage, is used as an output load for the buffer.

[0037] Wherein, the pseudo-differential input stage includes a first PMOS transistor 110 (Mp1) and a second PMOS transistor 111 (Mp2); the drain of the first PMOS transistor 110 is connected to the ground voltage GND (141), and the gate of the first PMOS transistor 110 is connected to the second PMOS transistor 110. An input terminal 102 (Vip), the source and substr...

Embodiment 2

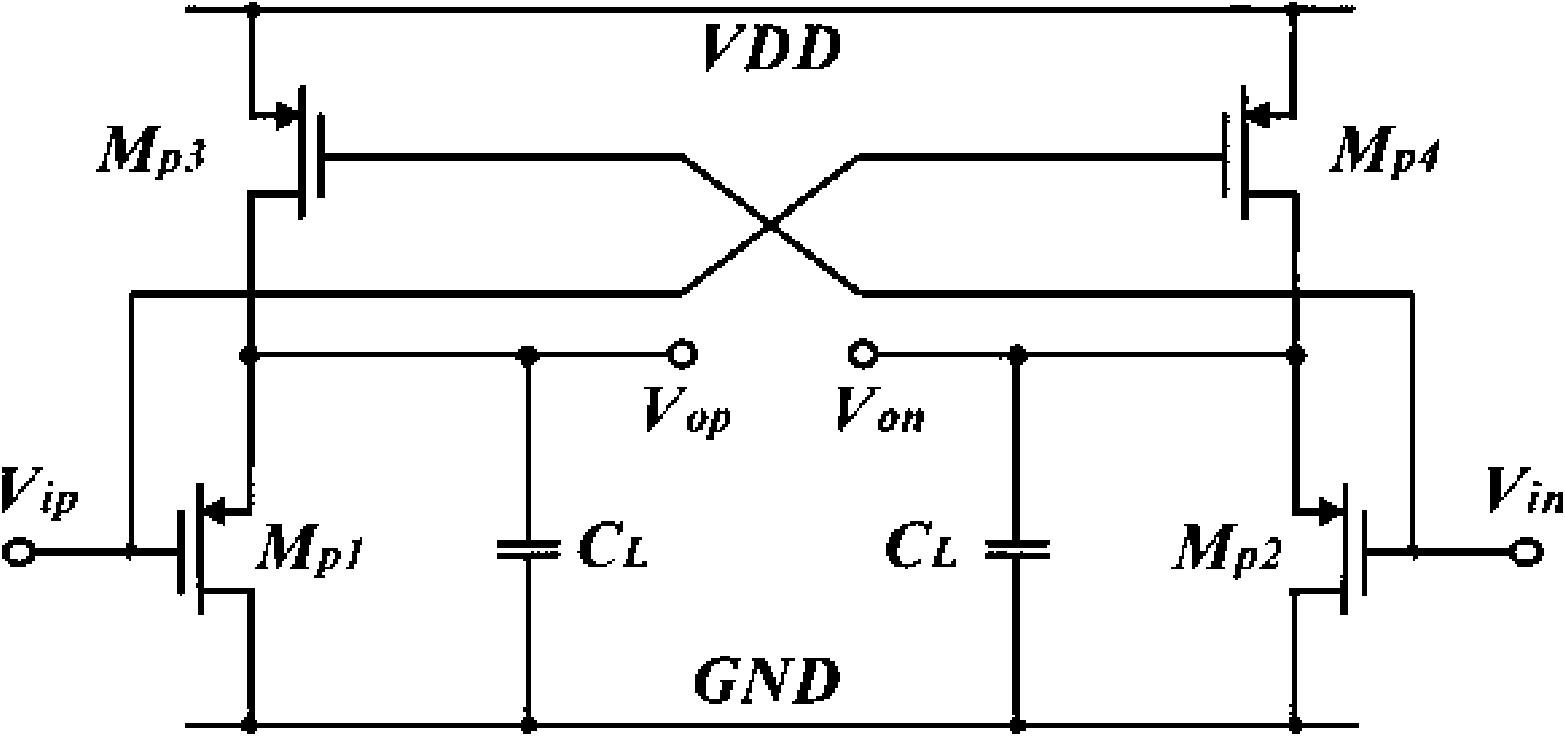

[0043] see Figure 5 , the embodiment of the present invention also provides another buffer based on a source follower, and the buffer includes:

[0044] a pseudo-differential input stage for receiving a differential input signal;

[0045]A cross-coupled common-source stage connected to a pseudo-differential input stage to form a negative resistance to cancel out the output resistance of the buffer;

[0046] a current source coupled to the pseudo-differential input stage for providing buffer branch current;

[0047] A capacitive load, connected to the pseudo-differential input stage, is used as an output load for the buffer.

[0048] Wherein, the pseudo-differential input stage includes a first PMOS transistor 210 (Mp1) and a second PMOS transistor 211 (Mp2); the drain of the first PMOS transistor 210 is connected to the ground voltage GND (241), and the gate of the first PMOS transistor 210 is connected to the second PMOS transistor 210. An input terminal 202 (Vip), the so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More