High efficiency storing method for coding digit of LDPC coder based on FPGA

A decoder and codeword technology, applied in the field of decoding codeword storage, can solve the problems of occupying decoding throughput and not being able to meet high-speed data transmission, so as to reduce critical path delay, improve storage resource utilization, reduce The effect of storage resource quantity requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

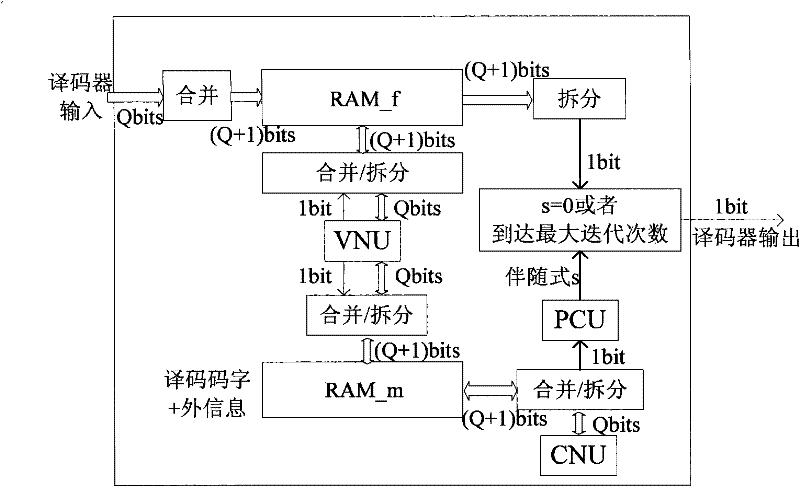

[0046] Such as figure 1 Shown, the present invention a kind of high-efficiency storage method of the decoded code word based on the LDPC decoder of FPGA, described LDPC decoder structure comprises the storage block RAM_f that storage bit width is (Q+1)bits and RAM_m , variable node processing unit VNU, check node processing unit CNU, check equation calculation unit PCU; method steps are as follows:

[0047] (1) Initialization: the decoder expands the received channel information with a bit width of Q bits into (Q+1) bits (the upper bits are complemented with '0' or complemented with '1' through the merging unit) and stored in RAM_f, and the RAM_m is initialized to all zeros, the number of initialization iterations iter=0, the maximum number of iterations iter=MAX_ITER;

[0048] (2) Update of variable nodes: a) Read (Q+1) bits of data A and B from memory blocks RAM_f and RAM_m respectively; b) Split data A and B into Q bits of data (A and The low Q bits of B are represented b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More