Realization method for improving chip yield

A realization method and a technology of yield rate, applied in the field of structural design and implementation to improve chip yield, can solve problems such as cost loss, increase design, verification, and test cycles, and achieve the effects of improving yield rate, balanced configuration, and high technical value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

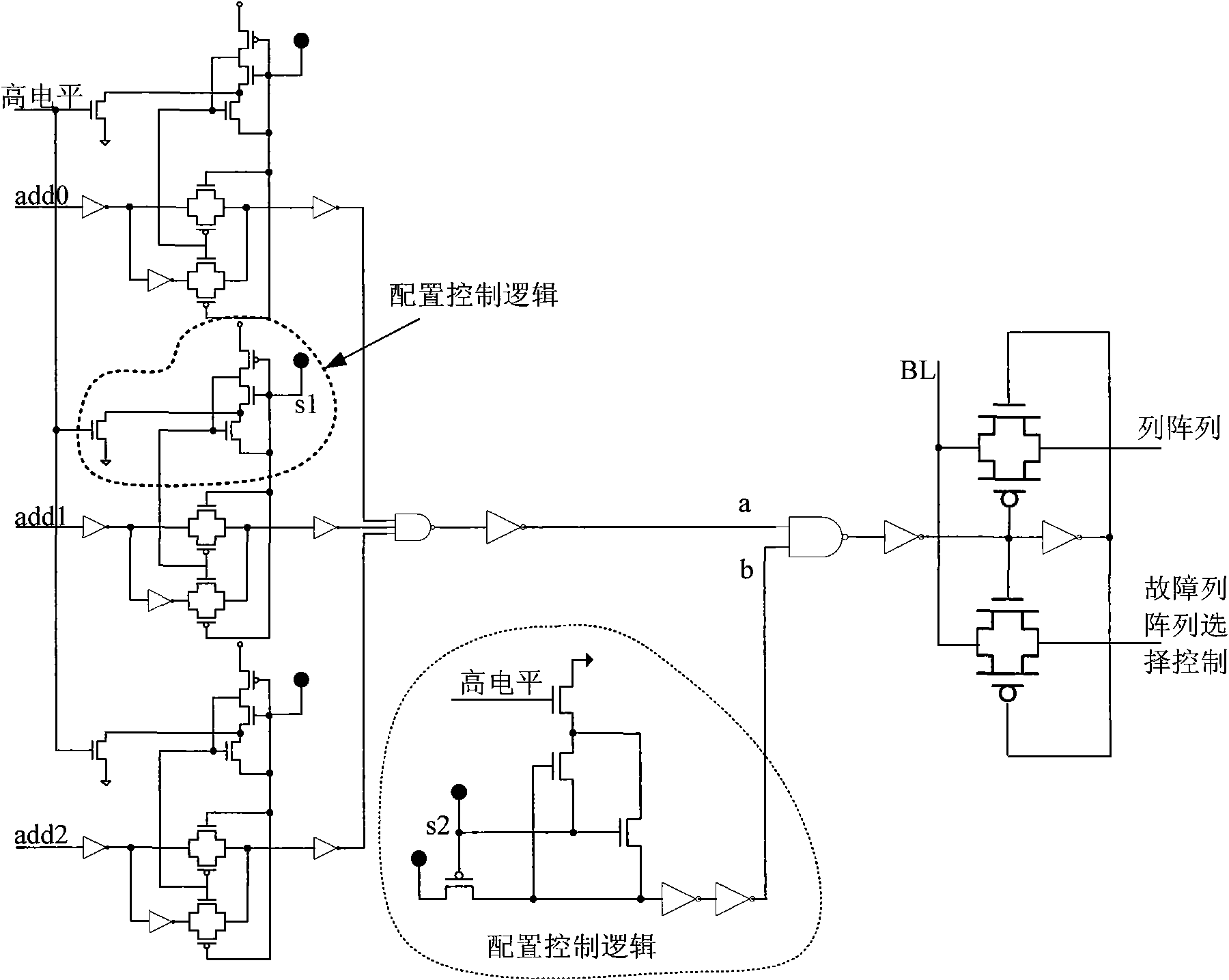

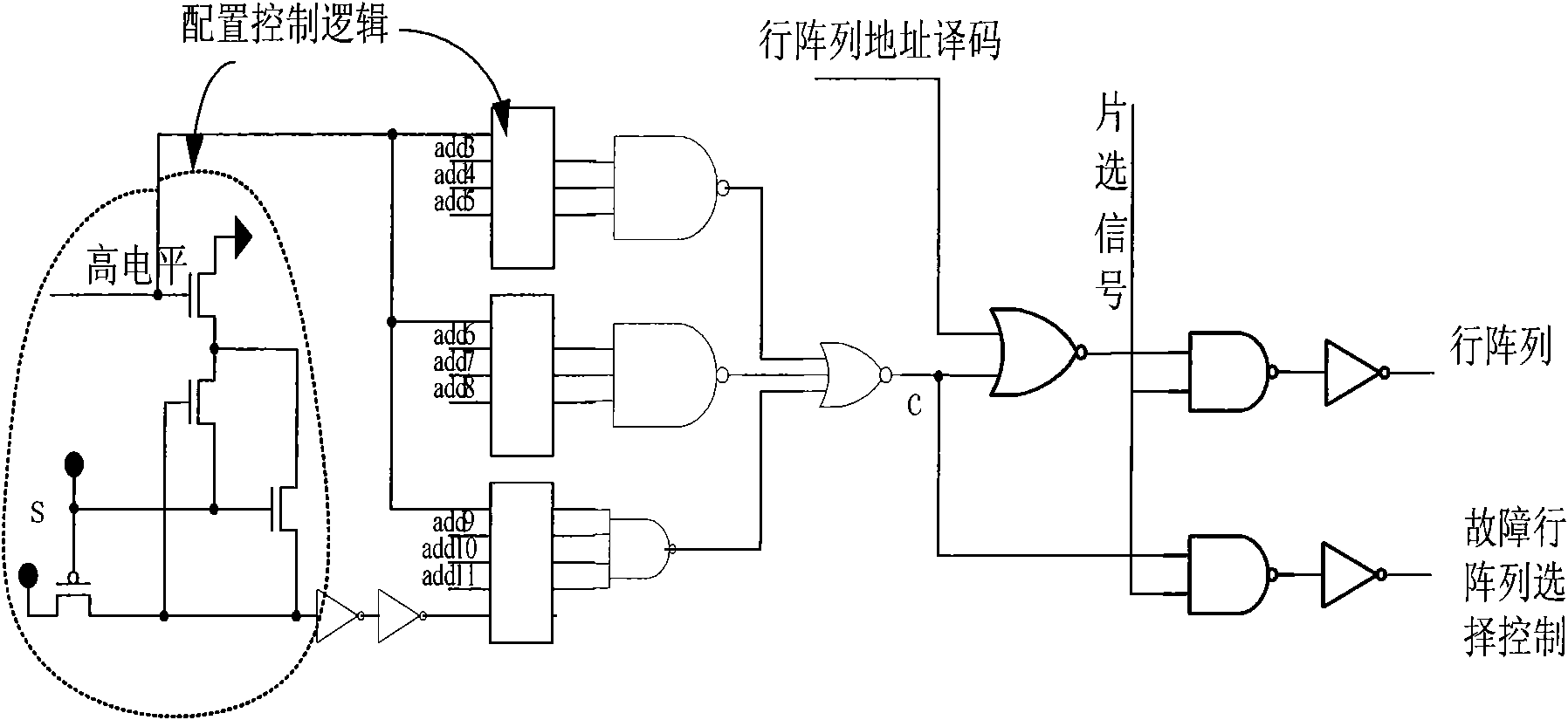

[0016] The method for repairing the defects of the storage array in the present invention mainly includes: a storage array column unit fault repairing method, a storage array row unit repairing method, a fuse control efficient implementation method, and a redundant array dynamic expansion method.

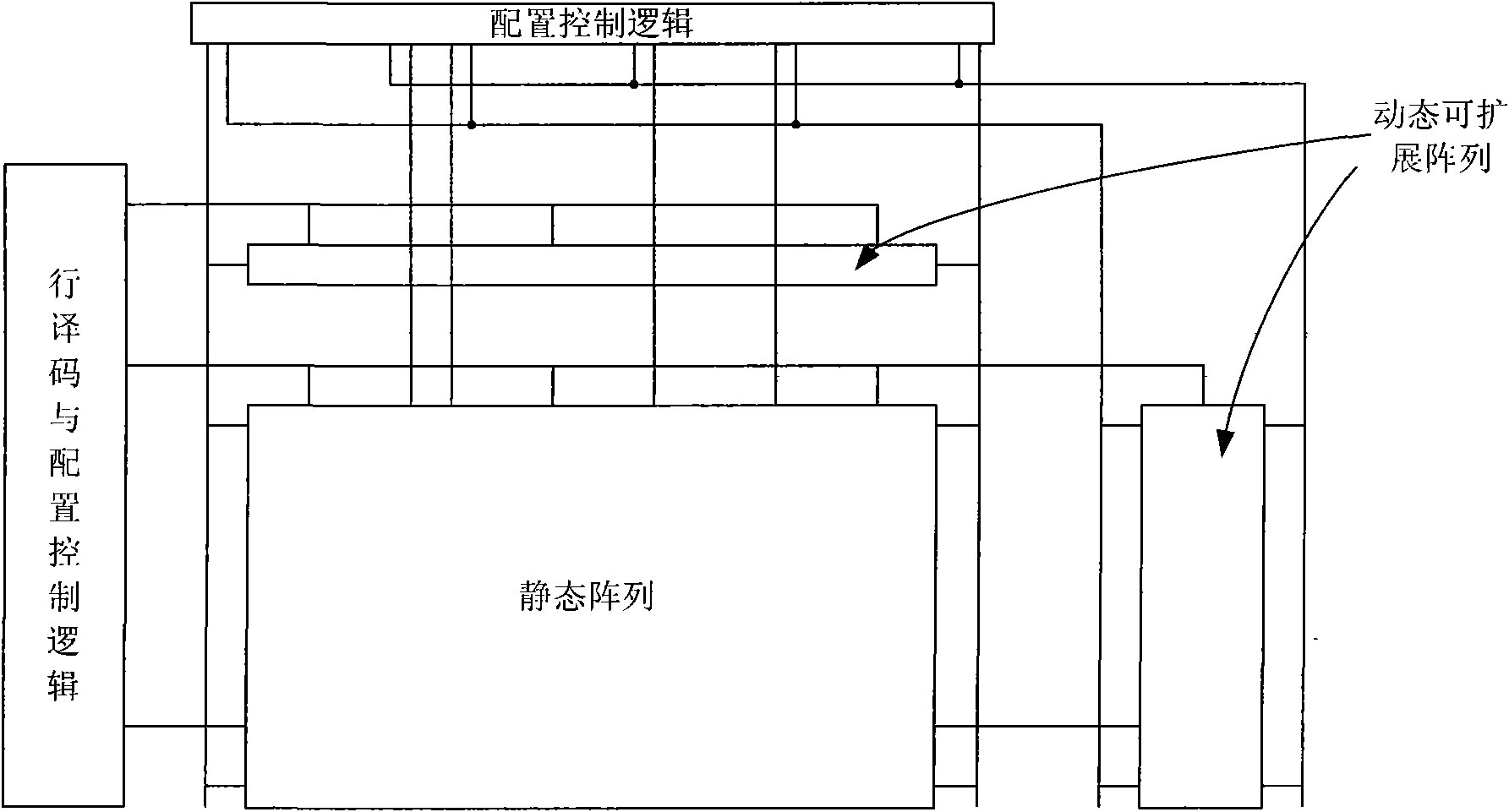

[0017] The redundant structure of the dynamic memory array in this paper includes: a dynamic redundant column array and a dynamic redundant row array, which are respectively located above and to the right of the static memory array, which is considered for the decoding logic and the layout of the layout. Redundant array configuration control logic modules are also divided into row array configuration logic and column array configuration logic. The configuration control selection signal adopts top-level wiring, which makes it very easy for the laser programming method to control whether to select redundant column arrays or row arrays. easy to accomplish.

[0018] The steps of redunda...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More