Multi-standard LDPC encoder circuit base on SIMD architecture

A decoder, multi-standard technology, applied in the field of decoder circuits, can solve problems such as limitations, complex hardware implementation, and unfavorable simplified circuit design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

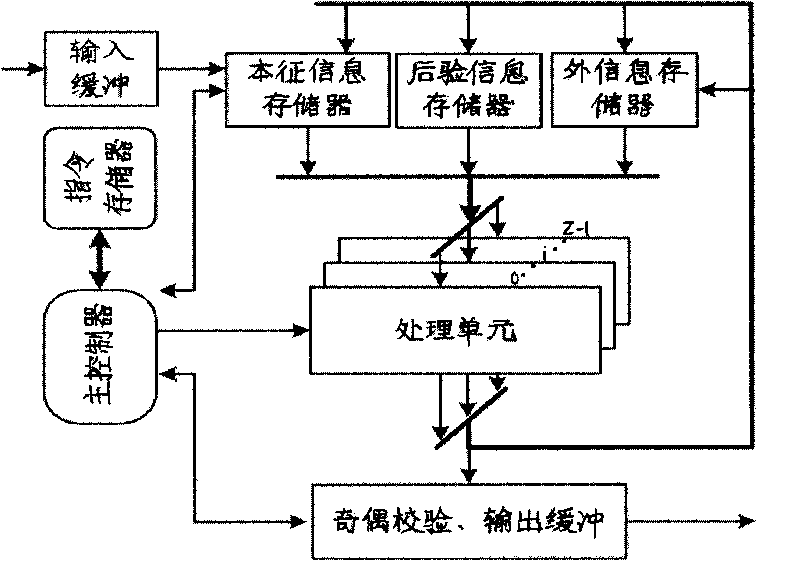

[0028] According to the solution provided in the summary of the invention, the specific implementation of the multi-standard LDPC decoder based on the SIMD structure is as follows:

[0029] Before decoding, the main controller first reads the parameter configuration information from the instruction memory, and performs the initialization operation. The input buffer unit notifies the main controller that the data is ready and waiting for decoding after receiving a complete frame length data. After the main controller reads the data, the input buffer automatically enters the receiving state of the next frame of data.

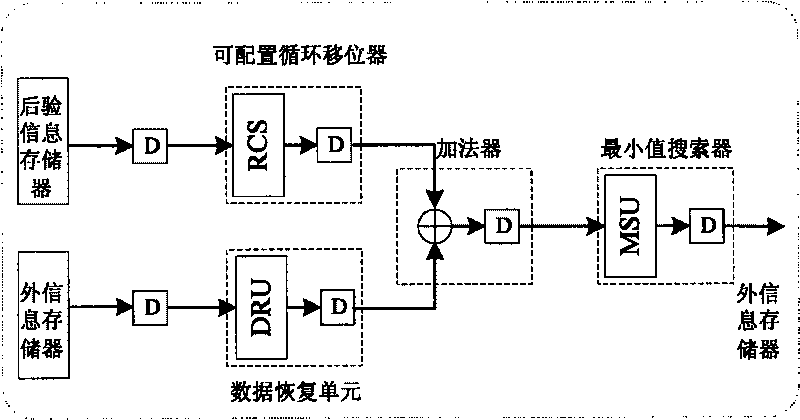

[0030] At the beginning of decoding, the internal state machine controls the data flow of the entire decoder according to the decoding mode, and the main controller reads the row or column scanning instruction and sends it to the processing unit array. Multiple parallel processing units simultaneously receive the instruction stream sent from the main controller, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More