Method for designing micro/nano-scale nonstandard product structure

A technology of product structure and micro-nano scale, applied in the direction of micro-structure technology, micro-structure devices, computing, etc., can solve the problem of the scale and complexity of micro-nano-scale product design, and the difficulty of macro-scale design methods to adapt to micro-nano scale and limitations. Issues such as product independence and innovation, to achieve the effect of improving design efficiency, enhancing openness, and meeting simulation needs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

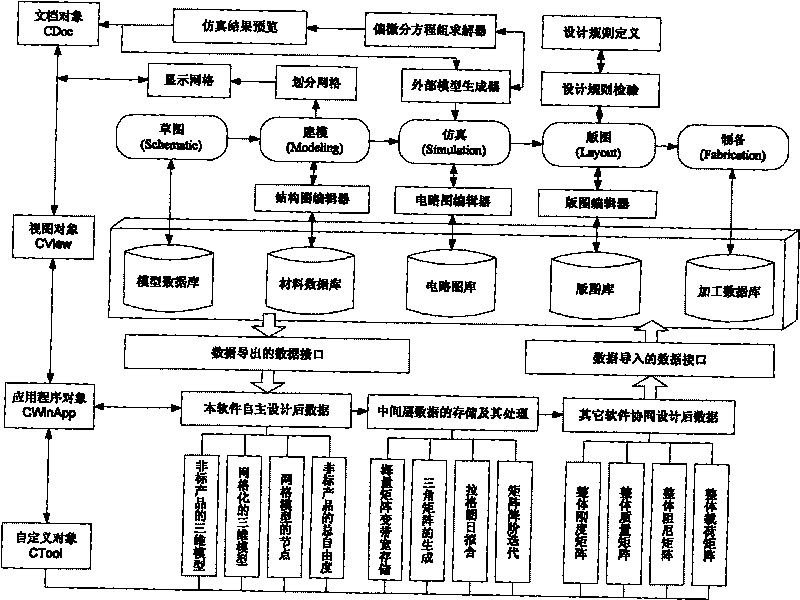

[0031] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

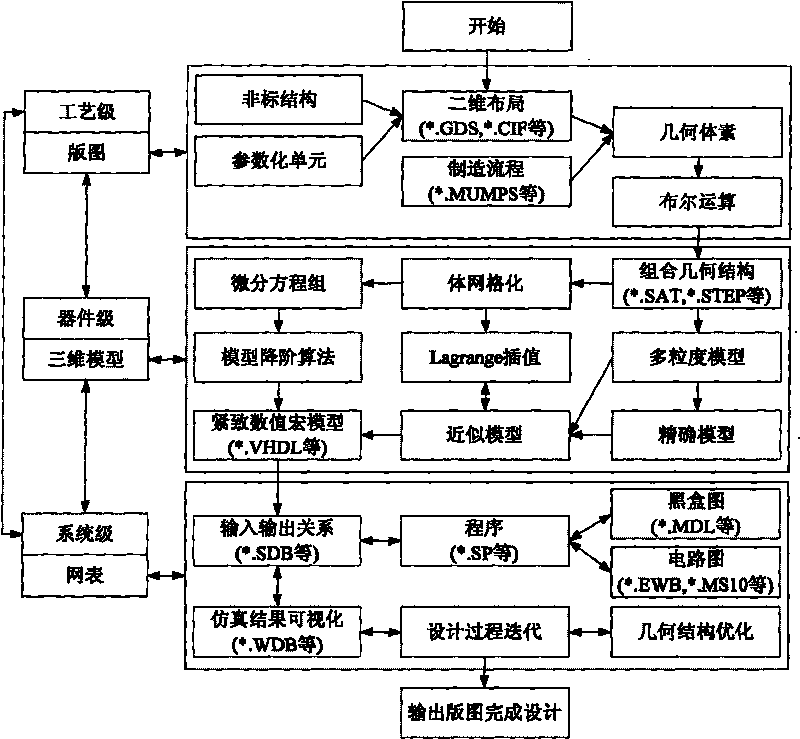

[0032] Such as figure 1 Shown is the main design process of the method proposed by the present invention. The interface from device level to system level is called macro modeling. The macromodel connects the device-level model and the system-level model. The modeling level of micro-nano structure can be divided into system level, device level and process level design.

[0033] (1) System-level design: Facing user requirements, focusing on the overall behavioral characteristics and performance of the system, including product concept design, formulation of design schemes, providing basis for device-level design, and integrating the macro-model obtained at the device layer into the system model Carry out simulation and optimize the system according to the simulation results.

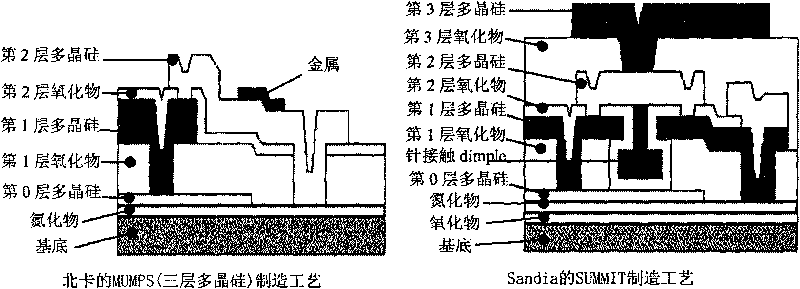

[0034] (2) Device-level design: including device modeling, process simulati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More