Memory system topologies including a buffer device and an integrated circuit memory device

An integrated circuit and memory technology, applied in the field of integrated circuit devices, can solve the problems of capital investment cost affecting the speed of DRAM technology data bandwidth and system capacity requirements, DRAM expensive data bandwidth and system memory requirements, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

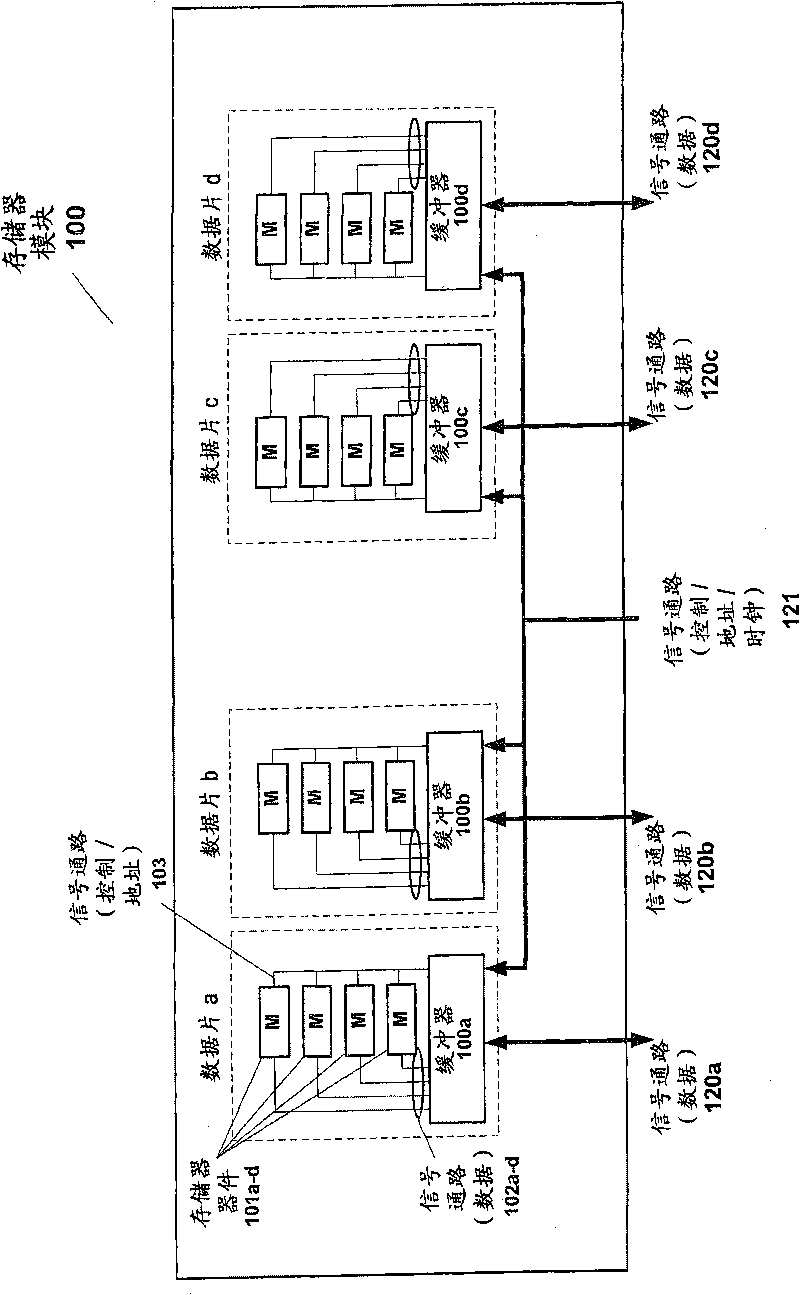

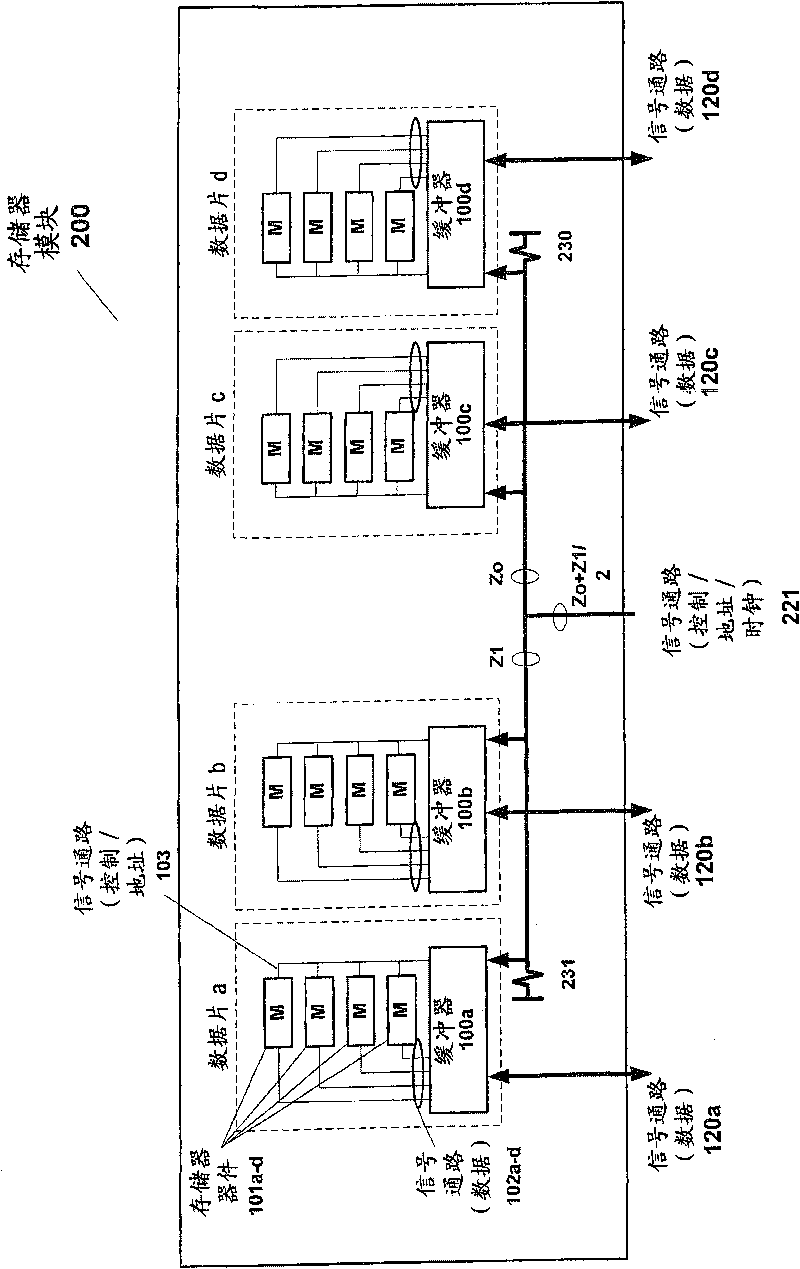

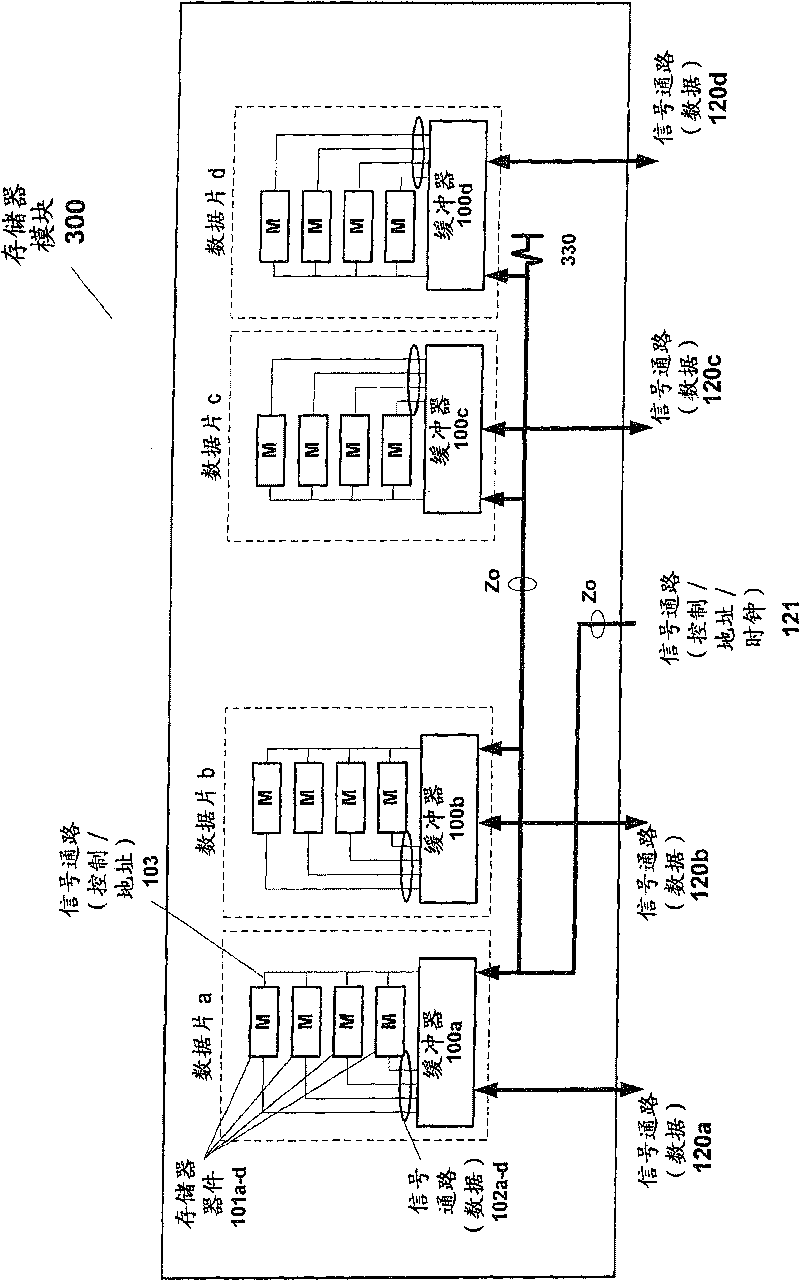

[0047] The system, among other embodiments, includes a topology for transferring data and / or control / address information between an integrated circuit buffer device (which may be coupled to a master device such as a memory controller) and a plurality of integrated circuit memory devices . For example, independent segment (or point-to-point link) signal paths may be used across multiple integrated circuit buffer devices in response to control / address information provided from an integrated circuit buffer device to multiple integrated circuit buffer devices using a single fly-by (or bus) signal path. Data is provided between the circuit memory device and the integrated circuit buffer device. Other topology types may include fork, star, fly-by, segment, and topologies used in SIP or MCP embodiments.

[0048] Integrated circuit buffer devices enable configurable efficient memory organization of multiple integrated circuit memory devices. The memory organization represented to th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More