Method for testing service life of NMOS hot carrier injection

A hot carrier and lifetime technology, applied in the direction of single semiconductor device testing, semiconductor/solid-state device testing/measurement, etc., can solve the problems of scrapped wafers and increased costs, and achieve cost saving, saving capacity and material loss, and saving The effect of test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The specific embodiment of the present invention will be described in more detail below in conjunction with the accompanying drawings.

[0018] A method for testing the hot carrier injection lifetime of an NMOS device, comprising the steps of:

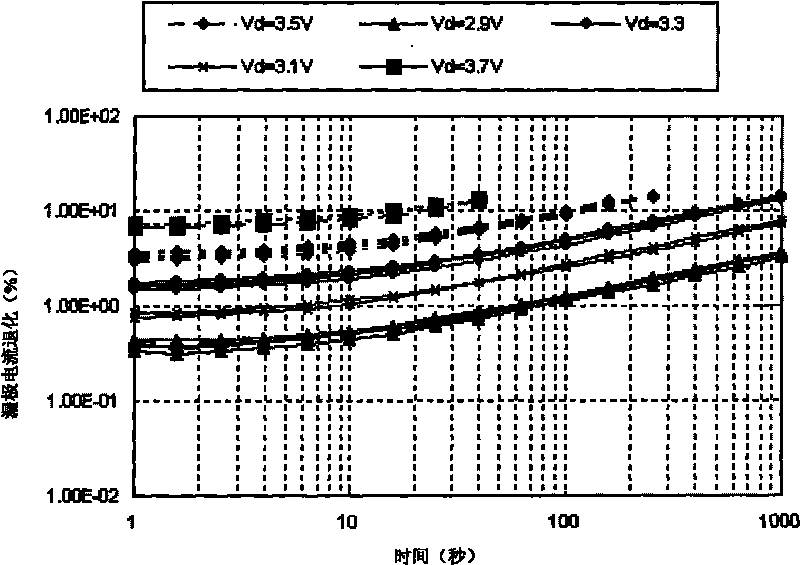

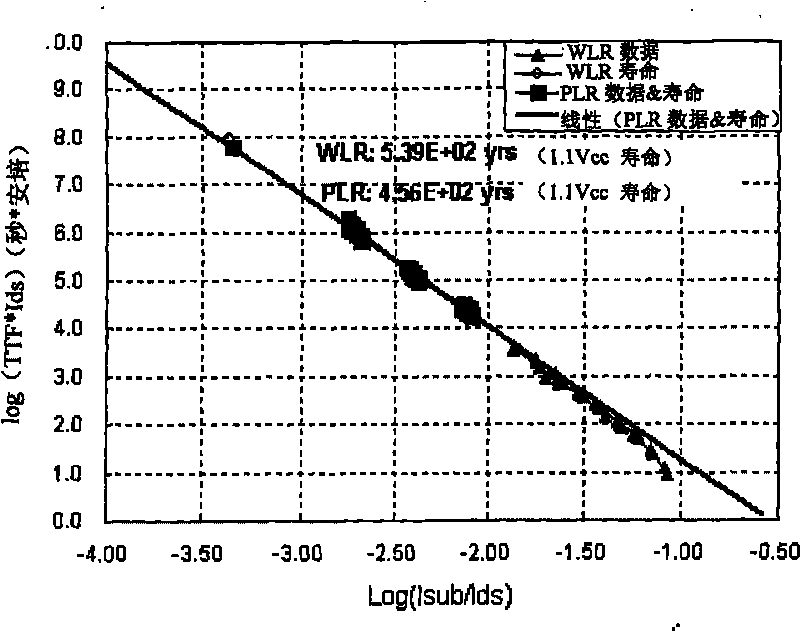

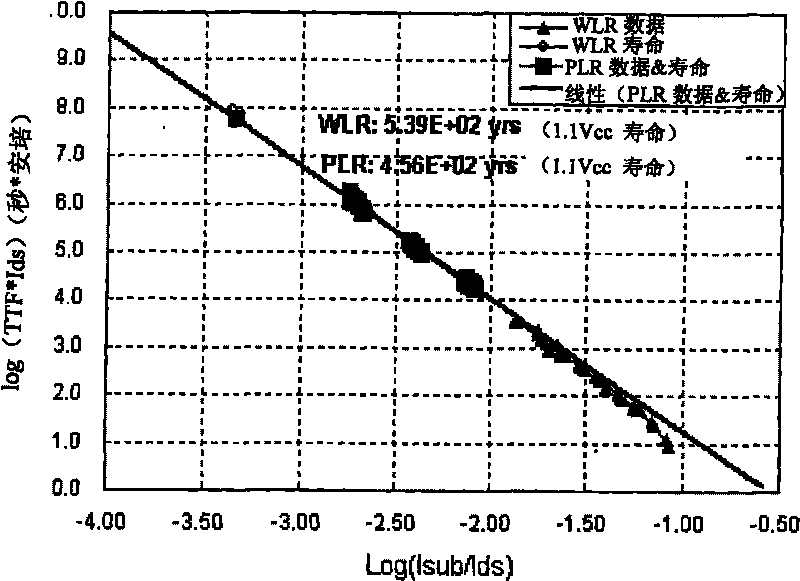

[0019] Step 1. The test system applies test voltage stress to the drain of the device under test, and the value of the test voltage is between 60% and 70% of the breakthrough voltage. This test system can be determined according to needs, and in the present embodiment, be to use Agilent 4070 test system under RMB (Agilent assembly language Rocky Mountain Basic, applied to Agilent test system) environment; The stress voltage that this drain is added is the most important a parameter of .

[0020] Step 2. The test system uses the method of maximum base current for testing. The gate voltage corresponding to the maximum base current when the voltage stress is applied to the drain is the gate voltage stress. The gate voltage stress ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com