SOI substrate-based antifuse unit structure and preparation process thereof

A preparation process and anti-fuse technology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts, etc., can solve the problem that the peripheral circuit does not have the advantage of anti-radiation, and the anti-radiation advantage of the anti-fuse unit cannot be obtained Fully embodies other issues, to achieve the effect of enhancing the ability to resist total dose radiation, good resistance to single particle ability, and good resistance to total dose radiation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be further described below in conjunction with specific drawings and embodiments.

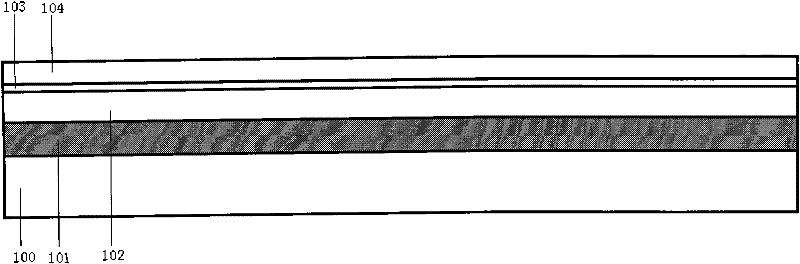

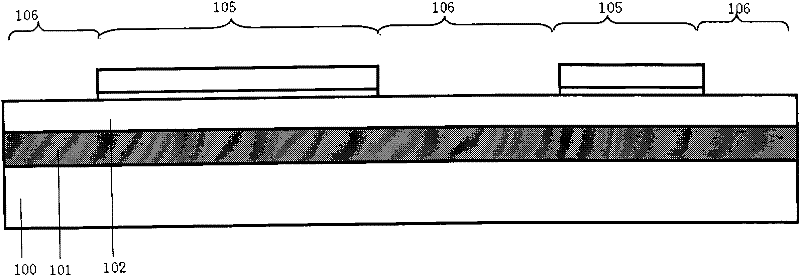

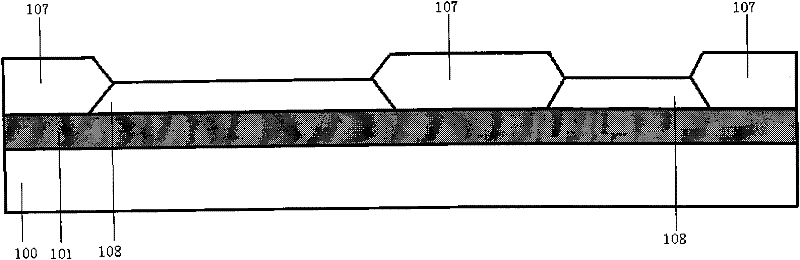

[0029] Figure A-1 to Figure A-8 Description of the identification numbers on the middle picture: 100-bulk silicon substrate, 101-silicon dioxide buried layer, 102-silicon film, 103-third silicon dioxide layer, 104-second silicon nitride layer, 105-first organic Source region, 106-field region, 107-silicon dioxide spacer layer, 108-second active region, 109-MOSFET well region, 110-antifuse lower plate, 111-first silicon dioxide layer, 112- First silicon nitride layer, 113-second silicon dioxide layer, 114-polysilicon layer, 115-silicide layer, 116-MOSFET gate, 117-antifuse upper plate, 118-MOSFET source , 119-MOSFET drain.

[0030] Such as Figure A-8 As shown: the silicon dioxide buried layer 101 is located on the bulk silicon substrate 100, and at least one MOSFET well region 109 and at least one antifuse lower plate 110 are arranged on the silicon dioxide...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More