A silicon-on-insulator material and its reinforcement method against total dose radiation

A technology of silicon-on-insulator and anti-total dose, which is applied in the field of semiconductor technology, can solve the problems of implantation damage, affecting the electrical characteristics of SOI devices and circuits, etc., and achieve the effect of suppressing net accumulation and improving the ability of anti-total dose radiation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

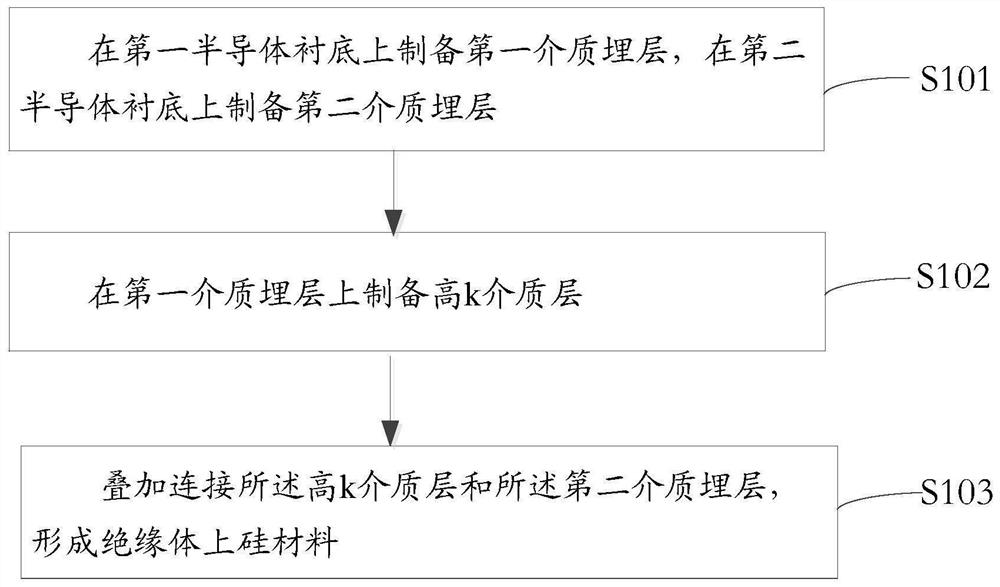

[0033] In this embodiment, a method for strengthening silicon-on-insulator materials against total dose radiation is provided, such as Figure 1~3 shown, including:

[0034] Step S101, preparing a first buried dielectric layer 2 on the first semiconductor substrate 1, and preparing a second buried dielectric layer 4 on the second semiconductor substrate 3;

[0035] Step S102, preparing a high-k dielectric layer 5 on the first buried dielectric layer 2;

[0036] Step S103, superimposingly connecting the high-k dielectric layer 5 and the second buried dielectric layer 4 to form a silicon-on-insulator material.

[0037] It should be noted that step S102 may be performed before the second buried dielectric layer 4 is prepared on the second semiconductor substrate 3, or after or simultaneously with the second buried dielectric layer 4 prepared on the second semiconductor substrate 3, No limitation is imposed here.

[0038] Below, combine Figure 1 ~ Figure 3 , introducing in de...

Embodiment 2

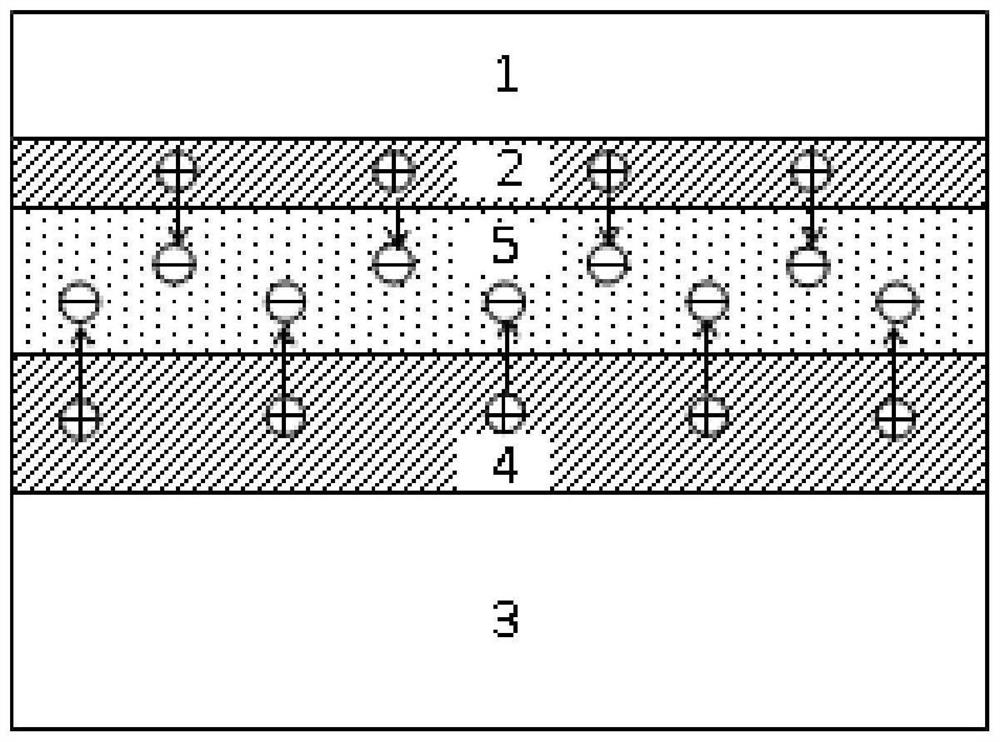

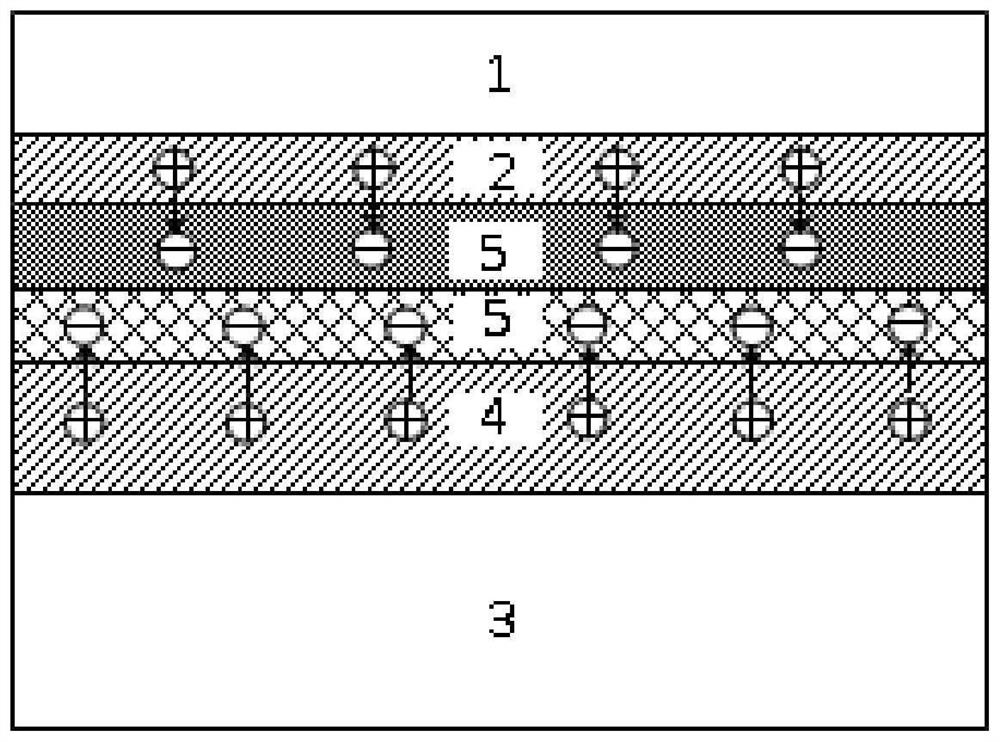

[0057] This embodiment provides a silicon-on-insulator material, such as figure 2 and 3 shown, including:

[0058] The first semiconductor layer 1, the first buried dielectric layer 2, the second buried dielectric layer 4 and the second semiconductor layer 3 stacked in sequence;

[0059] Wherein, a high-k dielectric layer 5 is embedded between the first buried dielectric layer 2 and the second buried dielectric layer 4 .

[0060] In the embodiment of the present application, the theoretical total trapped charge density value of the first buried dielectric layer 2, the second buried dielectric layer 4 and the high-k dielectric layer 5 tends to zero under preset working conditions.

[0061] In the embodiment of the present application, the high-k dielectric layer 5 includes a high-k material with an initial negative charge for electron traps.

[0062] In the embodiment of the present application, the high-k dielectric layer 5 includes multiple high-k dielectric layers of dif...

PUM

| Property | Measurement | Unit |

|---|---|---|

| relative permittivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com