Method of layout design of laterally diffused MOS transistor

A MOS transistor and layout design technology, applied in transistors, computing, electrical solid devices, etc., can solve the problems of large drain resistance, difficult resistance value, large drain area, etc., to reduce parasitic resistance, increase uniformity, The effect of even wiring

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

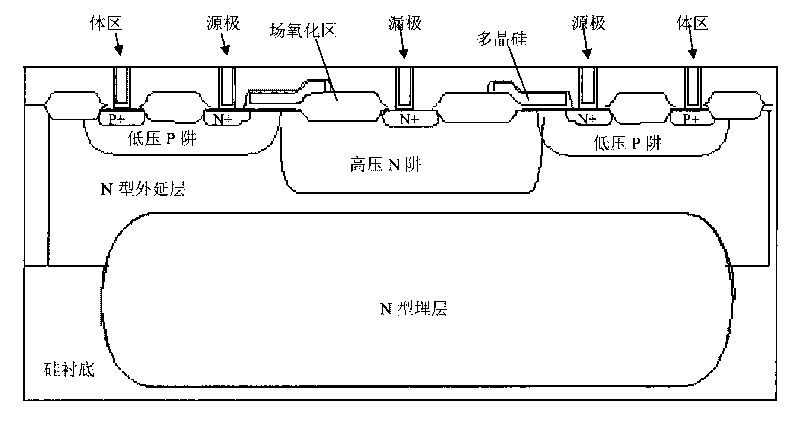

[0016] In the layout design method of the laterally diffused MOS transistor of the present invention, there are mainly the designs of the following areas:

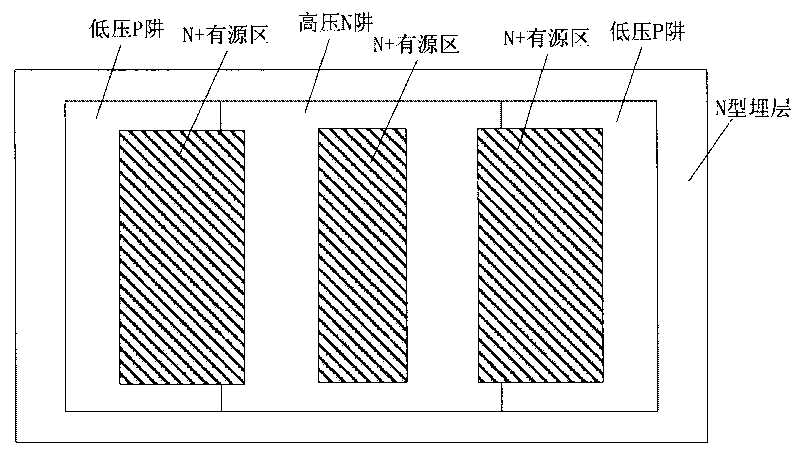

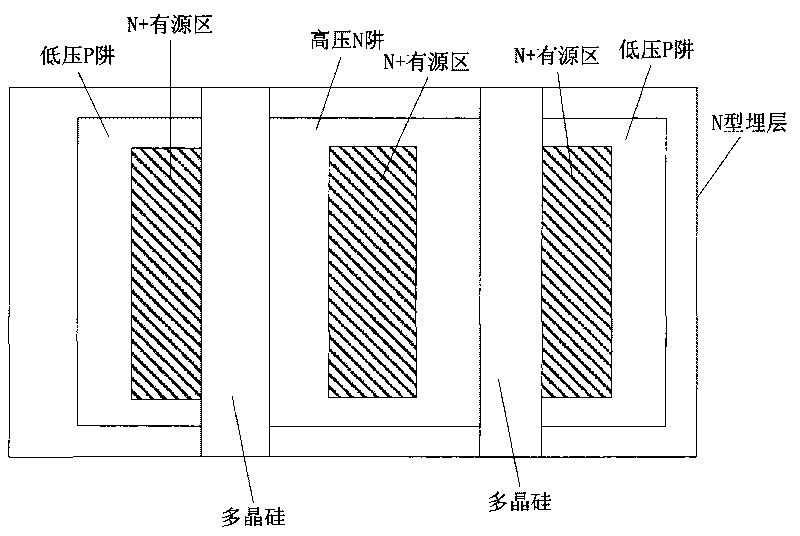

[0017] 1. The design method of the well is: usually LDMOS transistors use low-voltage or high-voltage wells as the source and drain regions to increase the breakdown voltage. In the design method of the present invention, the design of the well adopts a grid-like layout to ensure that each source region is surrounded by a drain region, and each drain region is also surrounded by a source region. image 3 In order to adopt the design method of a single unit of the source region and the drain region in the method of the present invention, it is formed by splicing two LDMOS transistors, the high-voltage N well region is the drain region, the P well region is the source region, and the source region and the drain region are phase Adjacent squares form a 3×3 square array unit (see Figure 4 ). By splicing and arranging a plur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More