Manufacturing method of semiconductor memory

A manufacturing method, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the obstacles of miniaturization or high integration of semiconductor memory, affect device performance, and make it difficult to keep the grid structure of grid array 15 straight And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

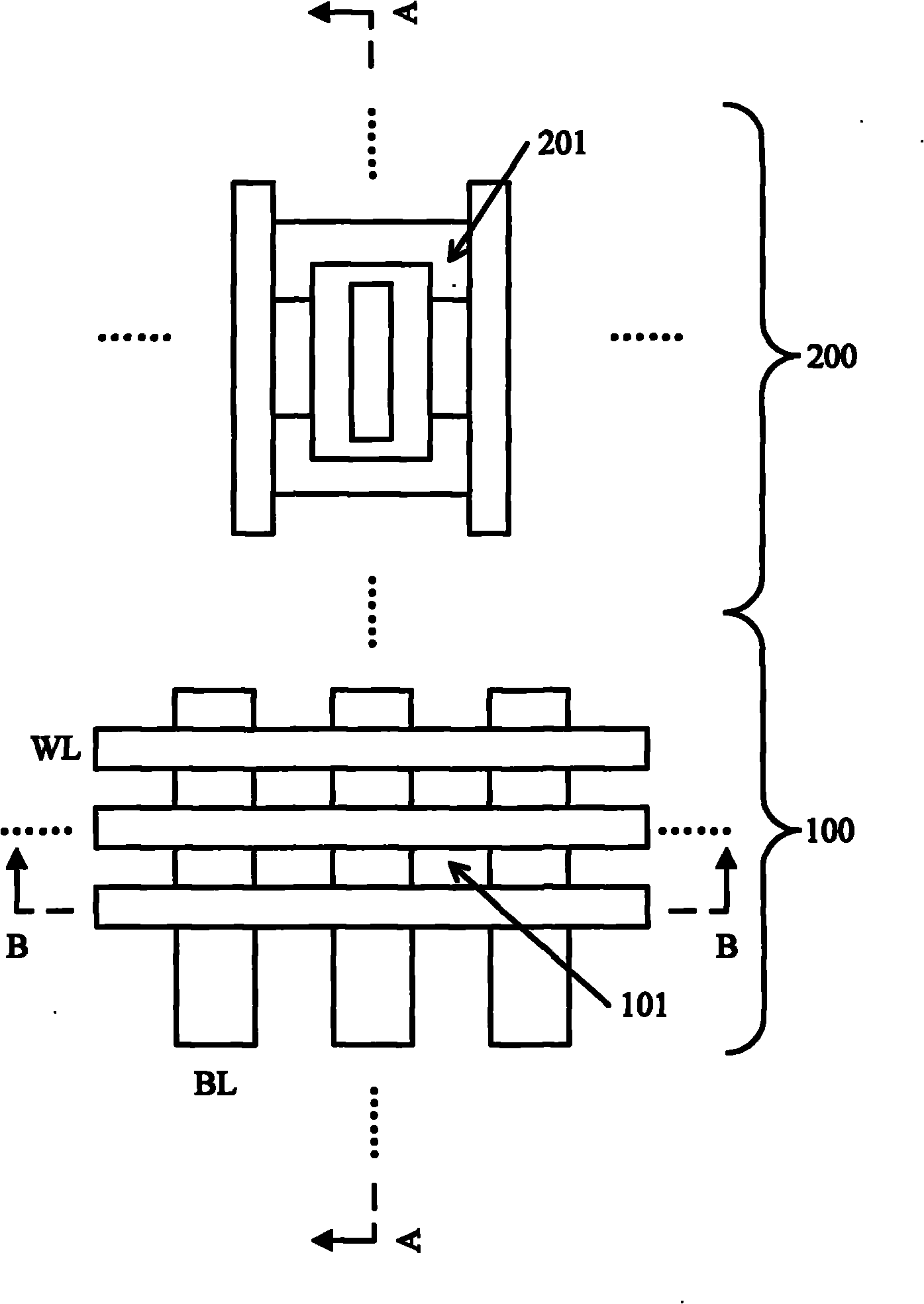

[0037] Please refer to Figure 9 , in the schematic diagram of the semiconductor memory manufacturing process given by it, the definition and etching of the gate array in the memory cell area come first, and the definition and etching of the gate of the logic transistor in the peripheral circuit area follow, as follows:

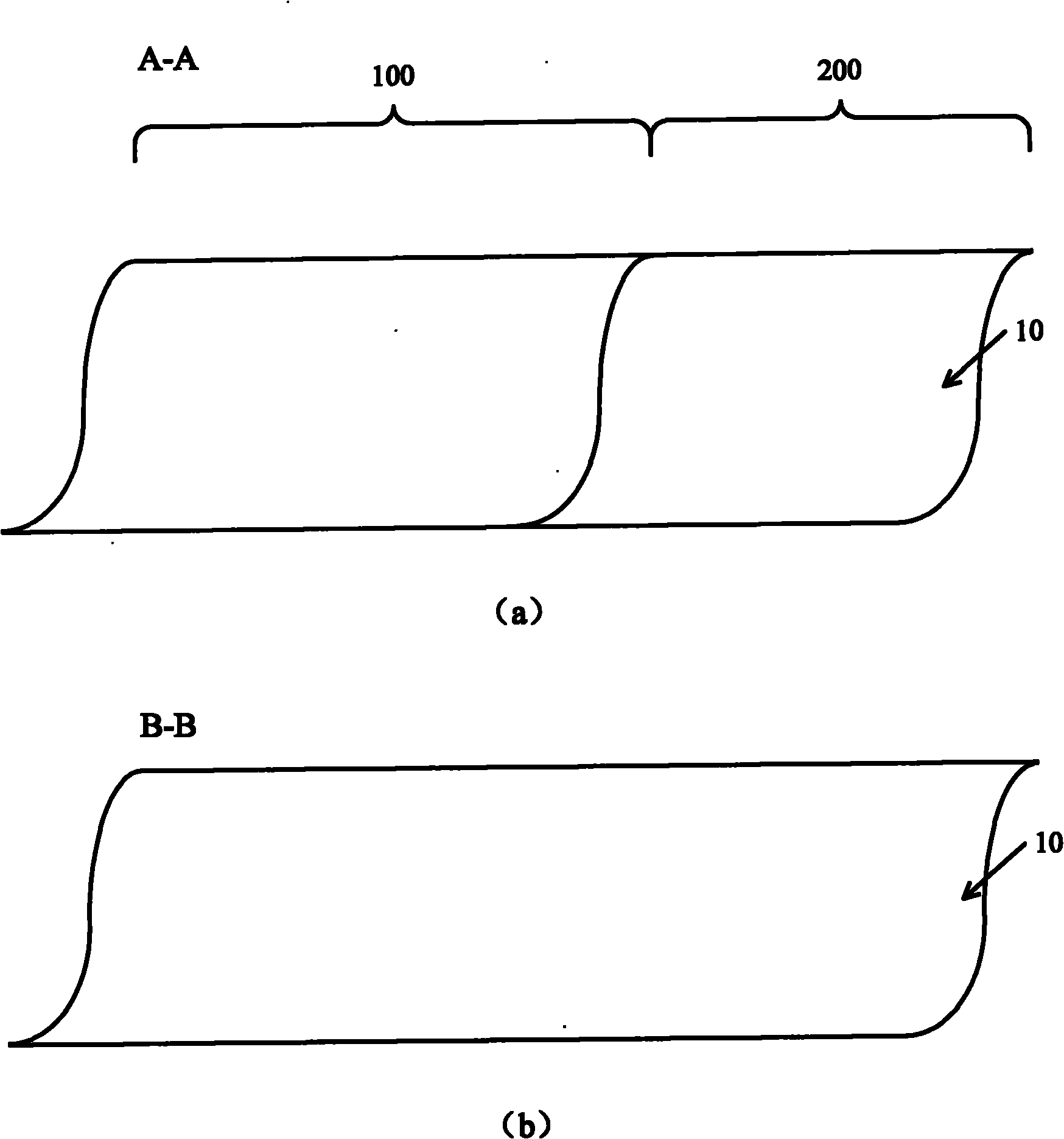

[0038] S11: providing a semiconductor substrate having a memory cell area and a peripheral circuit area;

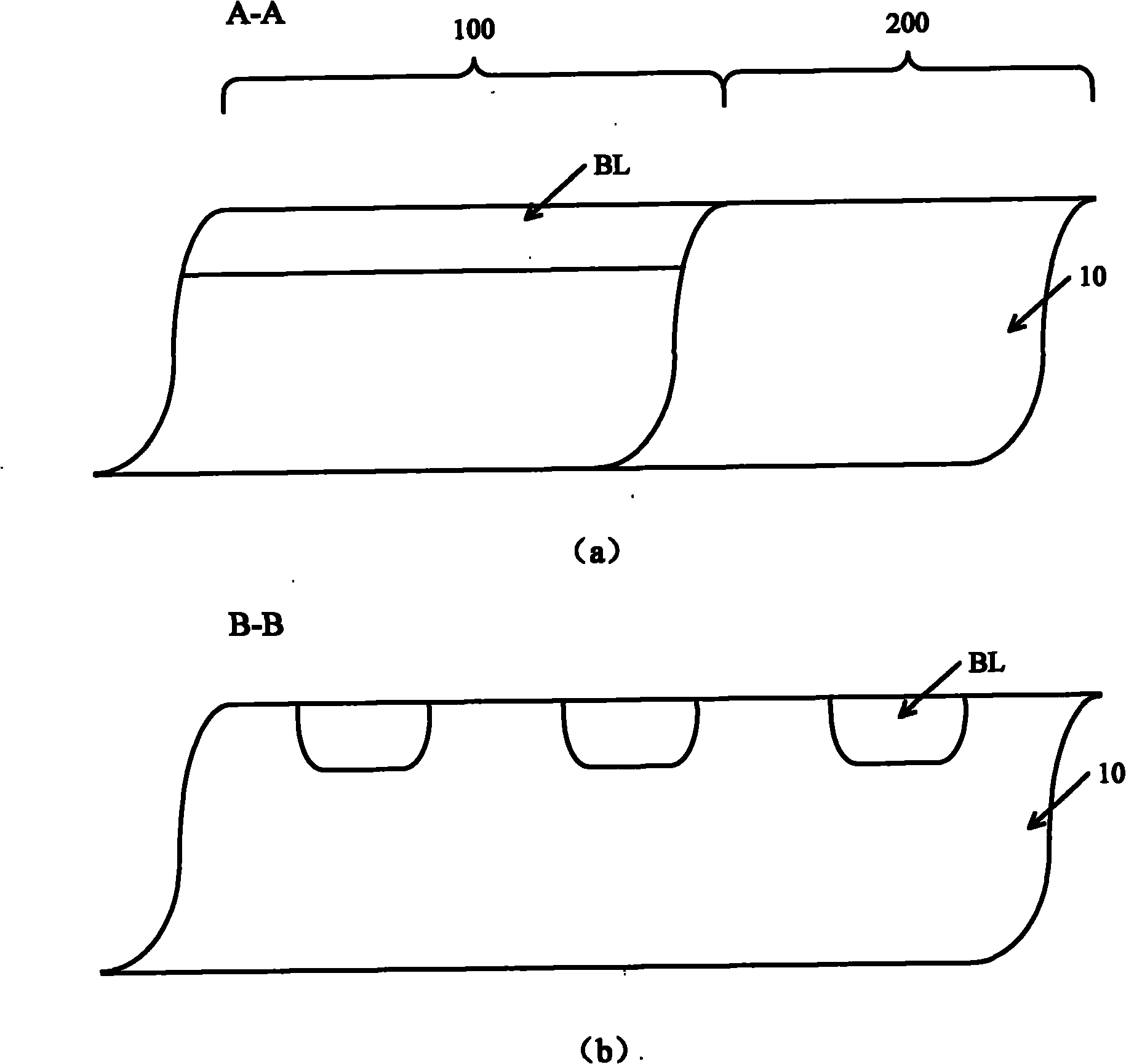

[0039] S12: forming a gate material layer on the semiconductor substrate;

[0040] S13: forming a first mask on the gate material layer, the first mask covers the peripheral circuit area and defines a gate array in the memory cell area;

[0041] S14: using the first mask as a barrier layer, etching to form a gate array;

[0042] S15: Perform anti-penetration (APT) implantation using the first mask as a barrier layer;

[0043] S16: removing the first mask;

[0044] S17: forming a second mask on the gate material layer, the second mask covers the memor...

Embodiment 2

[0048] Please refer to Figure 10 , in the schematic diagram of the semiconductor memory manufacturing process given by it, the definition and etching of the gate of the logic transistor in the peripheral circuit area come first, and the definition and etching of the gate array in the memory cell area follow, as follows:

[0049] S21: providing a semiconductor substrate having a memory cell region and a peripheral circuit region;

[0050] S22: forming a gate material layer on the semiconductor substrate;

[0051] S23: forming a second mask on the gate material layer, the second mask covers the memory cell area and defines the gate of the logic transistor in the peripheral circuit area;

[0052] S24: Using the second mask as a barrier layer, etch to form the gate of the logic transistor;

[0053] S25: removing the second mask;

[0054] S26: forming a first mask on the gate material layer, the first mask covers the peripheral circuit area and defines a gate array in the memor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More