High frequency switch circuit for inhibiting substrate bias effect in sampling hold circuit

A sample-and-hold circuit and high-frequency switching technology, which is applied in the direction of electrical components, output power conversion devices, etc., can solve the problems of affecting the accuracy of holding signals, the decline of circuit linearity, and the stability of thresholds, and achieve high-precision holding functions , good linearity, and the effect of improving the signal-to-noise-distortion ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

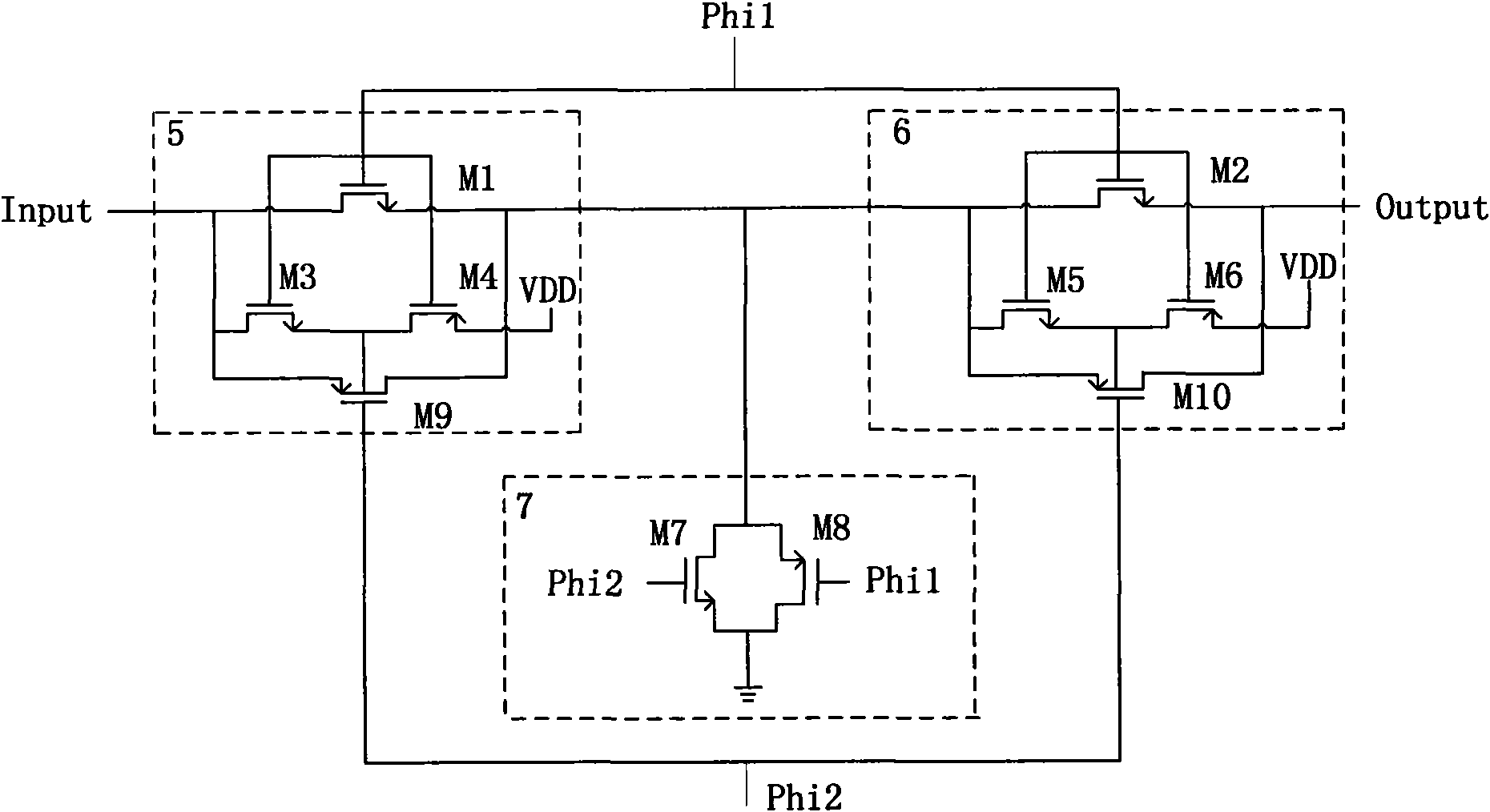

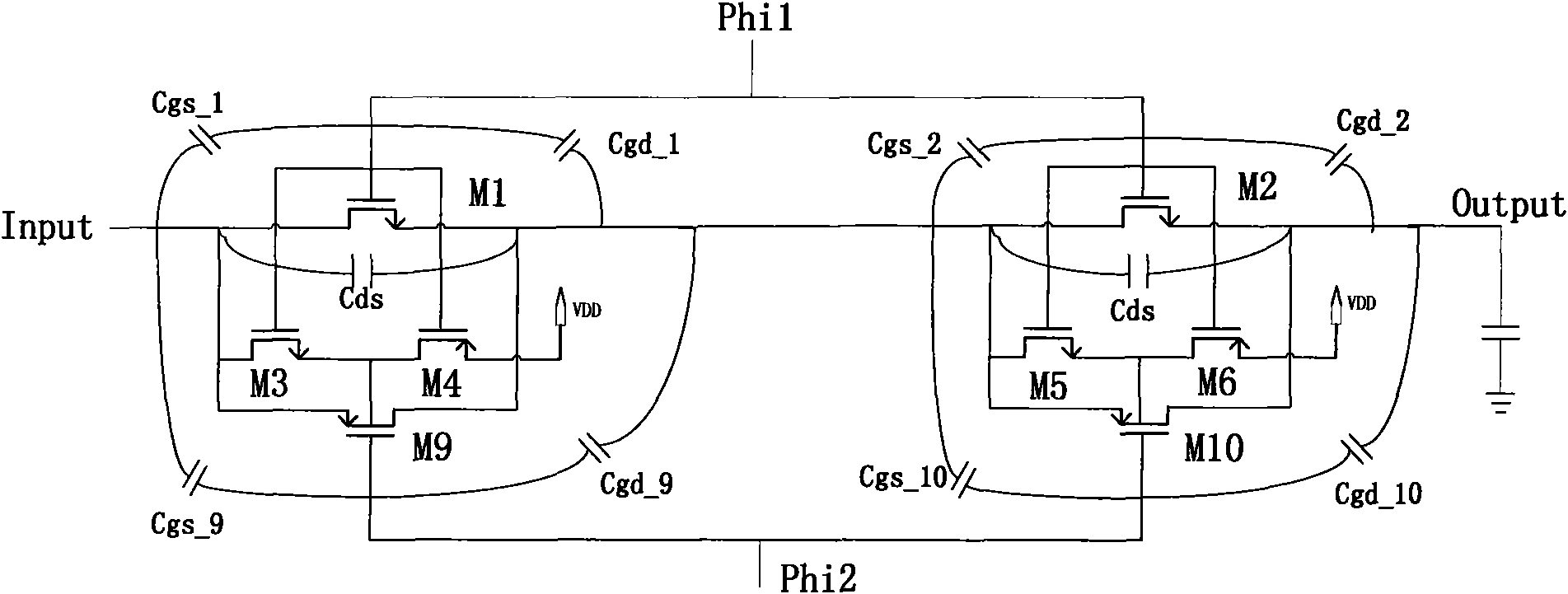

[0034] Such as figure 2 As shown, the high-frequency switch circuit for suppressing the substrate bias effect in the sample-and-hold circuit of the present invention includes three parts: the first substrate bias suppression high-frequency switch unit 5, the second substrate bias suppression high-frequency switch unit 6 and transmission gate switch 7.

[0035] One end of the first substrate bias suppression high-frequency switch unit 5 is connected to the input signal terminal Input, and the other end is connected to the second substrate bias suppression high-frequency switch unit 6 and the transmission gate switch 7; the second substrate bias suppression is high One end of the frequency switch unit 6 is connected to the first substrate bias suppression high frequency switch unit 5 and the transmission gate switch 7, and the other end is connected to the output signal terminal Output.

[0036] The first suppression substrate bias high-frequency switch unit 5 includes:

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More