Method for seeking mapping scheme between tasks and nodes of network on chip

An on-chip network and mapping scheme technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of high complexity of non-dominated sorting operations, and the performance of solutions is not particularly good, and achieves simple implementation and convergence. fast effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

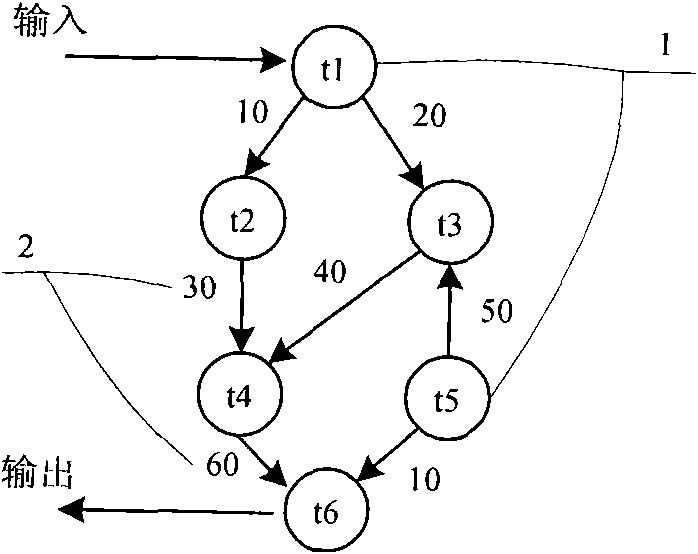

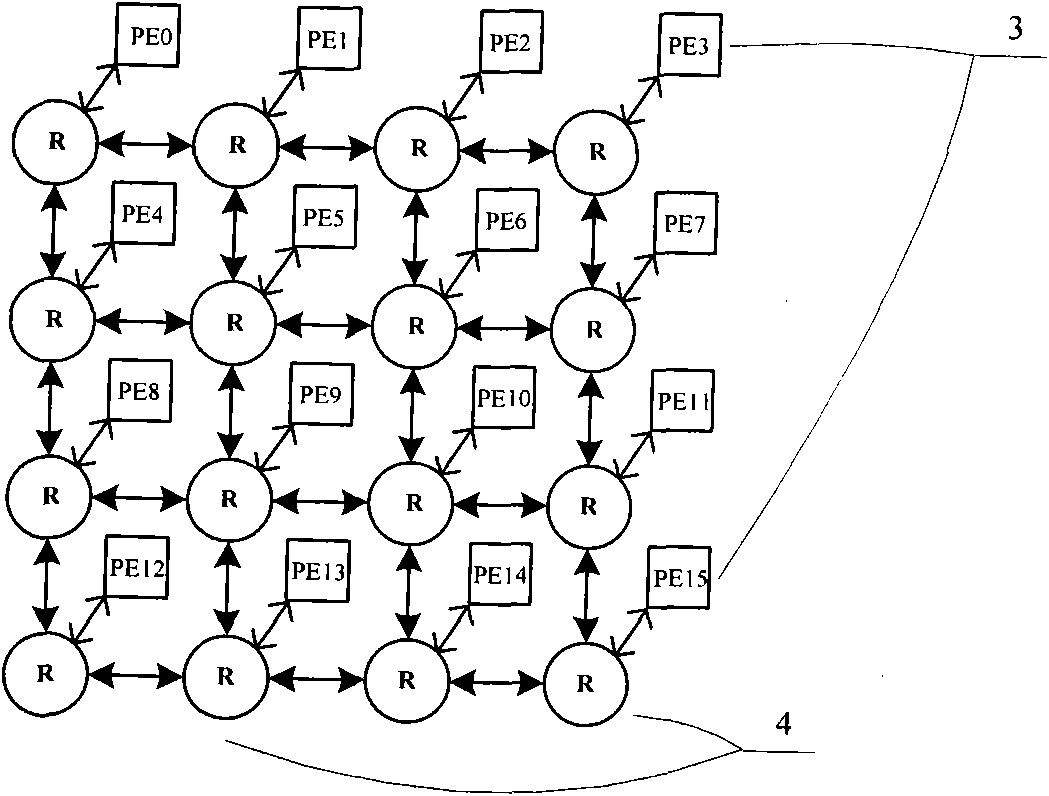

[0063] figure 1 The task graph shown has 6 tasks, figure 2 The network on chip shown has 16 nodes. This embodiment is to find a way to figure 1 The six tasks shown are assigned to figure 2 On the 16 nodes of the shown network on chip, the mapping scheme that makes the energy consumption and response time of the network on chip after mapping reach the minimum value at the same time. For the convenience of description, we use the vector X=(x 1 , x 2 , x 3 , x 4 , x 5 , x 6 ) represents a scheme in which 6 tasks of the on-chip network are mapped to 16 nodes, and the x on the nth position of the vector X n (0≤x n ≤15) represents the node number of the nth task mapped to a node, that is, x n Indicates that the task numbered n is assigned to the xth n of nodes.

[0064] The steps to find the solution that minimizes energy consumption and response time at the same time are as follows:

[0065] 1. Randomly generate a scheme group J containing 20 allocation schemes t ,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More