Method, apparatus, computer program product and device providing semi-parallel low density parity check decoding using a block structured parity check matrix

A parity check matrix and block structure technology, applied in the field of low-density parity check decoding, can solve the problems of restricted large area occupation, PCM is not architecture-aware, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

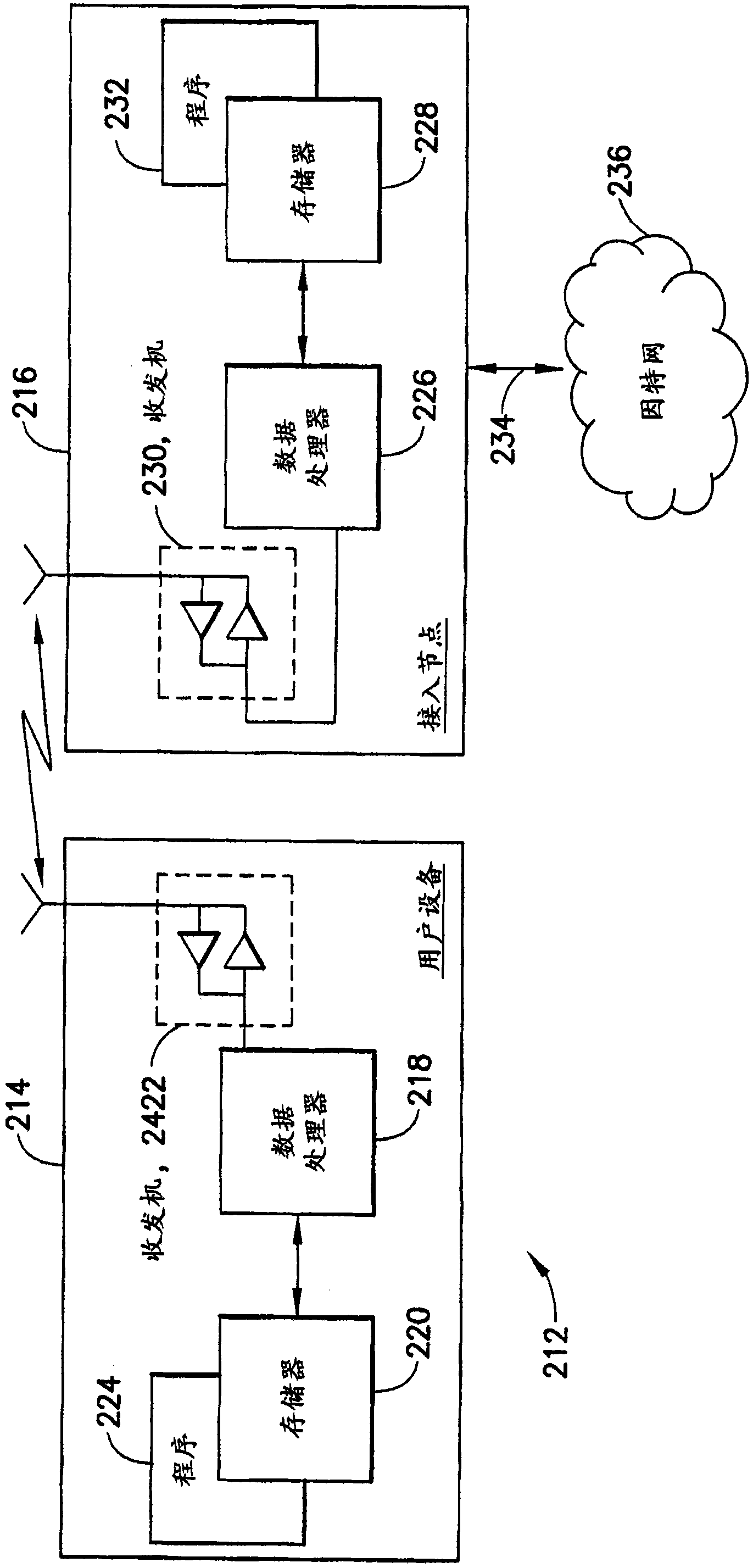

[0054] Embodiments in accordance with the present invention overcome the problems associated with architecture-aware PCM while maintaining the same error correction capability as when utilizing random PCM. These embodiments may enable a semi-parallel decoder architecture to achieve an average decoding throughput of about 1 Gbit / s.

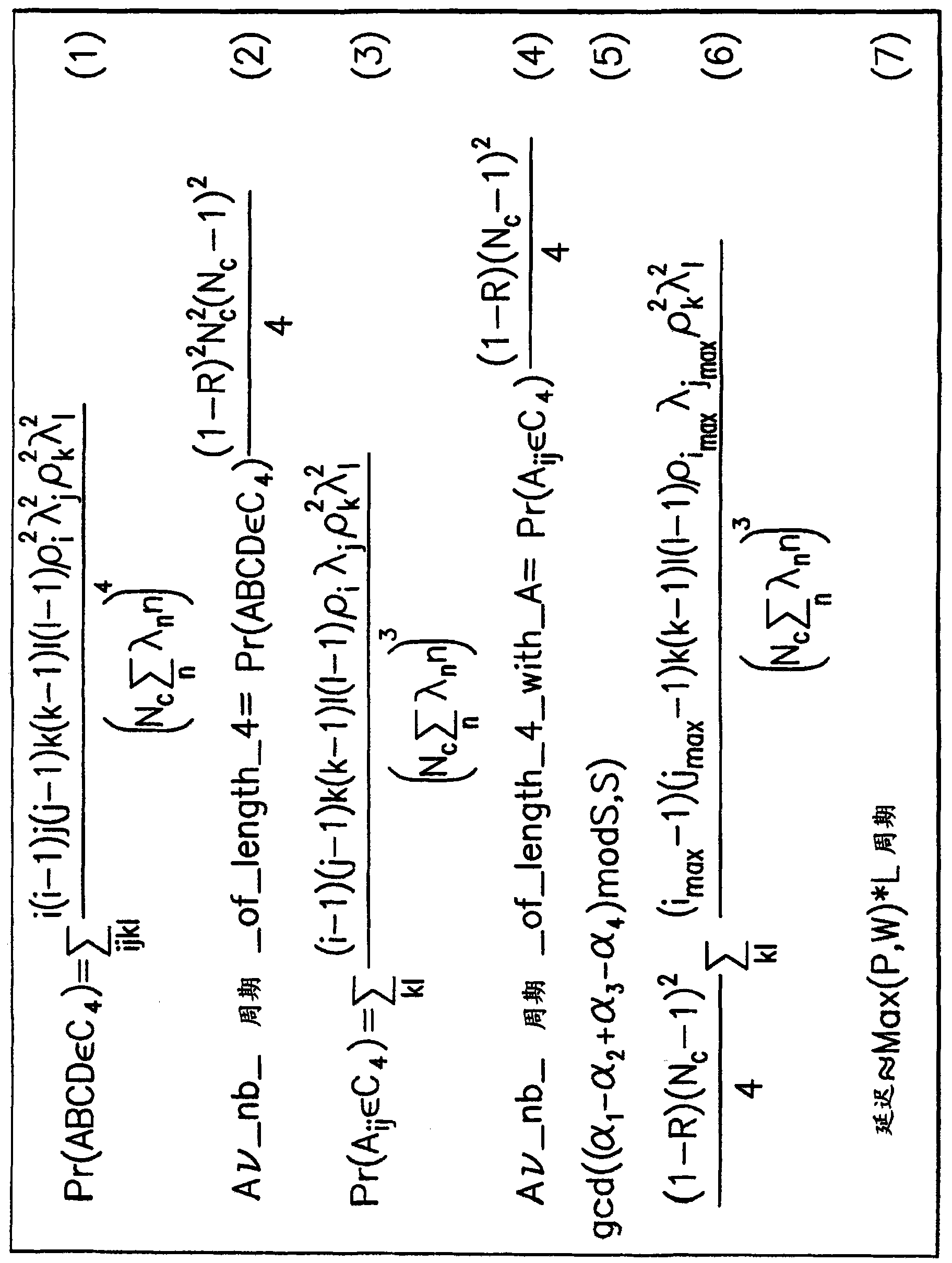

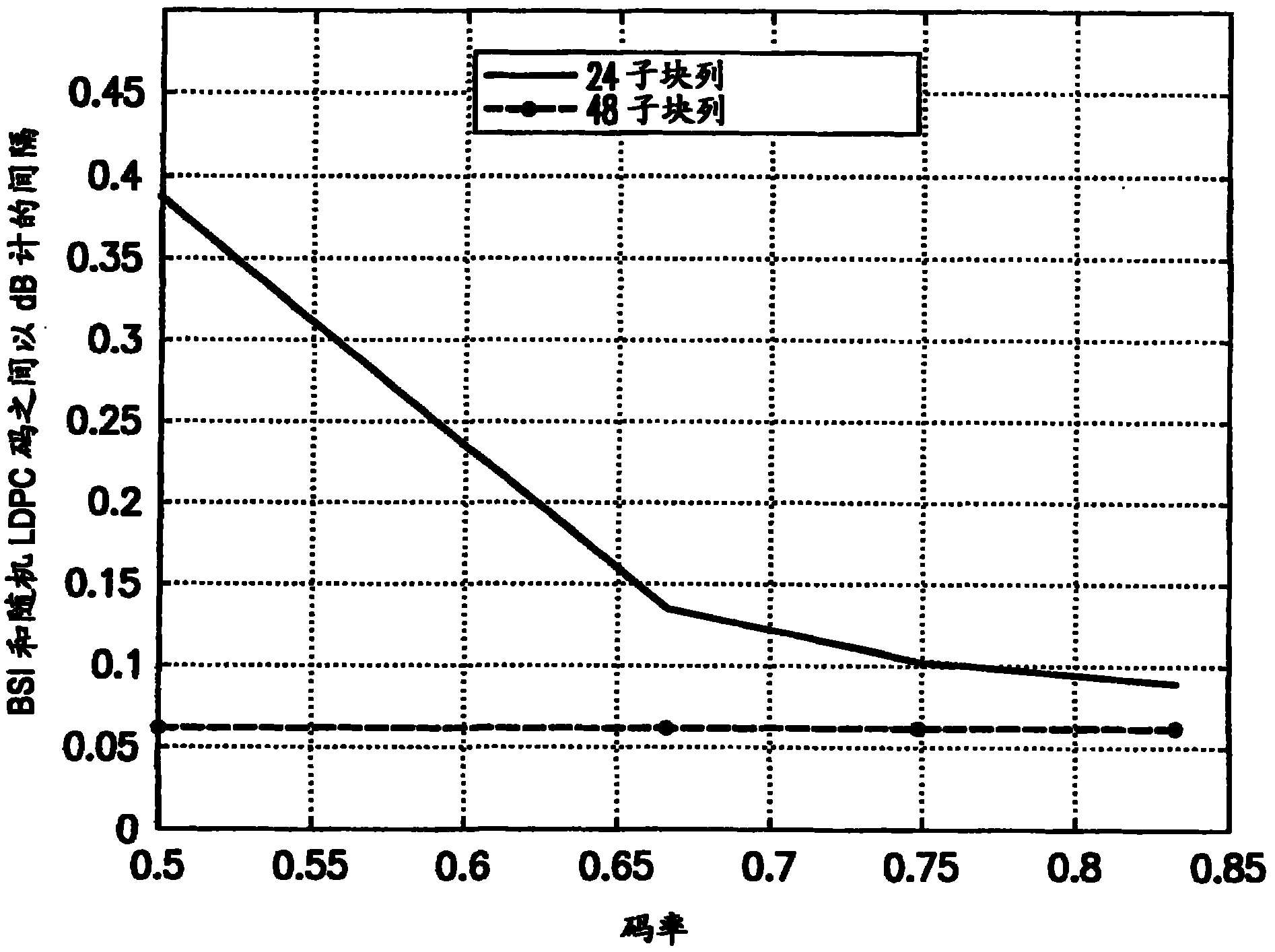

[0055] Embodiments according to the invention incorporate an architecture-aware block structure PCM. These PCMs, suitable for implementation in area efficient semi-parallel LDPC decoders, support high decoding throughput (eg, higher than 1 Gbit / s) without lacking error correction capabilities. PCM can incorporate several architecture-aware constraints: such as: minimum size of subblock matrix (e.g., shifted identity matrix), finite set of shift values for area-optimized decoder design, per Columns of odd / even non-zero blocks distributed equally across layers, and an upper triangular structure for the redundant part of the linear encoding (e.g., ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More