Duty ratio calibration circuit of precharge logical digital clock

A digital clock and calibration circuit technology, applied in the direction of transforming continuous pulse chains into pulse chain devices with required modes, etc., can solve problems such as long settling time, change influence, small edge jitter, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be described in detail below in conjunction with the accompanying drawings and specific examples.

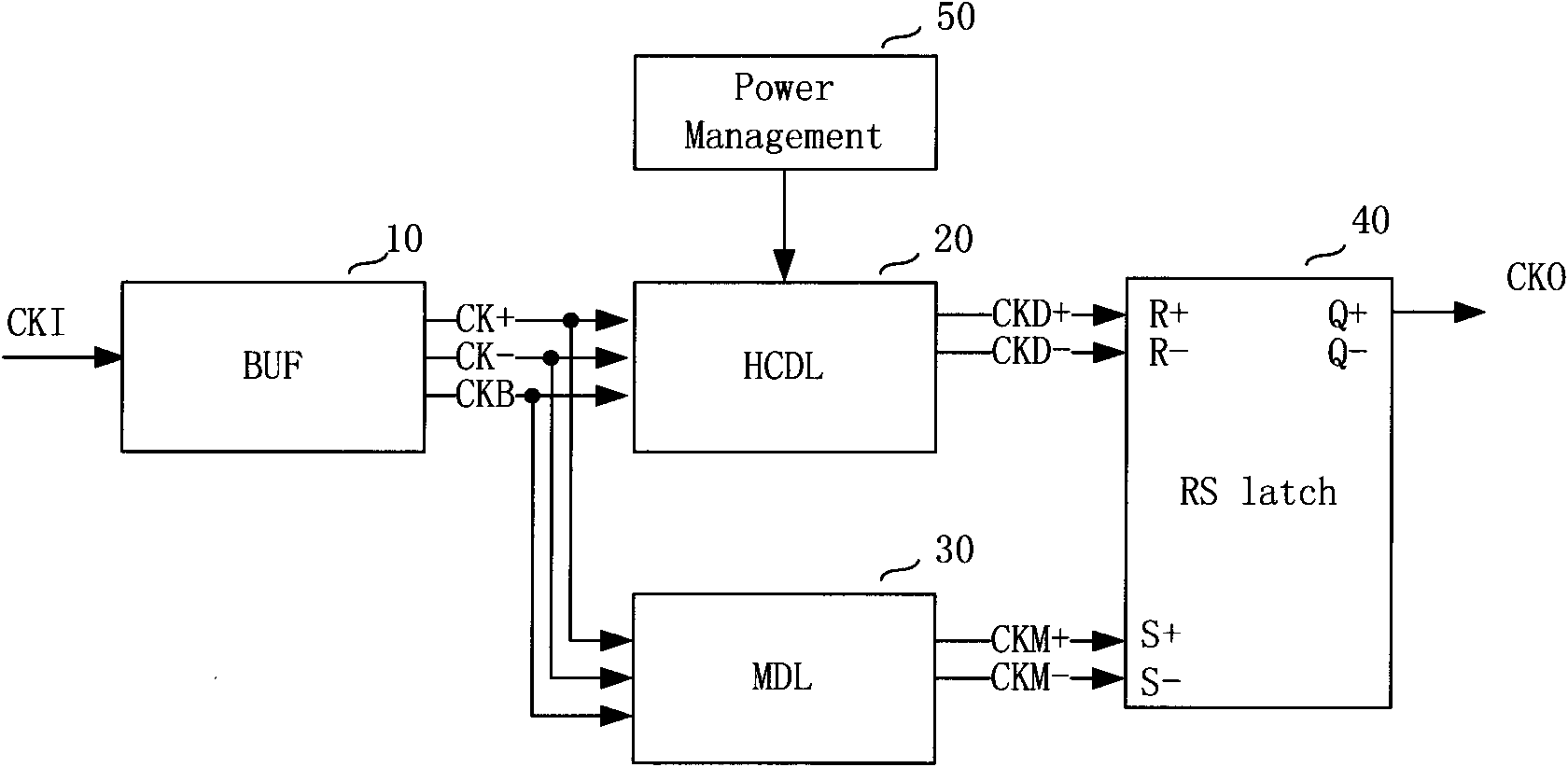

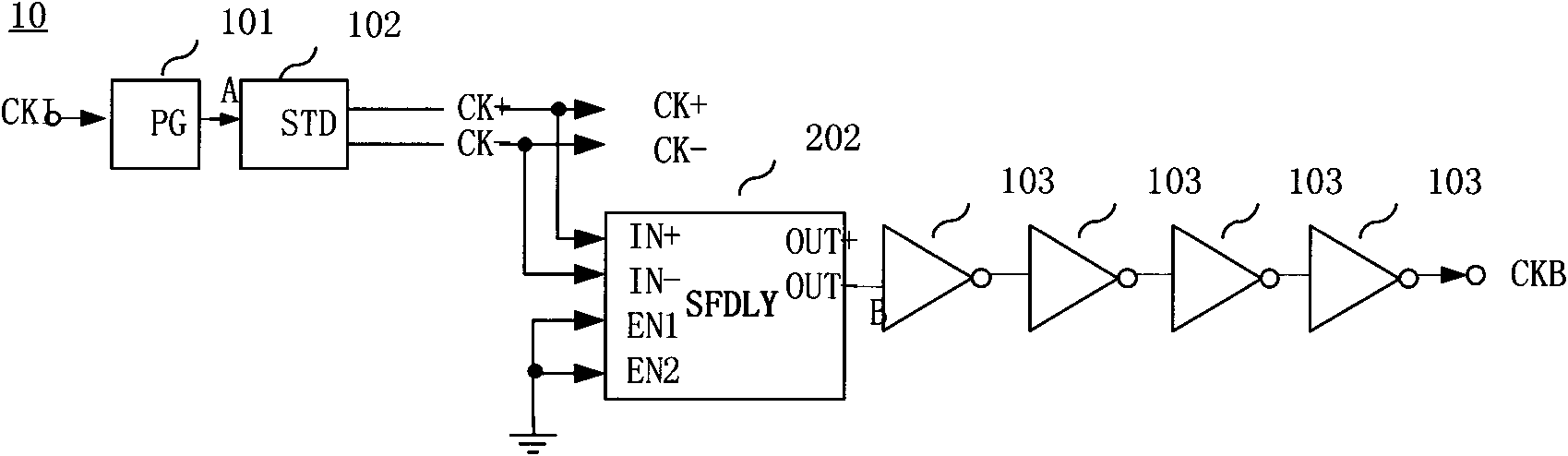

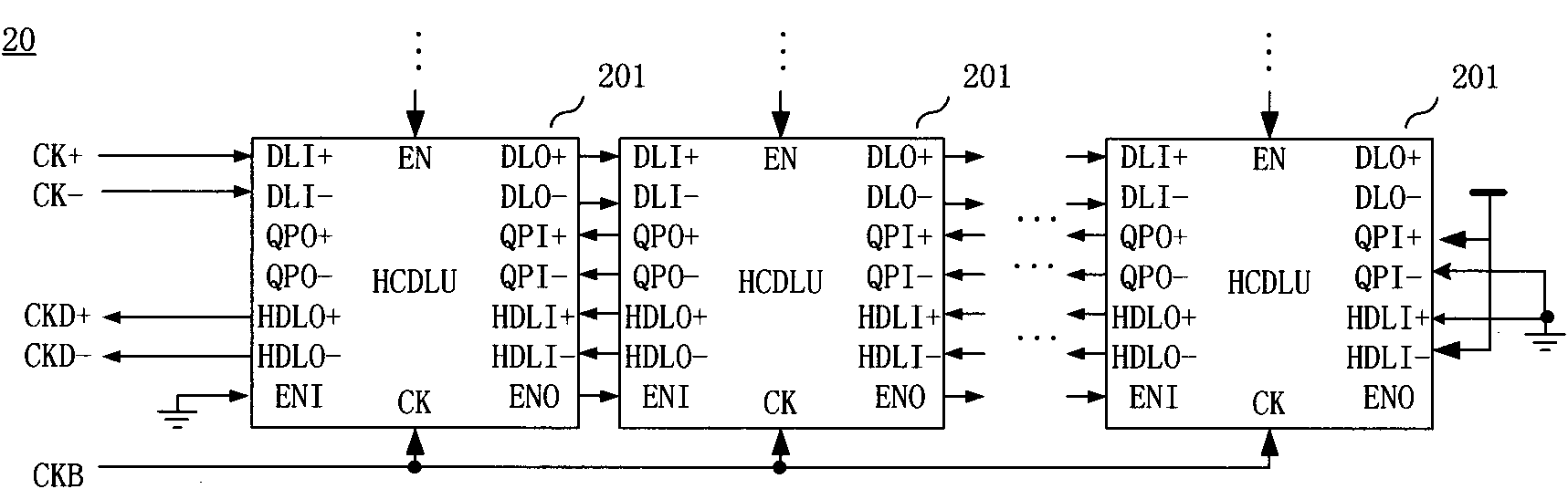

[0037] Such as figure 1 As shown, a digital clock duty ratio calibration circuit is characterized in that the left signal input terminal of the input stage 10 in the circuit receives the original input clock signal CKI calibrated; the output signal of the first and second signal output terminals of the input stage 10 The clock signals CK+ and CK- are respectively in differential form, and the output signal of the third signal output terminal is the buffered clock signal CKB. The buffered clock signal CKB is simultaneously connected to the corresponding input ends of the half-period delay line HCDL 20 and the matching delay line MDL 30; the output signal of the half-period delay line HCDL 20 is the half-period delayed clock signal CKD+ and CKD- in differential form, and The output signal of the matching delay line 30, that is, the matching delay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More