JTAG (Joint Test Action Group) real-time on-chip debug method and system of multicore processor

A multi-core processor, on-chip debugging technology, applied in the fields of electrical digital data processing, instruments, calculations, etc., can solve the problems of relatively large changes, poor reusability, and difficult physical design of chips, and achieve good versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] The present invention will be described in further detail below in conjunction with the accompanying drawings.

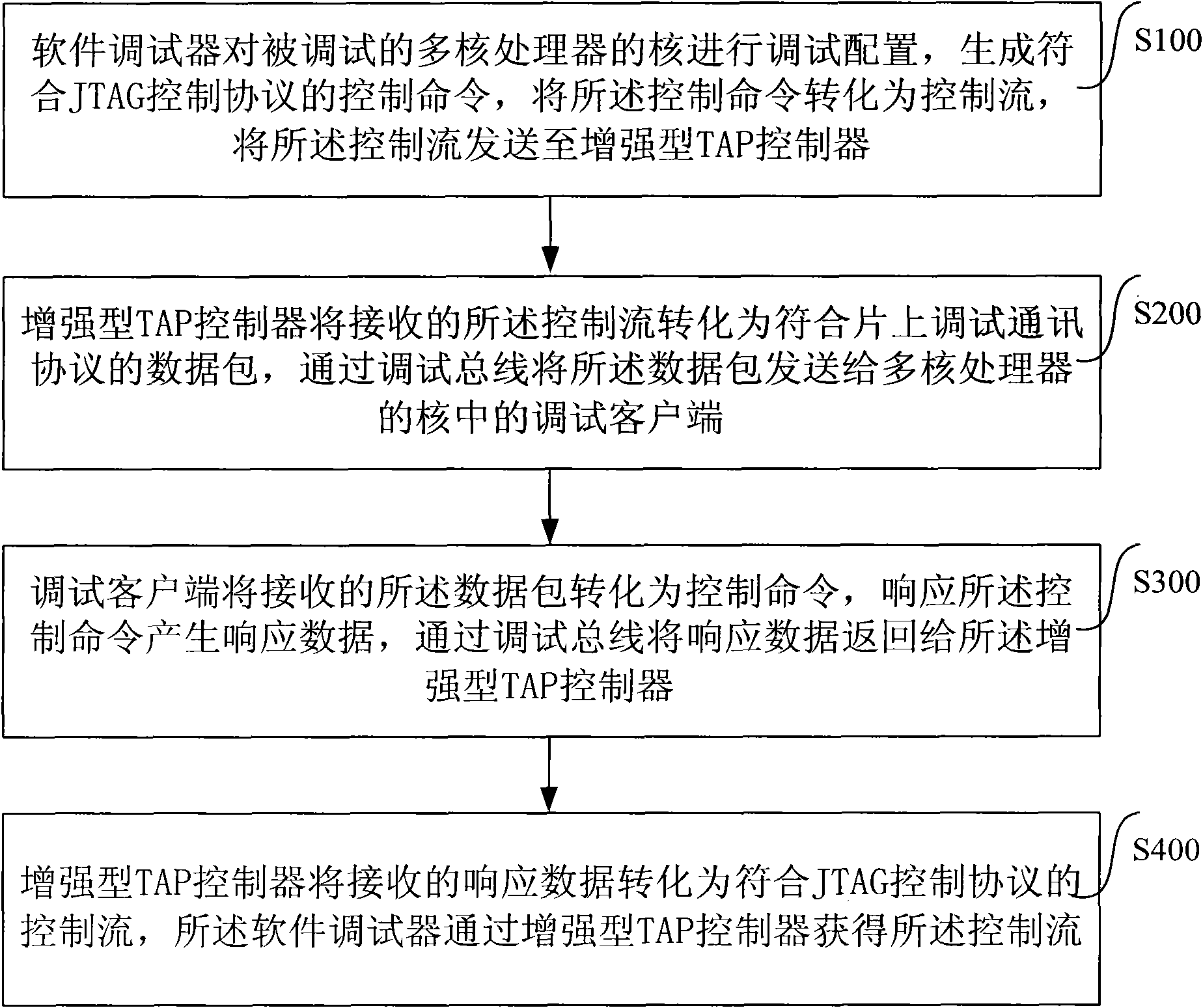

[0062] The flow process of the JTAG real-time on-chip debugging method of the multi-core processor of the present invention is as image 3 shown.

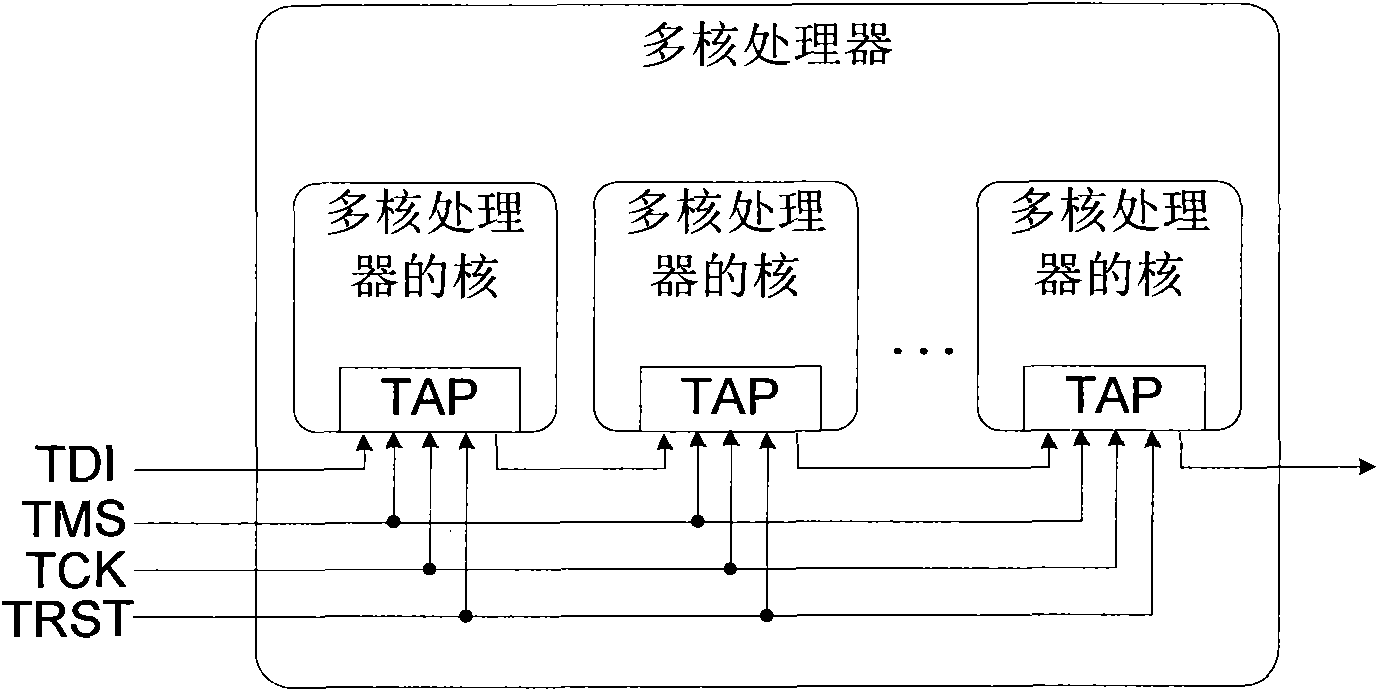

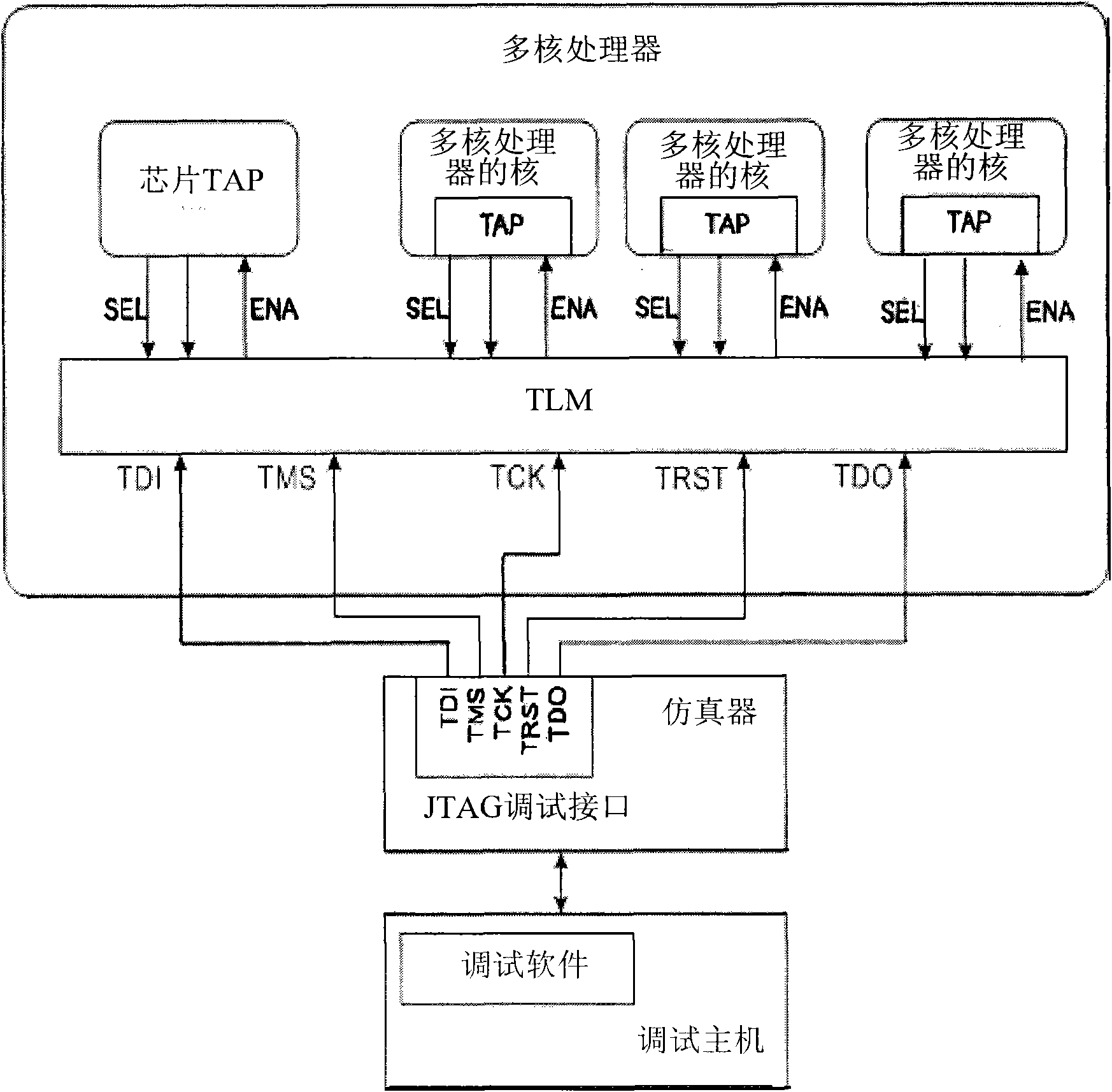

[0063] There are N cores in a multi-core processor, all of which are connected to the on-chip debug bus. The enhanced TAP controller interacts with the upper computer through the hardware port of the JTAG protocol of IEEE 1194.2, and interacts with the in-core debug client of the multi-core processor through the on-chip debug bus.

[0064] The method of the present invention specifically includes the following steps.

[0065] Step S100, the software debugger debugs and configures the core of the debugged multi-core processor, generates a control command conforming to the JTAG control protocol, converts the control command into a control flow, and sends the control flow to the enhanced TAP controller .

[0066]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More