Region-based photoelectric double-layer network-on-a-chip and routing method

A double-layer on-chip network and area technology, applied in electromagnetic wave transmission systems, transmission systems, digital transmission systems, etc., can solve problems affecting network performance, increasing implementation costs, and low wavelength utilization, so as to improve network performance and reduce congestion , Improve the effect of transmission speed and throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

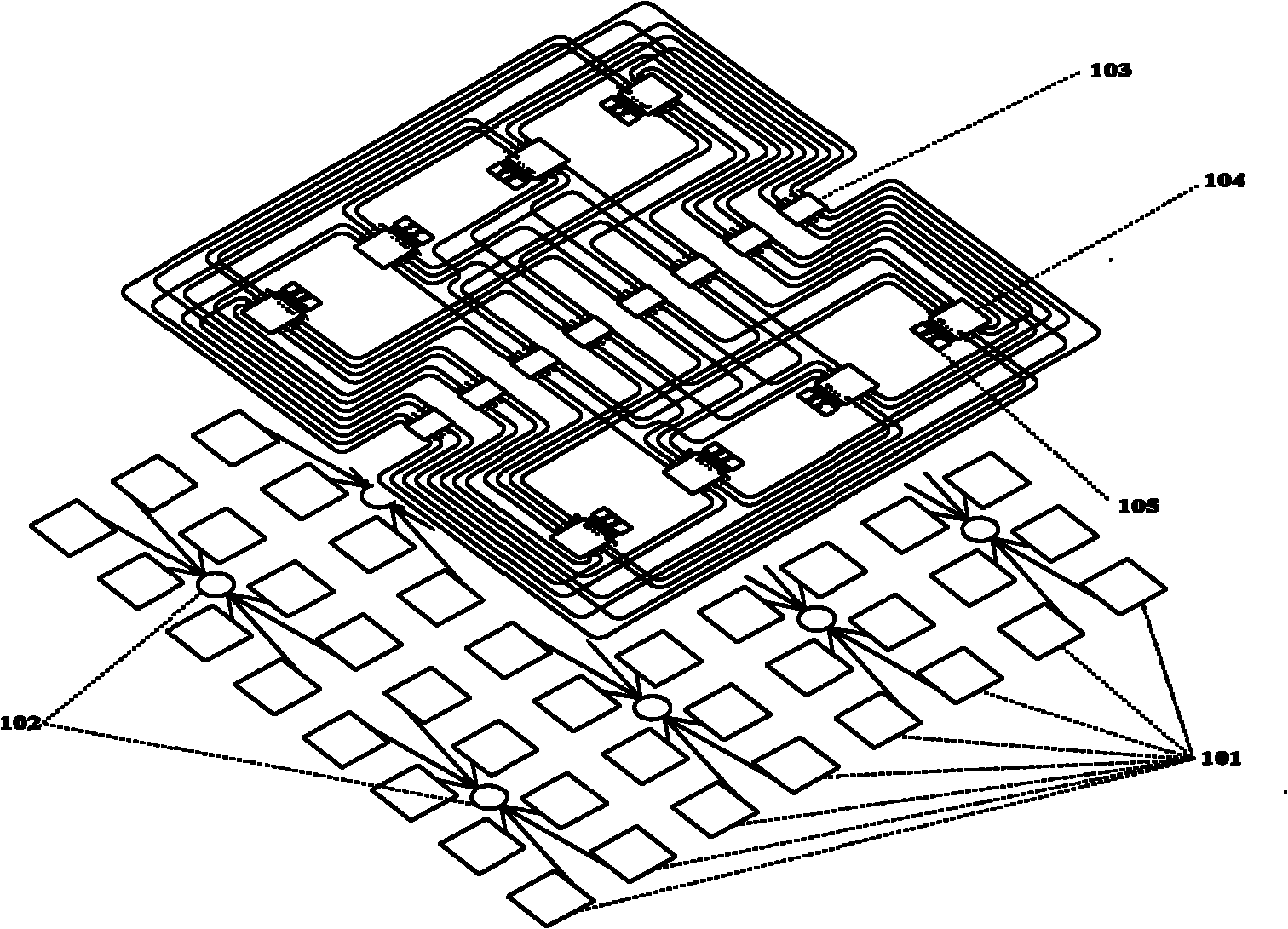

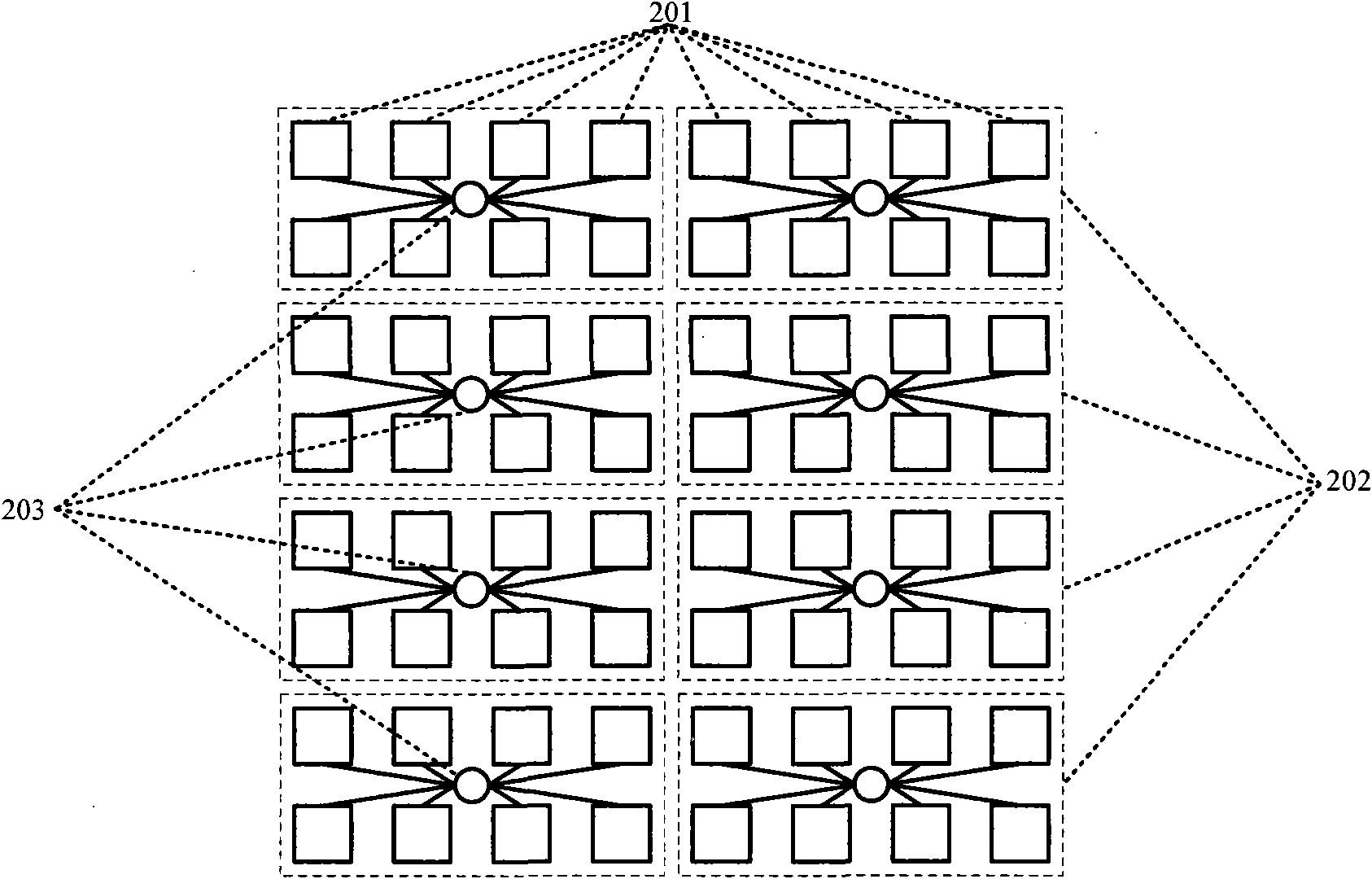

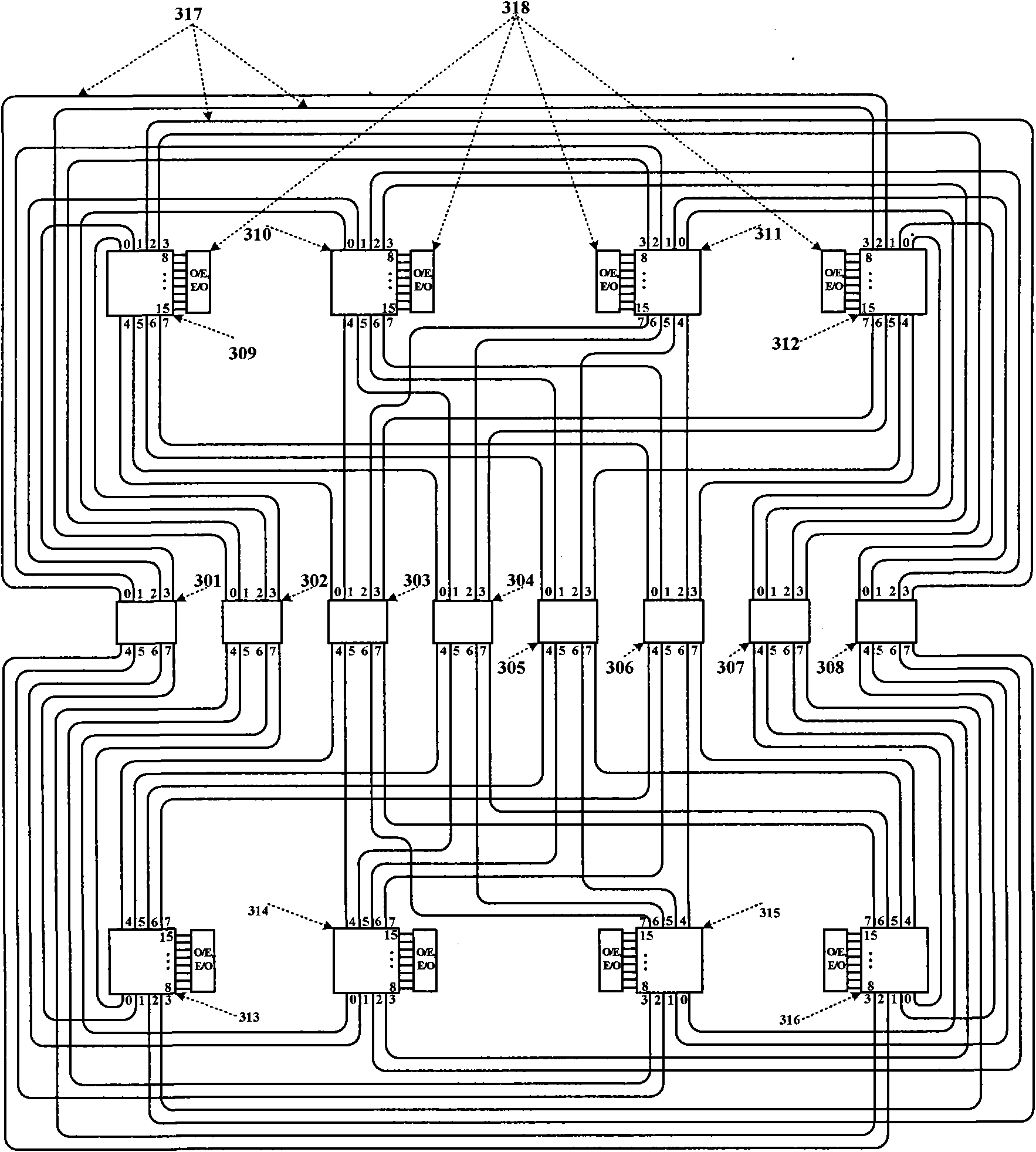

[0040] refer to figure 1 , the present invention discloses an area-based photoelectric double-layer on-chip network system, including: 64 processor cores 101, 8 electrical crossover matrix modules 102, 8 8-port optical routers 103 and 8 16-port optical routers 104. Considering the local characteristics of on-chip communication, the 64 processor cores are divided into 8 areas, and within each area, the 8 processor cores are interconnected by an electrical cross matrix module; between areas, the electrical The cross matrix module, 8-port optical router and 16-port optical router are divided into 3 levels, and each area is connected into a whole network according to the following rules:

[0041] Level 1, including 8 electrical cross matrix modules, each electrical cross matrix module has 16 ports, of which 8 ports are respectively connected to 8 processor cores, and the other 8 ports are respectively connected to the next 16 The 8 ports of the port optical router are connected o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More