Transistor test device and method

A testing device and transistor technology, applied in the field of microelectronics, can solve the problems of complicated and complicated testing of CMOS devices, and achieve the effect of monitoring structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

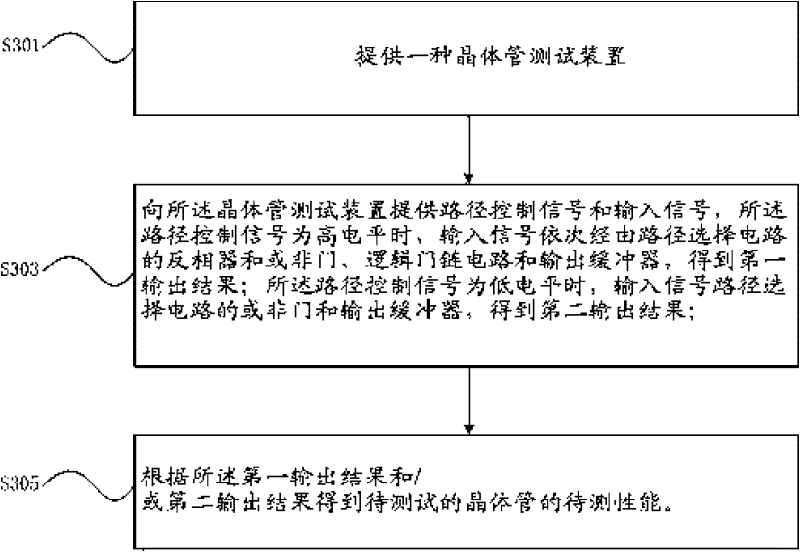

[0022] In the embodiment of the present invention, a transistor test scheme is provided. In this implementation scheme, a transistor test device with simple design and easy operation is used to test the transistor to be tested by using a test method corresponding to the test device to obtain a transistor The relevant performance of the transistor is used to determine whether the transistor meets the performance index requirements.

[0023] It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. The present invention will be described in detail below with reference to the accompanying drawings and examples.

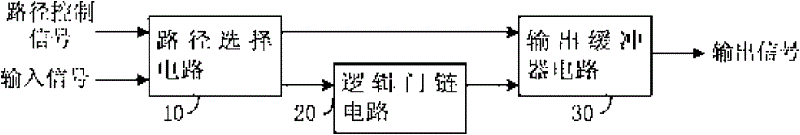

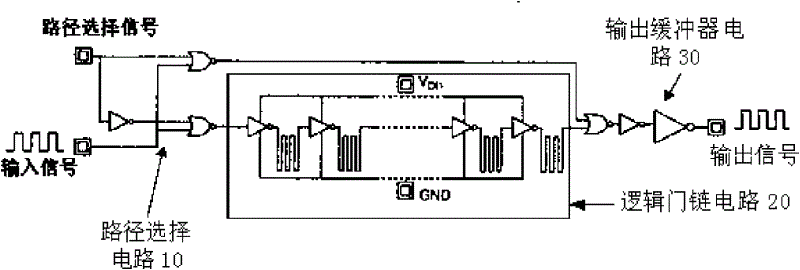

[0024] According to an embodiment of the present invention, a transistor testing device is provided. figure 1 It is a structural block diagram of a transistor testing device of the present invention. Such as figure 1 As shown, the transistor test setup includes: ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More