Wafer structure and manufacturing method thereof

A manufacturing method and wafer technology, which can be used in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as limiting the development breadth of semiconductors, and achieve the effect of simple process manufacturing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The specific implementation manners of the present invention will be described in further detail below with reference to the accompanying drawings. Throughout the description, like reference numerals refer to like parts.

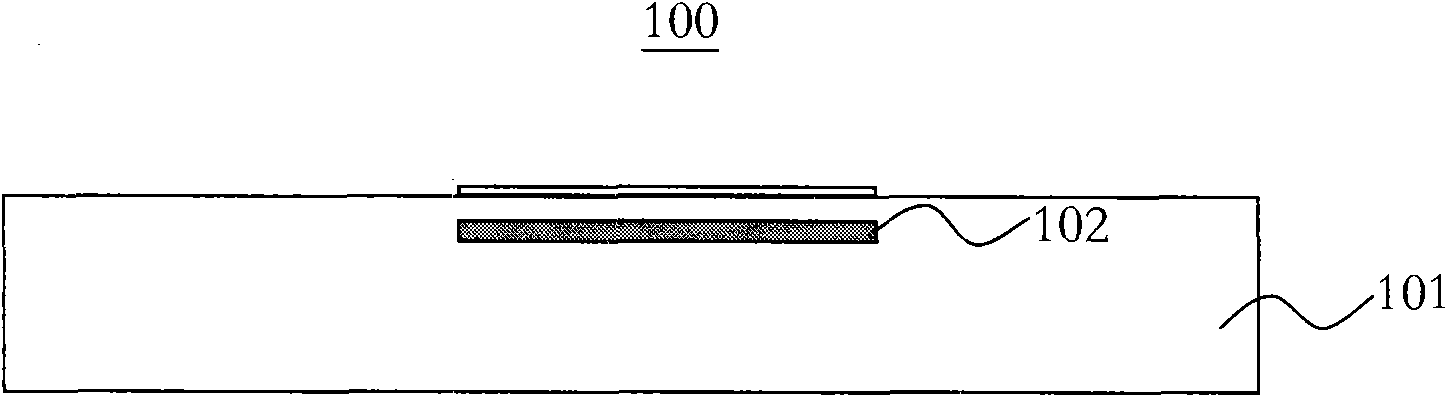

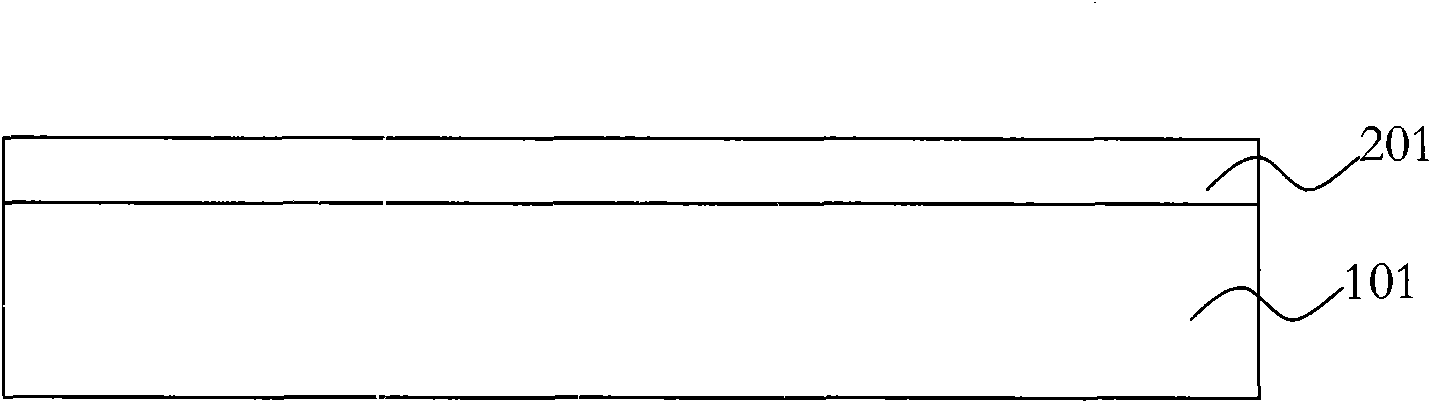

[0023] In the wafer structure and the manufacturing method of the wafer structure of the present invention, not only the substrate for manufacturing electrical devices but also the substrate for manufacturing optical devices is integrated on the wafer, realizing the integration of optoelectronic integrated components. In the manufacturing process of the wafer, the combination of the semiconductor substrate on the buried oxide layer and the semiconductor substrate not embedded in the buried oxide layer is distributed on the wafer, the process is simple and efficient, and it is beneficial to the later cutting process.

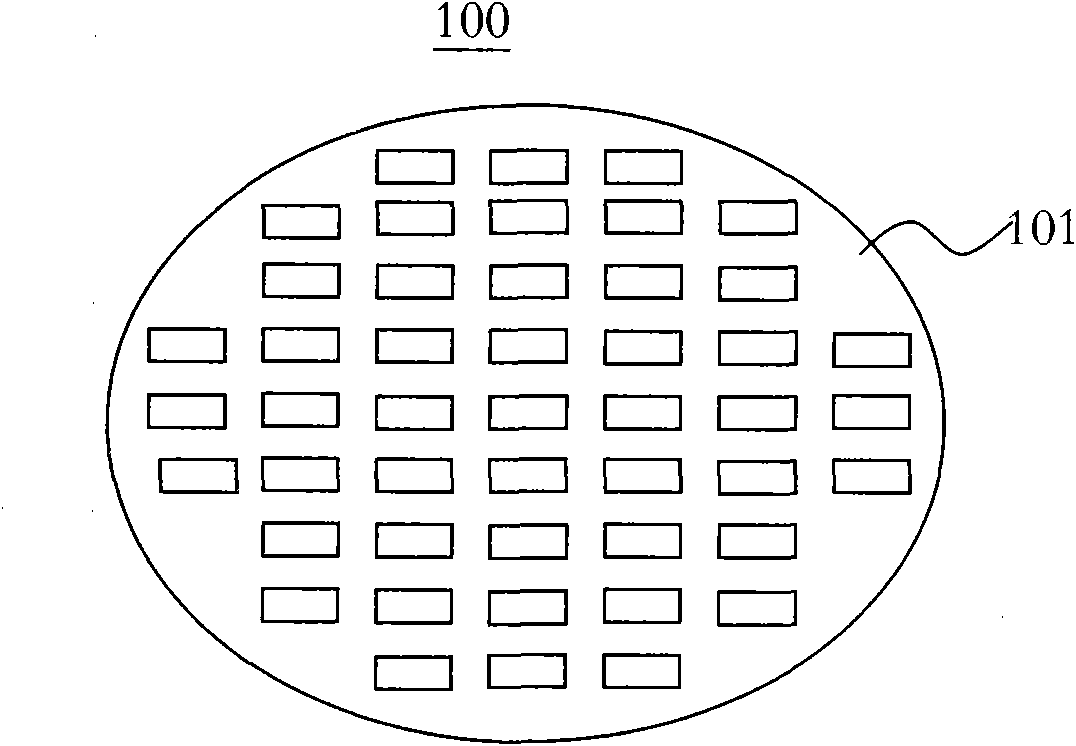

[0024] Figure 1a is a schematic top view of the wafer structure. Figure 1b is a schematic cross-sectional view of the wafer structur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More