On-chip network system supporting cache coherence and data request method

An on-chip network and high-speed cache technology, which is applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve problems such as difficulty in expanding access delays in directories, complex design of consistency protocols, etc., to reduce storage and delay overhead, simplify Design and verify process, effect to improve performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

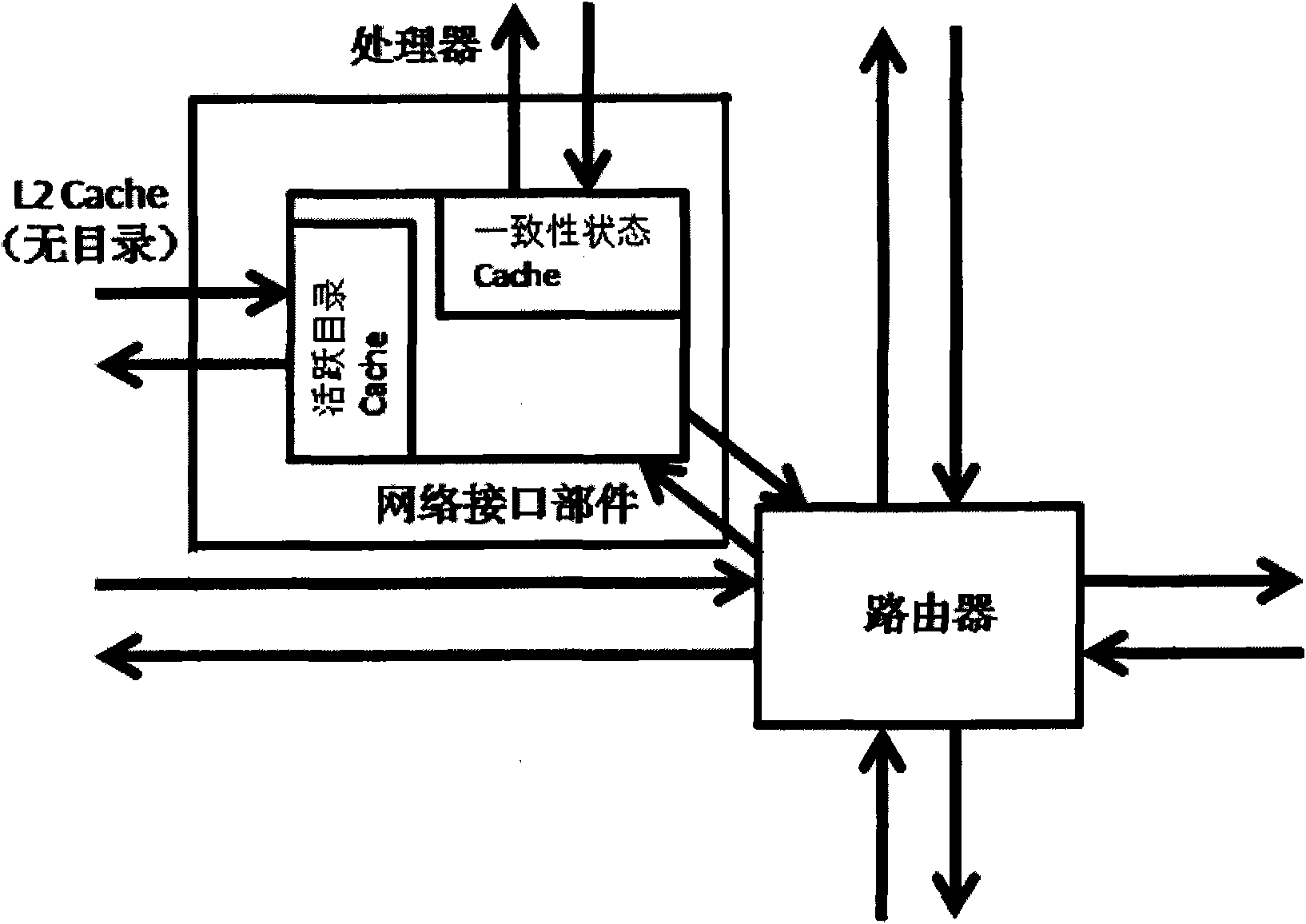

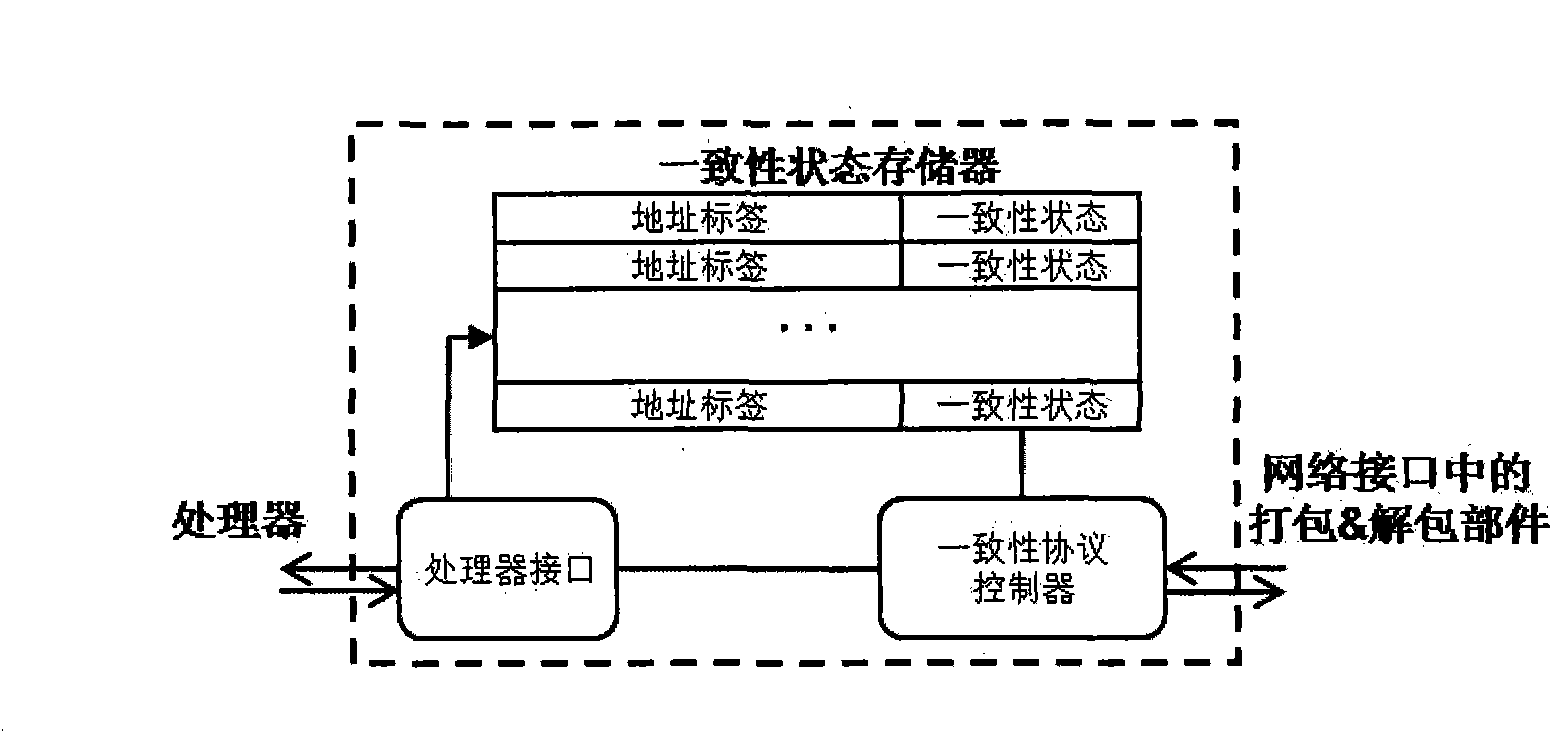

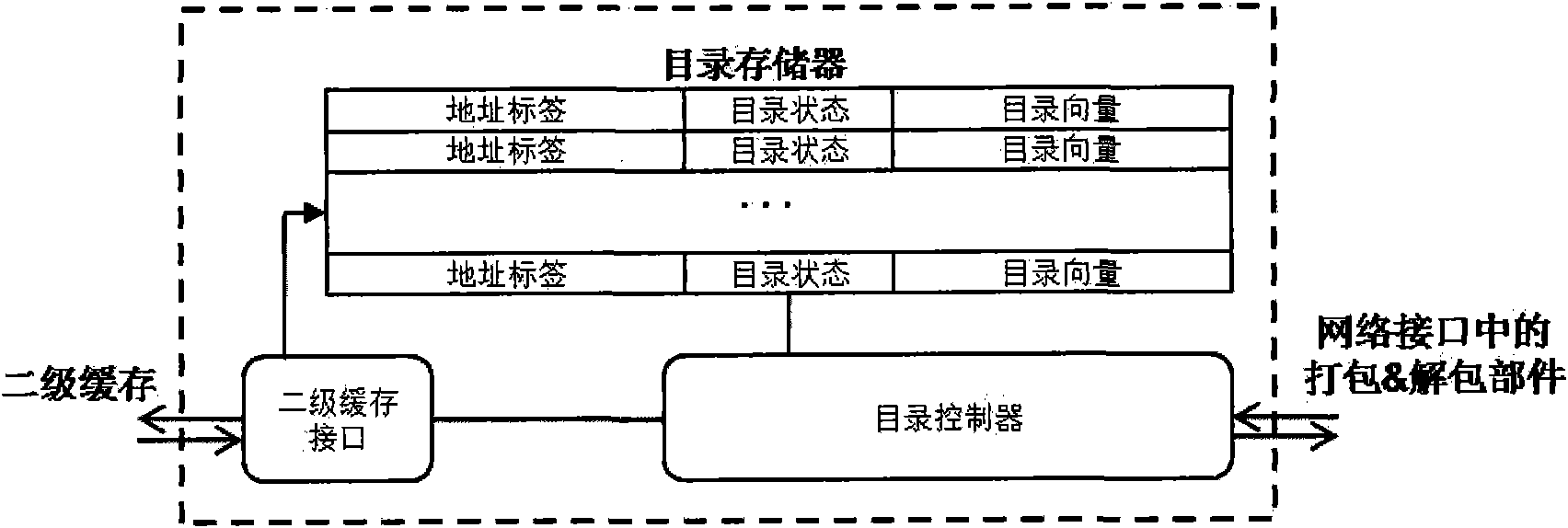

[0057] In multi-core processors, the operation of the cache coherence protocol is transmitted through the on-chip network. The private cache (Level 1 cache) miss request of the multi-core processor is sent to the on-chip network through the network interface component, and the response information is also transmitted to the router of the requesting node through the on-chip network, and then returned to the multi-core processor through the network interface component. Access to directories and data in the shared L2 cache is also transmitted through the network interface component. The response message of the shared secondary cache to the multi-core processor and the invali...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More