Integrated circuit structure

An integrated circuit and electrical connection technology, which is applied in the field of package integration including integrated circuit chips and package substrates, can solve problems such as short circuit, stress generation, and pitch change

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will provide many different embodiments to implement different features of the present invention. However, these examples are not intended to limit the present invention. The specific embodiments discussed below are only used to illustrate the manufacture and use of the embodiments of the present invention, but do not limit the scope of the present invention.

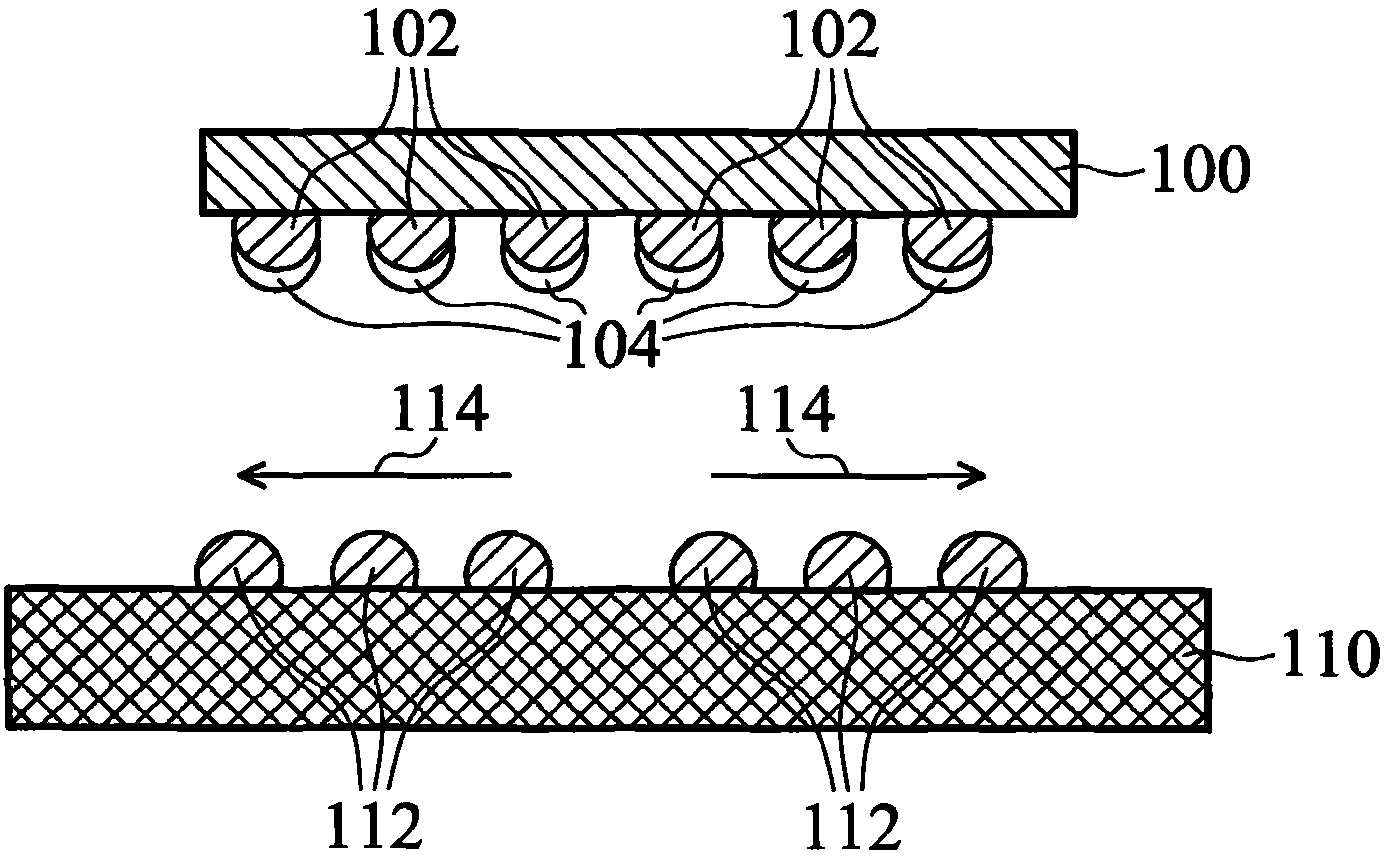

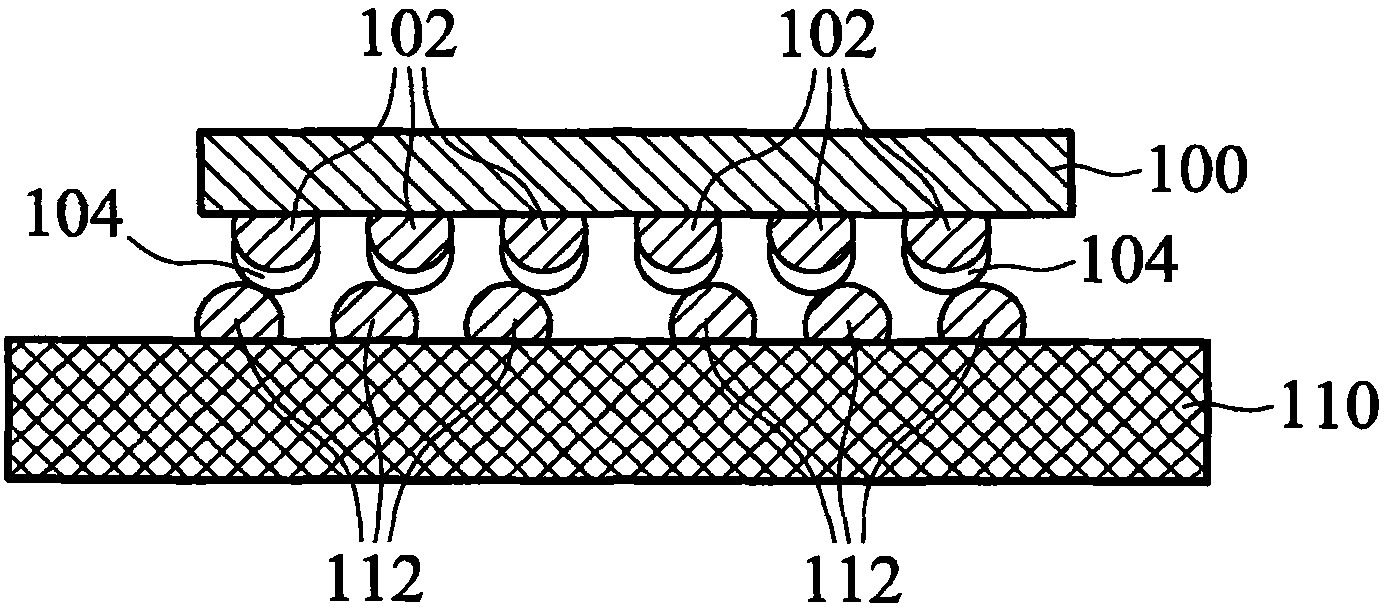

[0038] Herein, novel methods of fabricating integrated circuits according to embodiments of the present invention will be disclosed, an embodiment will be illustrated at various intermediate stages of manufacture, and variations of the embodiment will be discussed. In various drawings and embodiments of the present invention, similar reference numerals represent similar components.

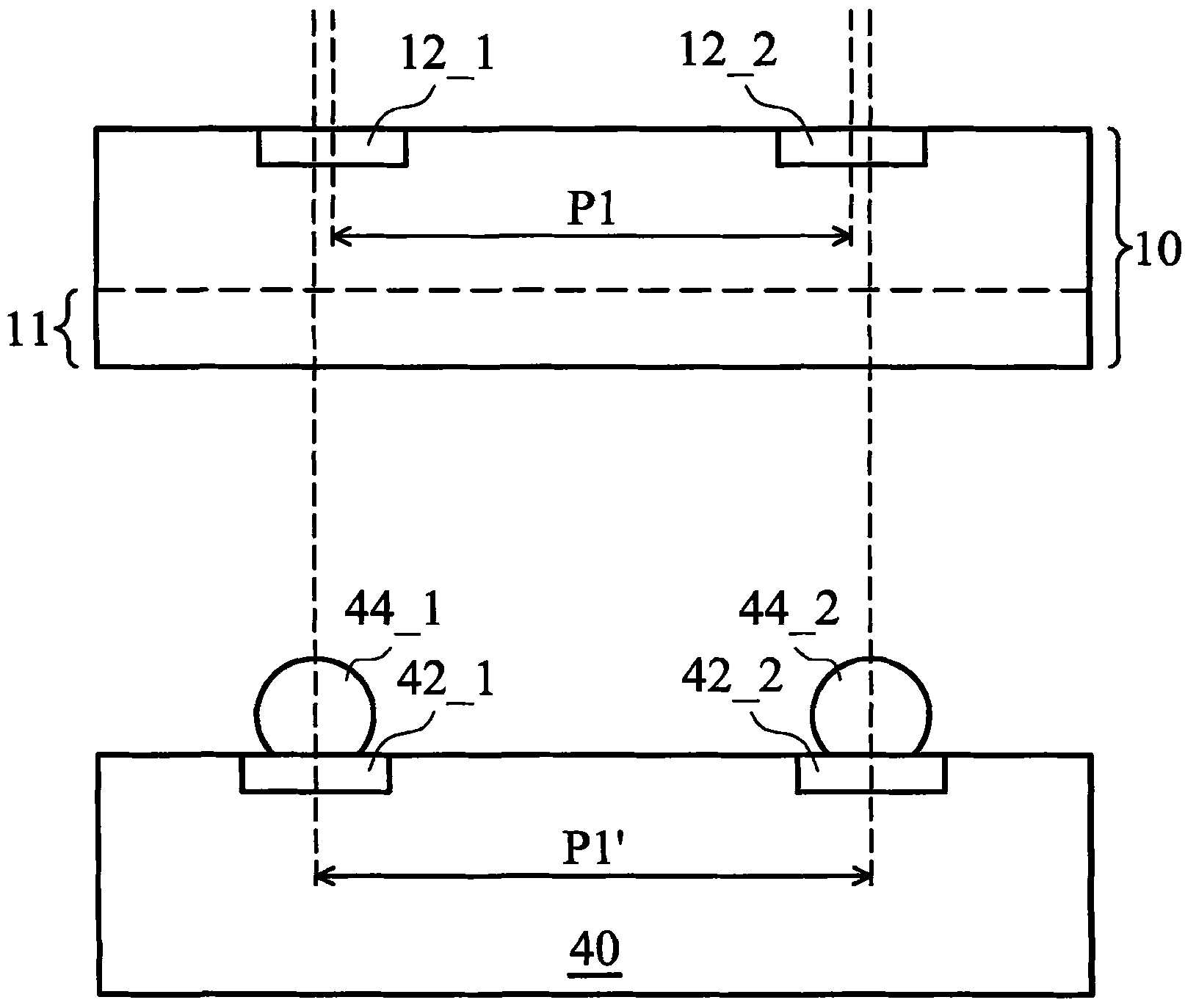

[0039] Figure 3A A cross-sectional view of the semiconductor chip 10 and the packaging substrate 40 is shown. It is understood that the semiconductor chip 10 and the package substrate 40 shown in the same pl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com