Rapid simulation method for anti-radiation property of field programmable gate array (FPGA)

A technology of anti-radiation and gate array, applied in the electronic field, can solve the problem of high hardware cost, and achieve the effect of tight and efficient error injection process, tight connection and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0042] Embodiment 1 Simulation of real radiation environment

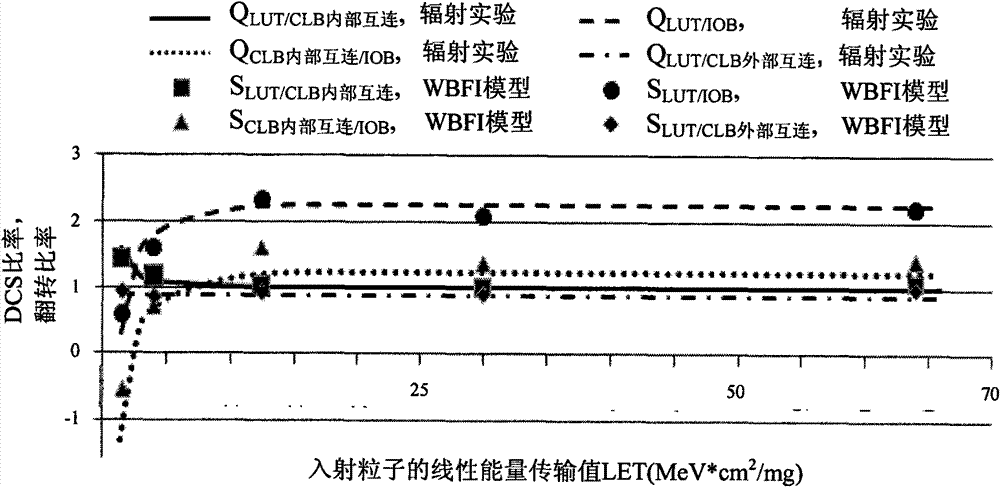

[0043] In order to simulate the single event flip effect caused by different particles, different LET values were set for the WBFI model in the experiment to count the ratio of the number of flips of different types of programmable points S a / b (LET). Each experiment simulates 10,000 single-event flip-induced changes in programmable point values, and the results are as follows image 3 shown. Depend on image 3 It can be seen that the number of flips between different types of programmable points under the WBFI model is more than S a / b (LET) can well fit the DCS ratio curve Q between different kinds of programmable points in real radiation experiments a / b (LET), which proves that the model of the present invention can accurately simulate the error injection in the real radiation experiment environment.

Embodiment 2

[0044] Embodiment 2 Simulation experiment of FPGA anti-radiation performance

[0045] The FDP series FPGA chip FPGA-2 developed by Fudan University supports dynamic partial reconfiguration and JTAG boundary scan technology, and can conveniently realize the error injection simulation platform proposed by the present invention. Therefore, the present invention utilizes FPGA-2 to set up the error injection system based on WBFI model, test circuit board such as Figure 4 shown.

[0046] The present invention uses an 18-bit non-pipeline multiplier based on a modified Booth code and a Wallace Tree structure after triple module redundancy (TMR) as a test circuit. The utilization rate of the look-up table of the test circuit after triple-mode redundancy under the FPGA-2 is 91%, the utilization rate of the programmable logic unit is 99%, and the utilization rate of the IOB is 50%. Among them, the open source tool BL-TMR [5] provided by Brigham Young University (Brigham Young Universi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More