A debugging structure for GPU unified coloring processing array

An array and unified technology, applied in the debugging structure field of GPU uniform dyeing processing array, can solve problems such as poor portability, inability to guarantee circuit, safety, reliability, security risks, etc., and achieve the goal of reducing difficulty and reducing the range of storage space Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

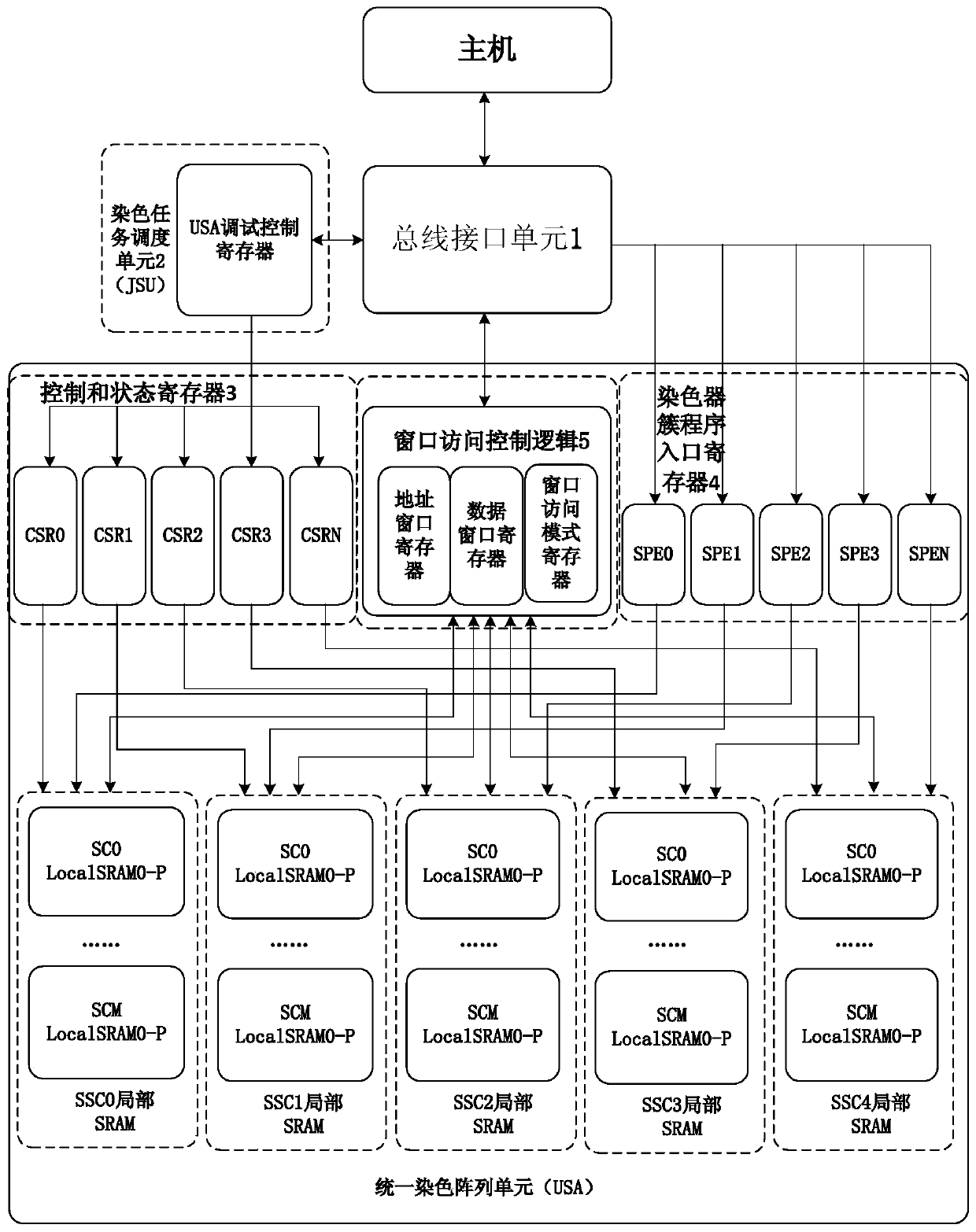

[0051] Such as figure 1 As shown, the host can configure the window access mode register in the window control logic through the register channel in the PCIe module, so as to choose to work in the normal working mode or the debugging working mode.

[0052] In the debugging working mode, there may be differences in the access procedures of different implementation solutions, but this does not make the essence of the corresponding implementation solutions deviate from the spirit and scope of the solutions of the present invention. The typical process of host debugging access to the unified dyeing array is as follows:

[0053] In the first step, the host sequentially accesses the address and data window registers in the window control logic through the register channel of the bus interface unit, writes the local memory address and write flag of the shader cluster to be written, and the data to be written. The window control logic will write any specified dyeing task attribute da...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More