Semiconductor structure and manufacture method thereof

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of reducing the switching speed of components, improving on-resistance, difficult to achieve high breakdown voltage and low on-resistance at the same time, etc. problem, to achieve the effect of reducing the on-resistance and increasing the breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

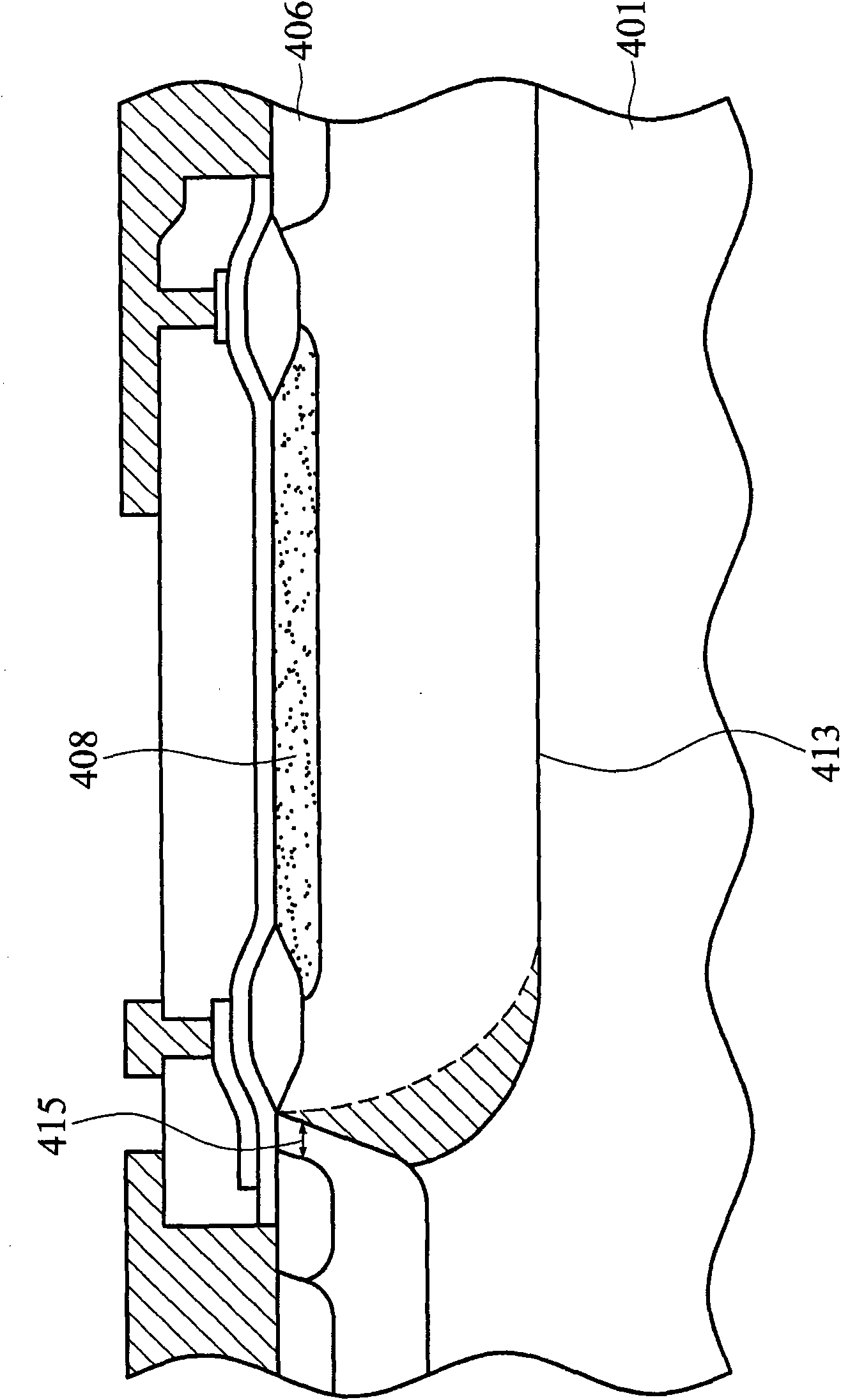

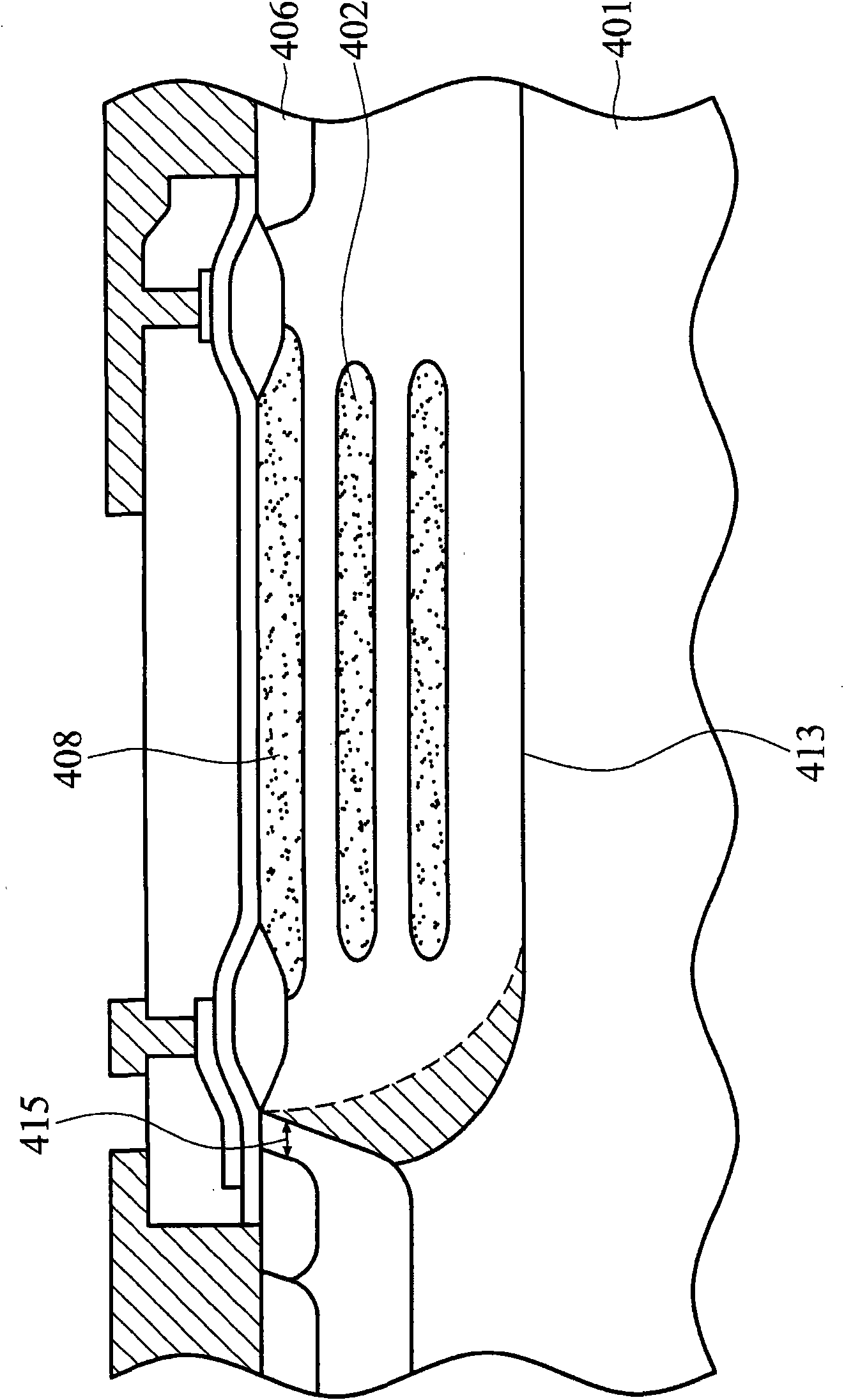

[0013] Embodiments of the present invention provide a semiconductor device and a manufacturing method thereof. The manufacturing method and usage method of each embodiment are described in detail below, and are illustrated with accompanying drawings. Wherein, the same reference numerals used in the drawings and the specification represent the same or similar components. In the accompanying drawings, for the sake of clarity and convenience of illustration, the shapes and thicknesses of the embodiments may be unrealistic. The following descriptions specifically illustrate the various elements of the device of the present invention or their integration. However, it should be noted that the above-mentioned elements are not particularly limited to those shown or described, but are known to those skilled in the art. Various forms, moreover, when a layer of material is on top of another layer of material or substrate, it may be directly on its surface or additionally interposed with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com