Method for realizing automated ECO (Engineering Change Order) netlist in digital IC (Integrated Circuit) design process

A netlist and digital technology, applied in the field of automatic ECO netlist, can solve problems such as impossibility, error-prone, heavy workload, etc., and achieve the effects of less error-prone, error-avoiding, and high process efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

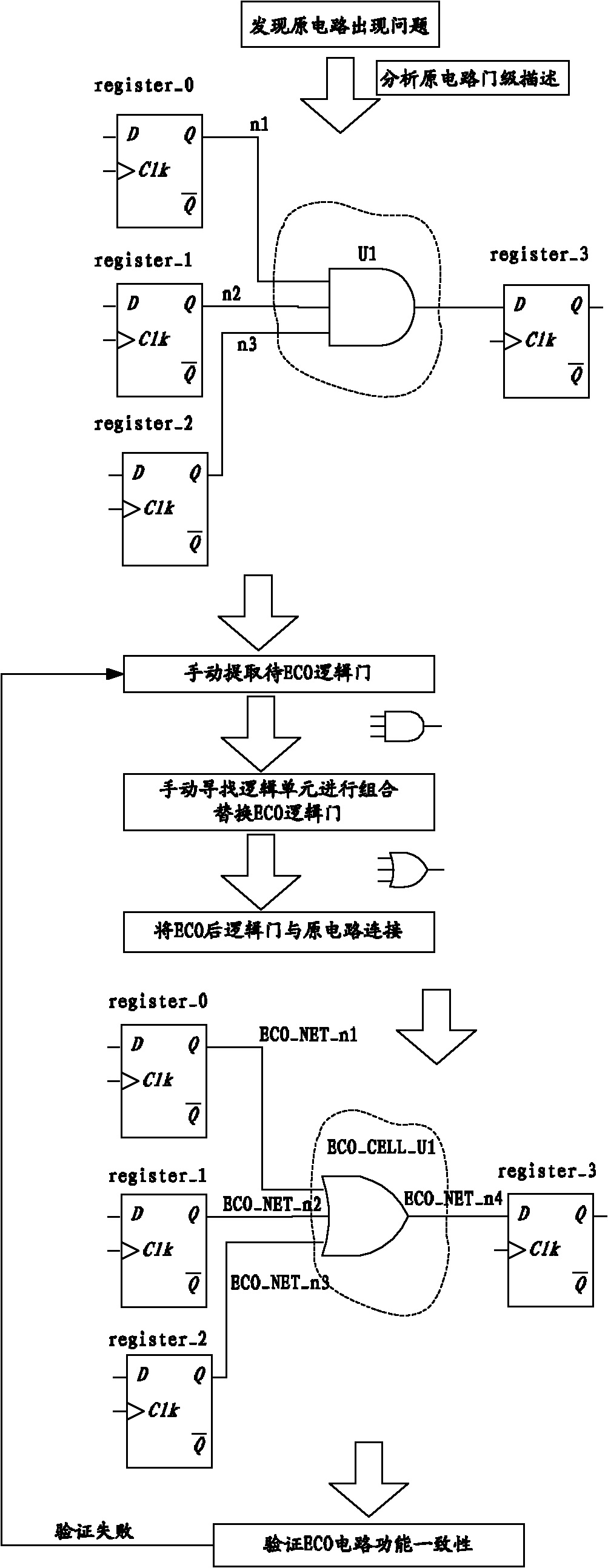

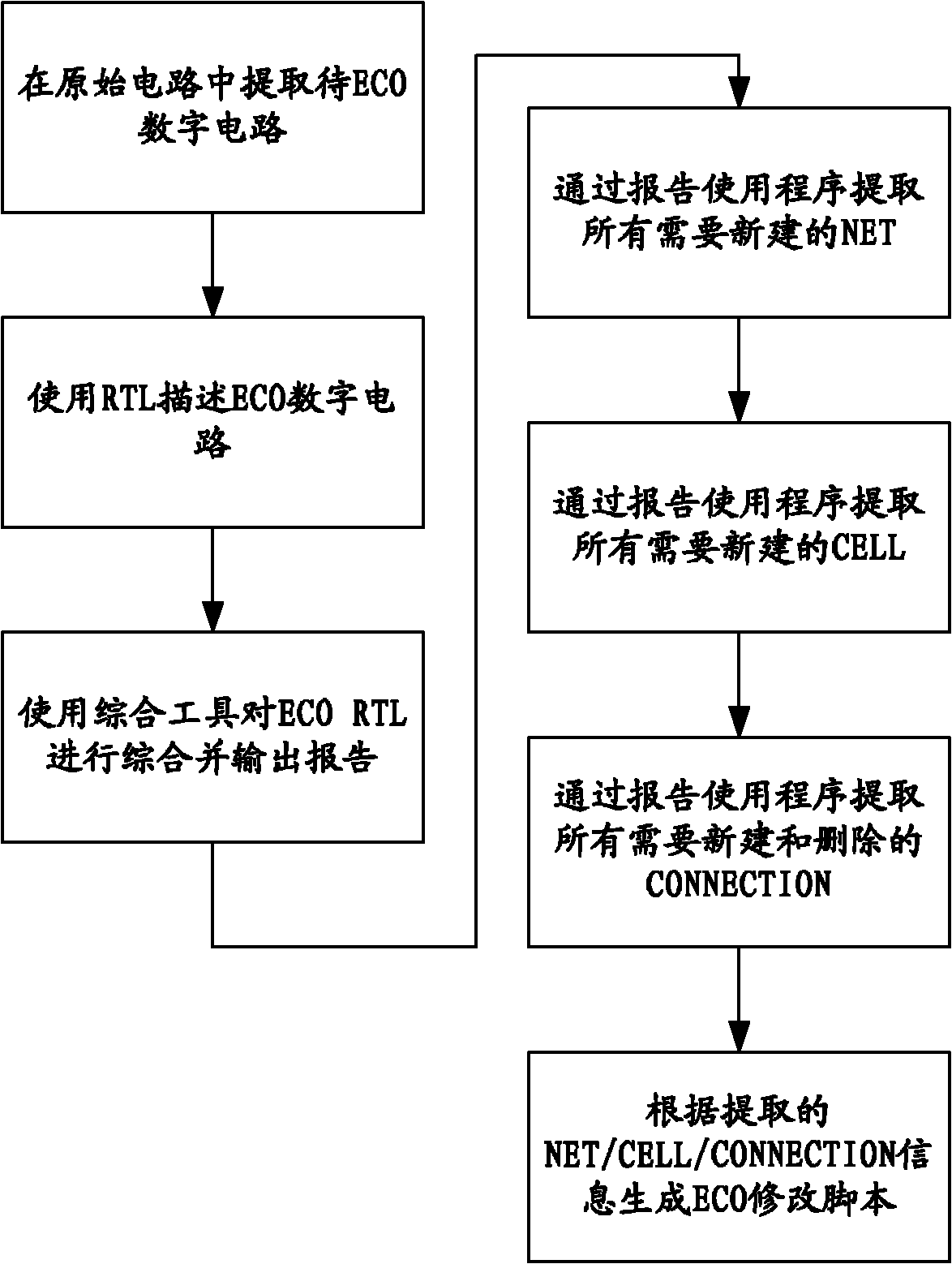

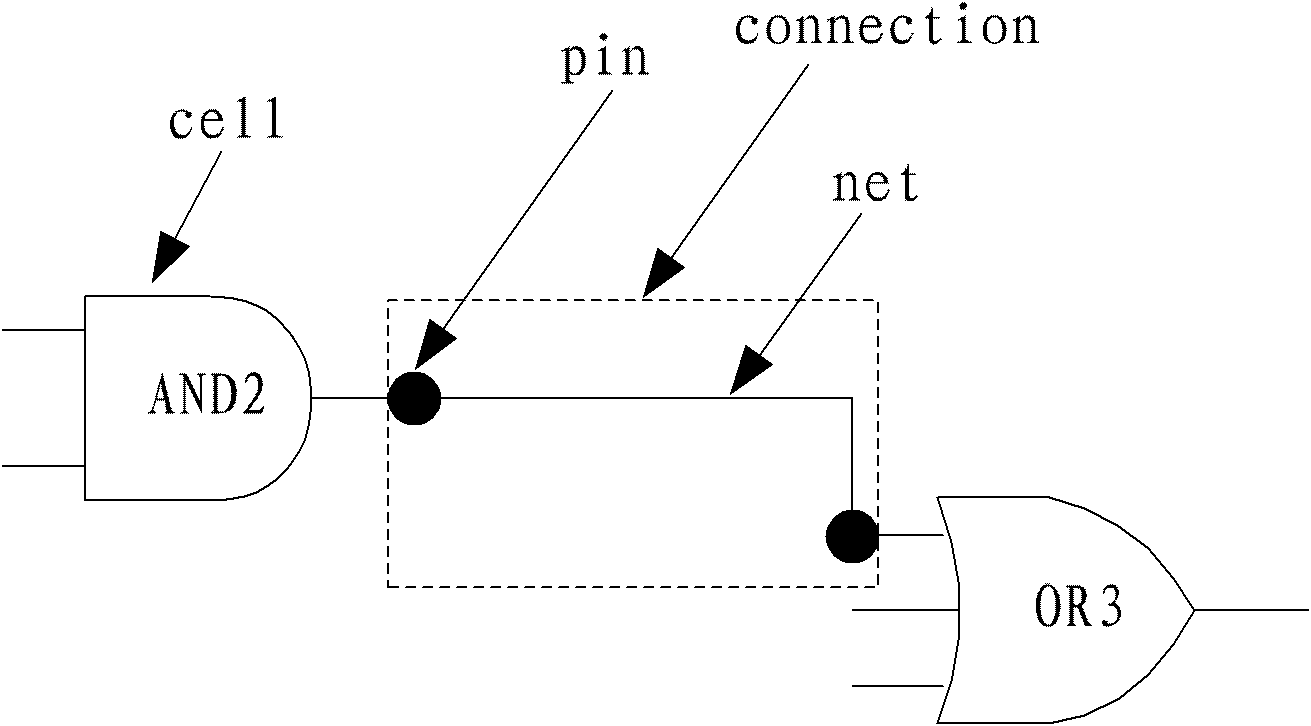

[0045] figure 2 Shown is a schematic flow diagram of a method for realizing an automated ECO netlist in a digital IC design flow of the present invention. Figure 4 It is a schematic diagram of the ECO process of the automatic netlist of the present invention. Including the following steps:

[0046] Step 100: Extract the digital circuit to be ECO from the original circuit, and use RTL to describe the digital circuit of ECO; see Figure 4 In the "Manually complete RTL code modification" section.

[0047] Step 200: Output the report used to generate the ECO modification script through the EDA tool; see Figure 4 "Automatically generate ECO modification script" section.

[0048] Step 300: Use a comprehensive tool to output a report to generate an ECO modification script. See Figure 4 In the "Automatically complete synthesis and report output" section.

[0049] The above steps are described in detail below:

[0050] Step 100 includes:

[0051] Step 101: First, find all input register...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More