P-channel depletion MOS (metal oxide semiconductor) transistor and preparation method thereof

A MOS transistor and depletion-type technology, which is applied in the field of P-channel depletion-type MOS transistors and its preparation, can solve the problems of increased production costs, complicated manufacturing processes, and waste of resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

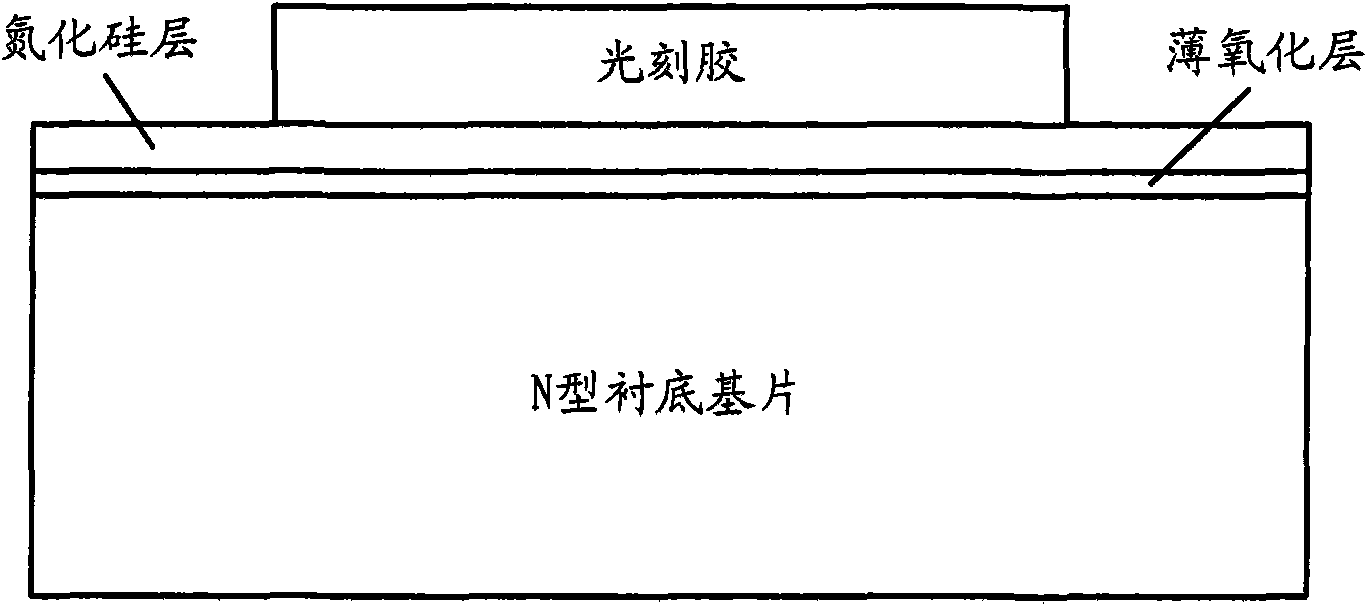

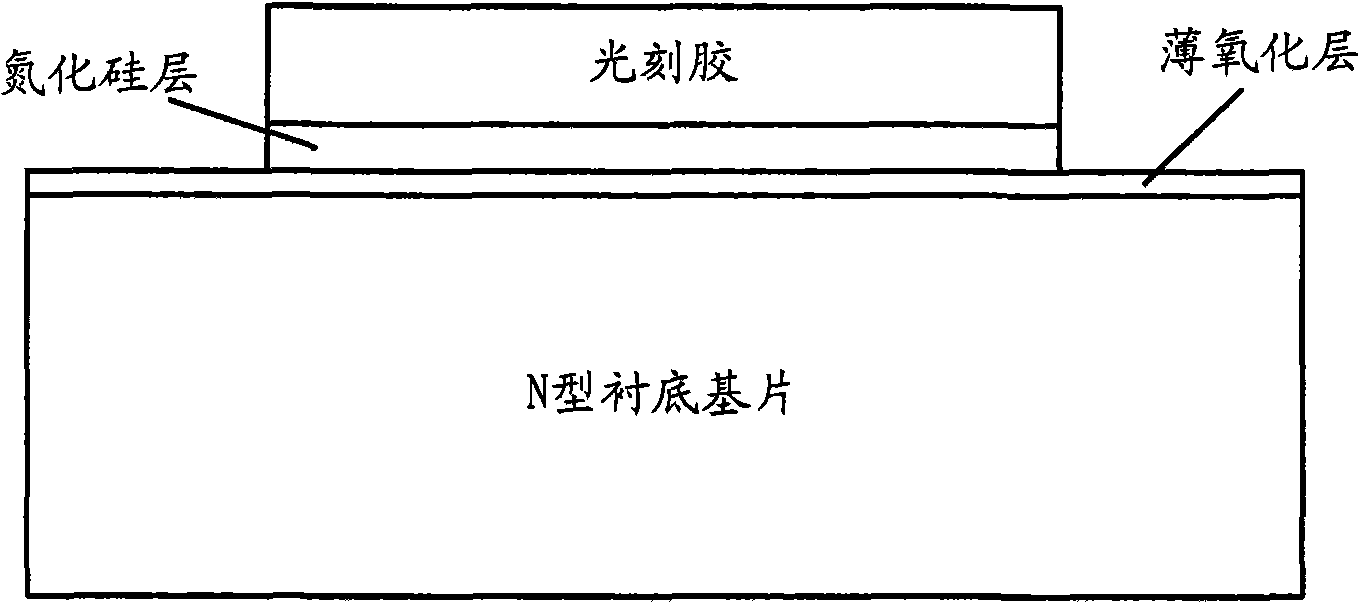

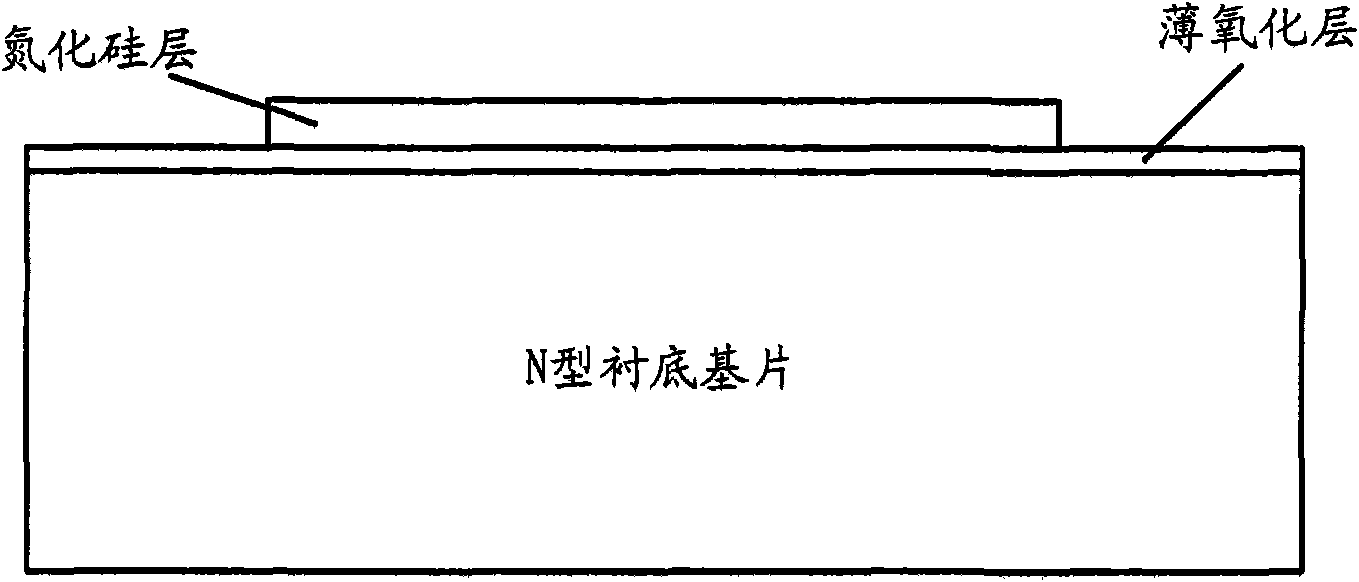

[0097] The preparation method of the P channel depletion mode MOS transistor provided by the embodiment of the present invention, its process is as follows Figure 14 As shown, it mainly includes the following process steps:

[0098] Step S11: preparing a field oxide layer on the upper surface of the N-type substrate outside the region where the MOS electrodes are to be prepared.

[0099] Step S12: preparing a gate oxide layer in the area not covered by the field oxide layer.

[0100] Step S13 : preparing an undoped polysilicon layer in the area where the MOS gate is to be prepared on the gate oxide layer.

[0101] Step S14: implant a set dose of boron ions from the area above the N-type substrate that is not covered by the field oxide layer, so that the undoped polysilicon layer forms a P-type polysilicon layer, and the undoped polysilicon layer A P-type source (drain) region is formed with the surface layer region above the N-type substrate covered by the field oxide layer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com