Patents

Literature

96results about How to "Increase the turn-on voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

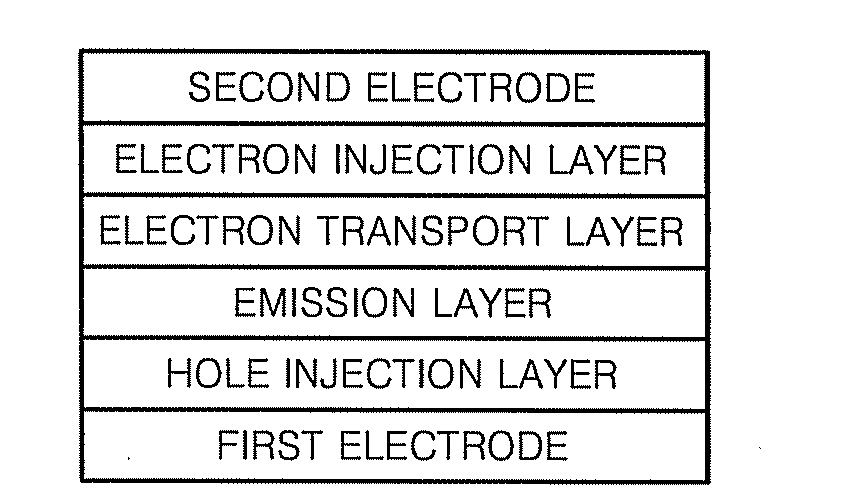

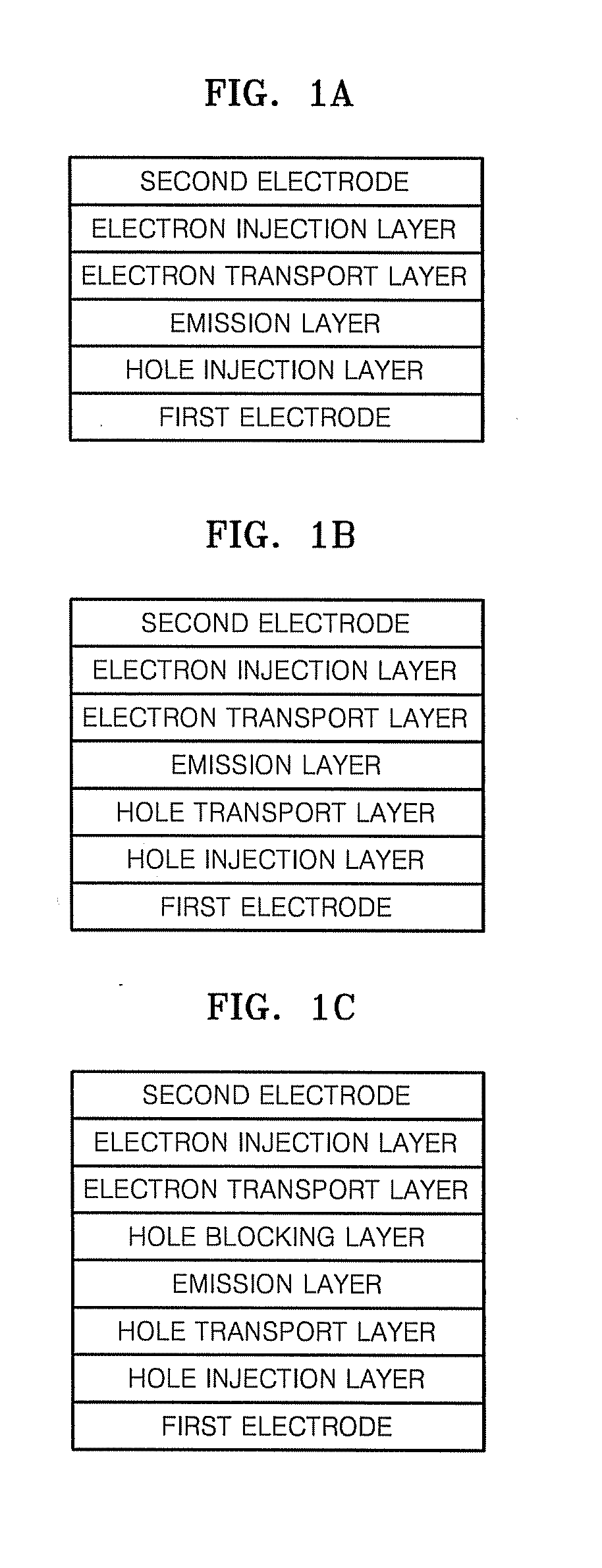

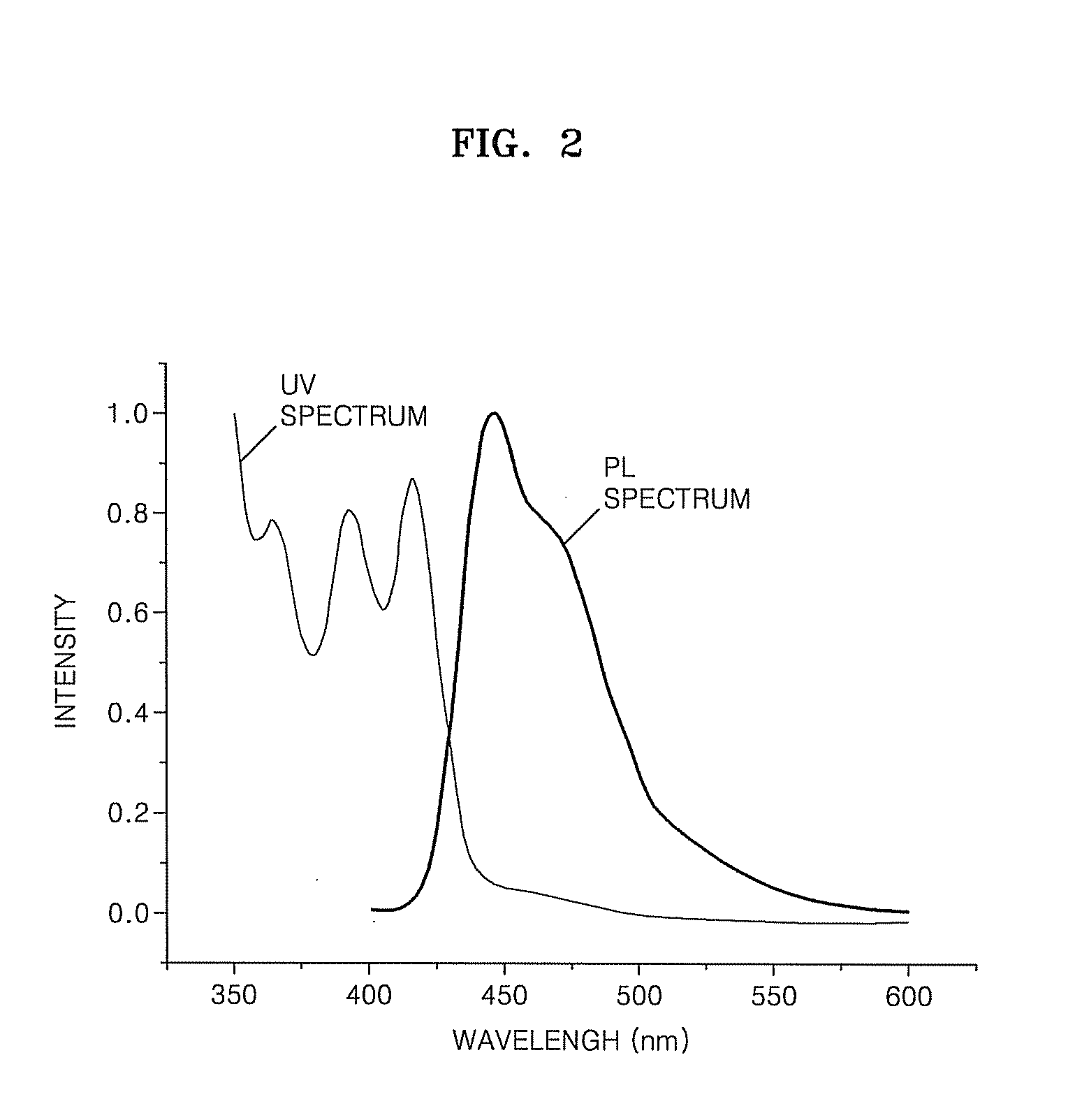

Organic light emitting compound and organic light emitting device comprising the same, and method of manufacturing the organic light emitting device

InactiveUS20080122344A1Improve solubilityImprove thermal stabilityOrganic chemistryDischarge tube luminescnet screensOrganic light emitting deviceHigh color

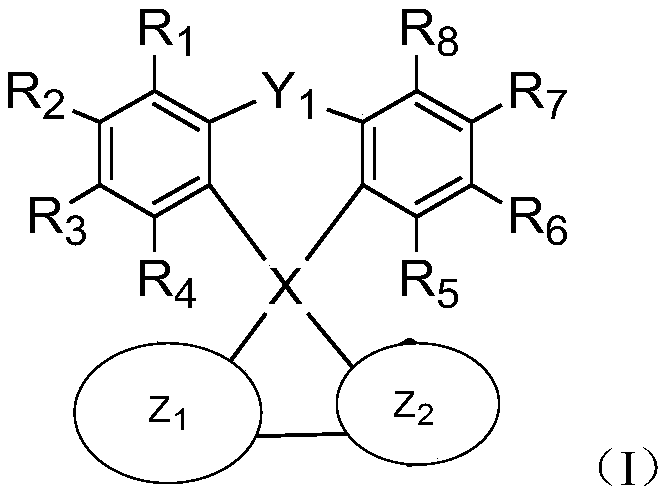

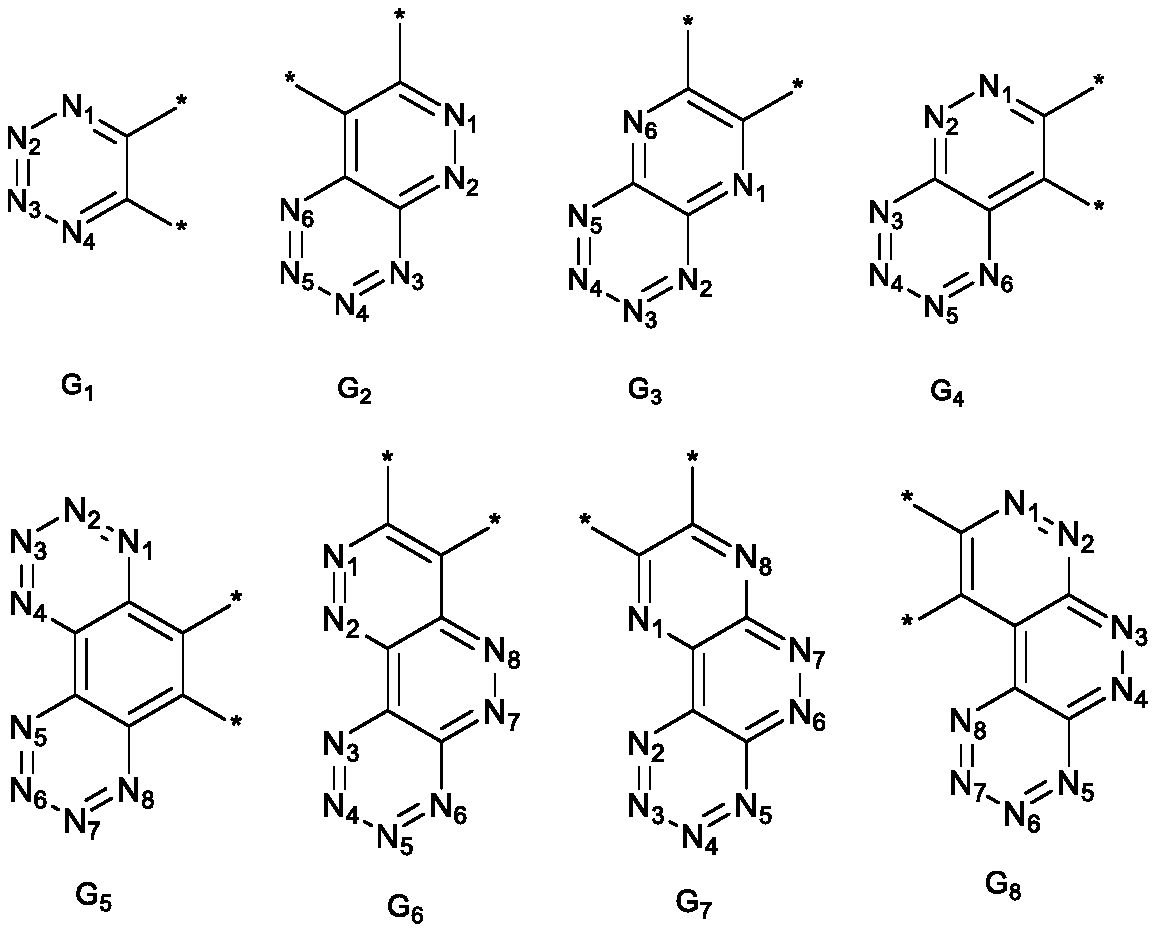

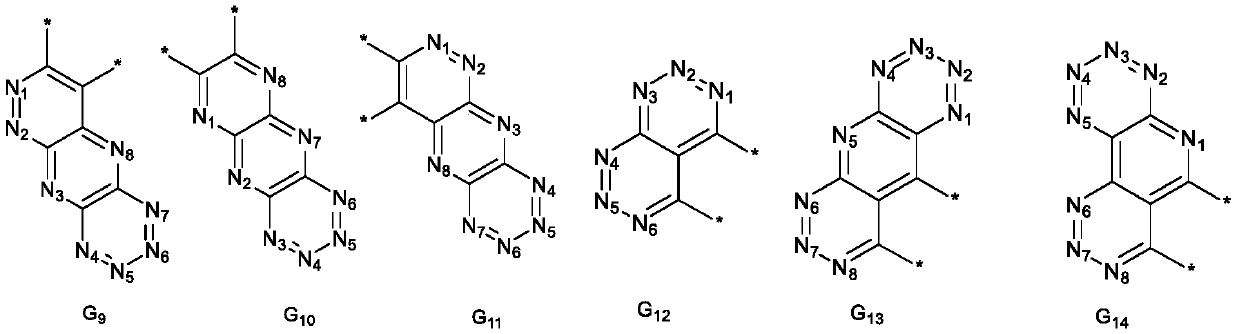

Provided are an organic light emitting compound represented by Formula 1 below, an organic light emitting device comprising the same, and a method of manufacturing the light emitting device:wherein CY1, CY2, Ar1, R1 and R2 are described in the detailed description of the invention. An organic light emitting device comprising the organic light emitting compound has low turn-on voltage, high efficiency, high color purity and high luminance.

Owner:SAMSUNG DISPLAY CO LTD

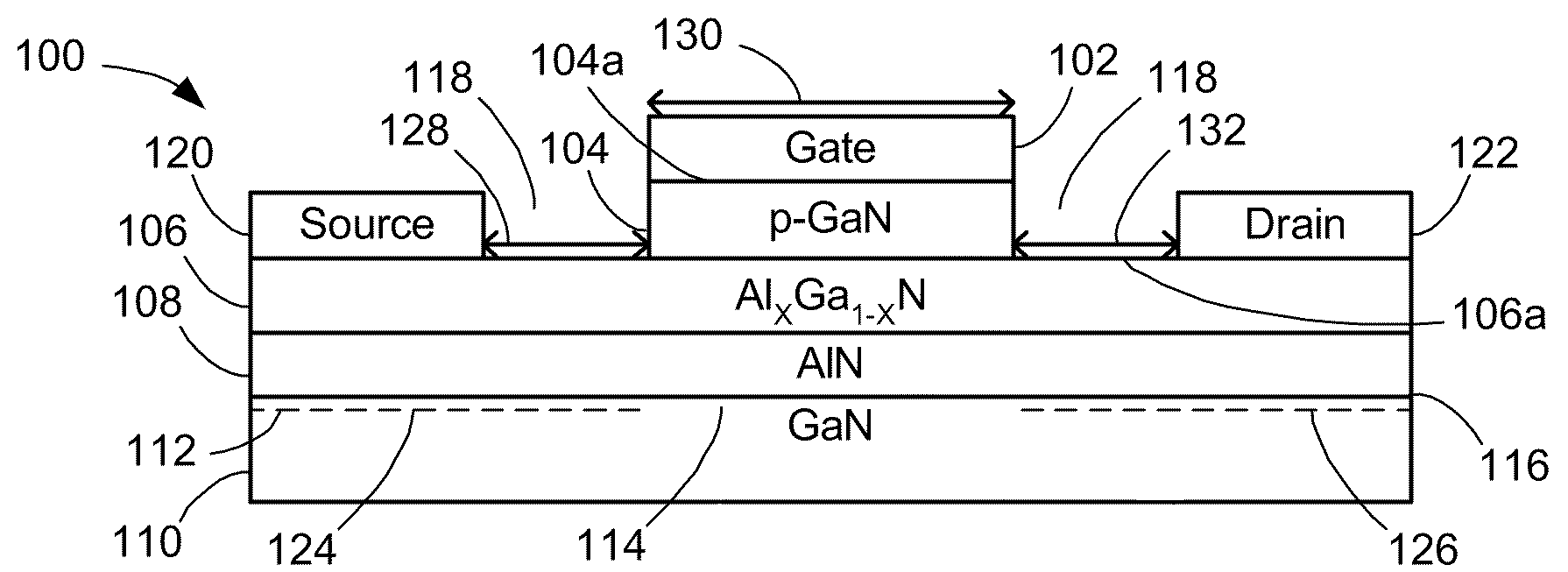

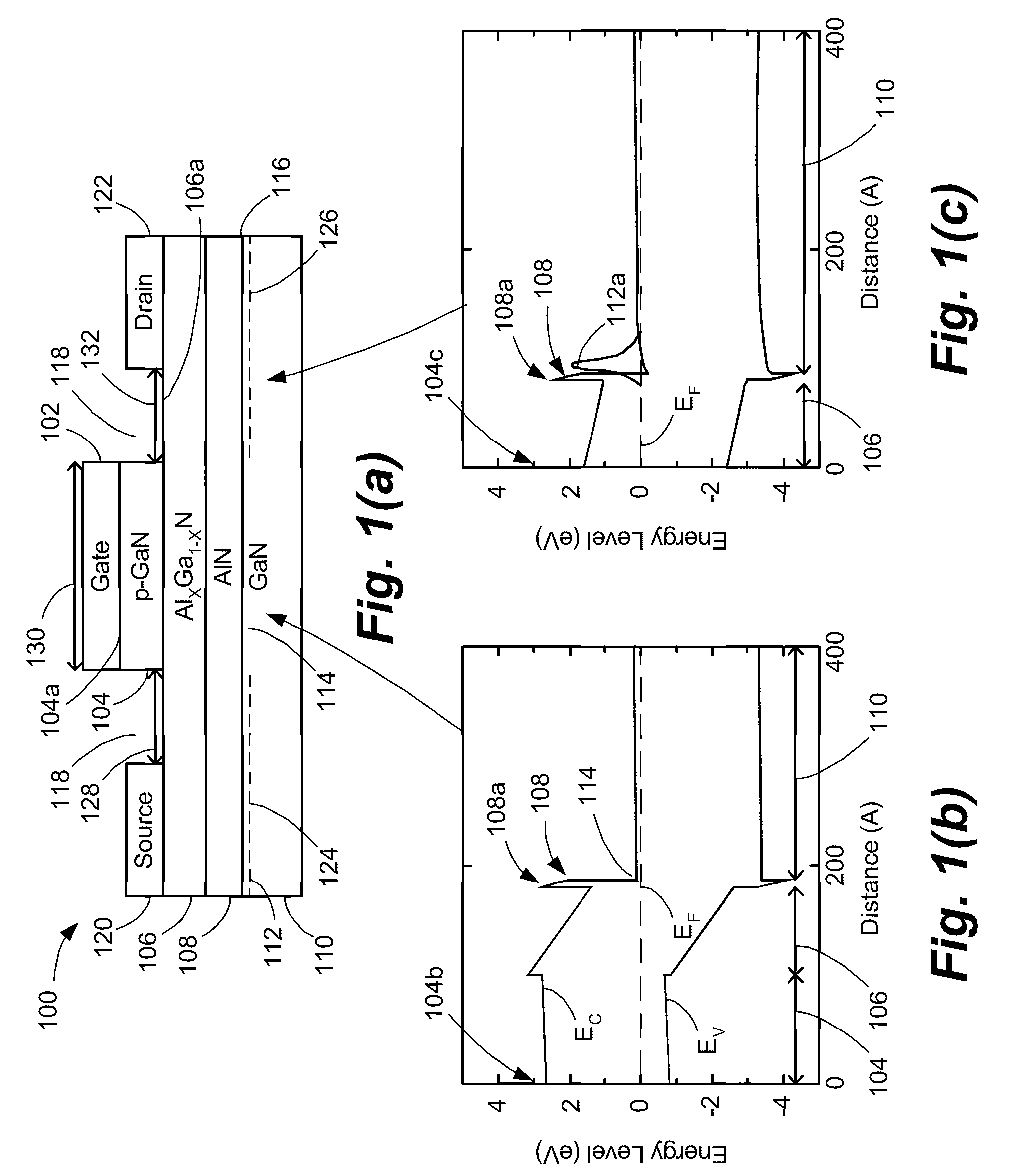

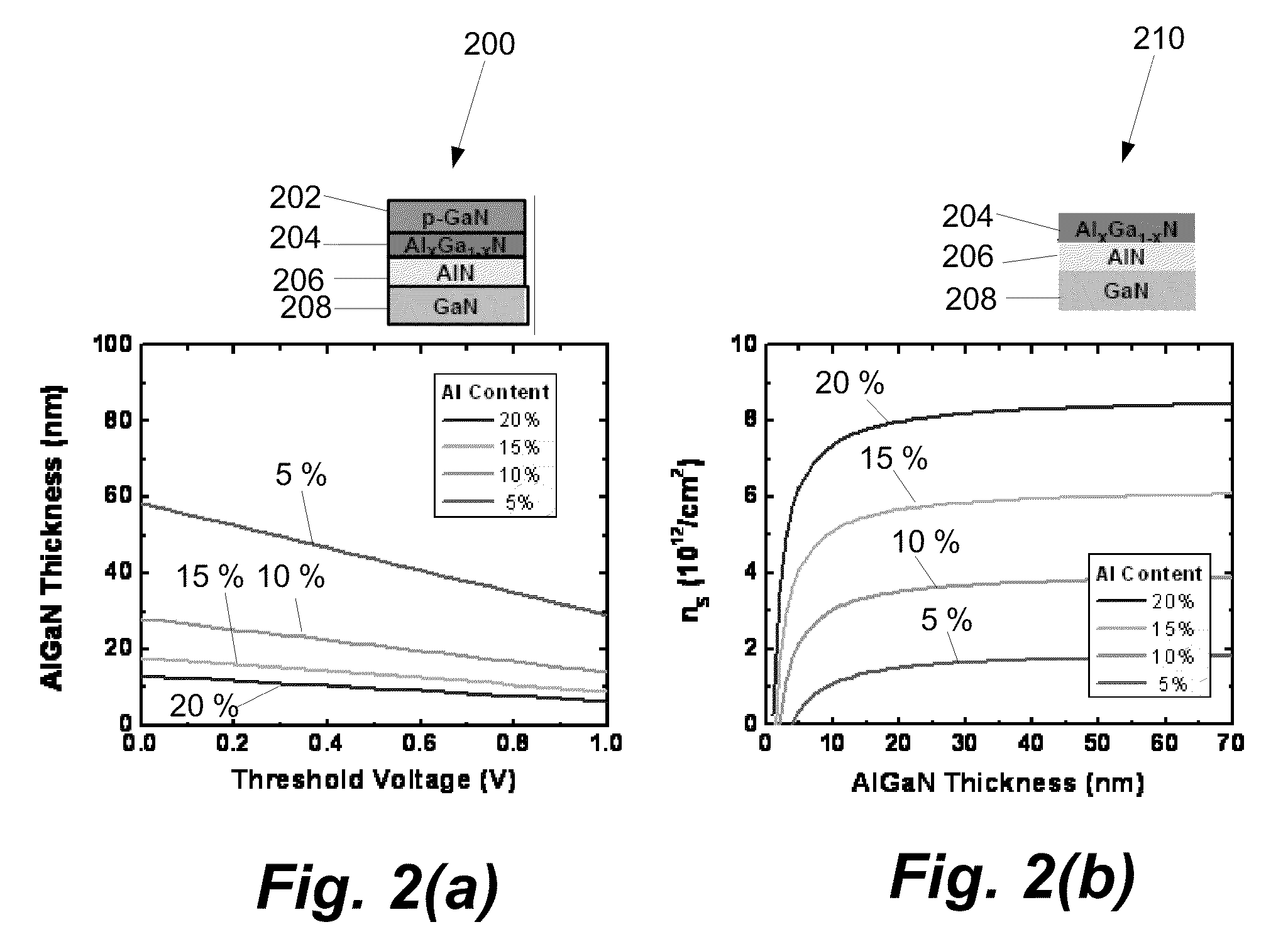

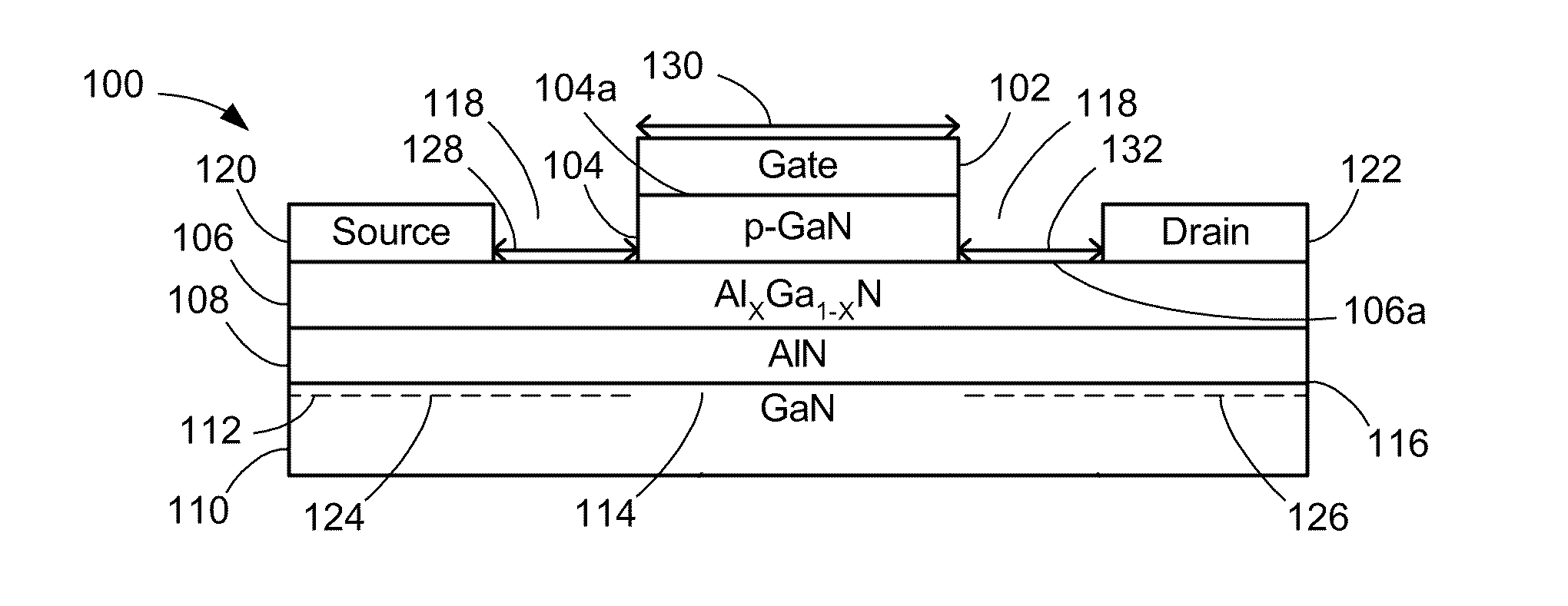

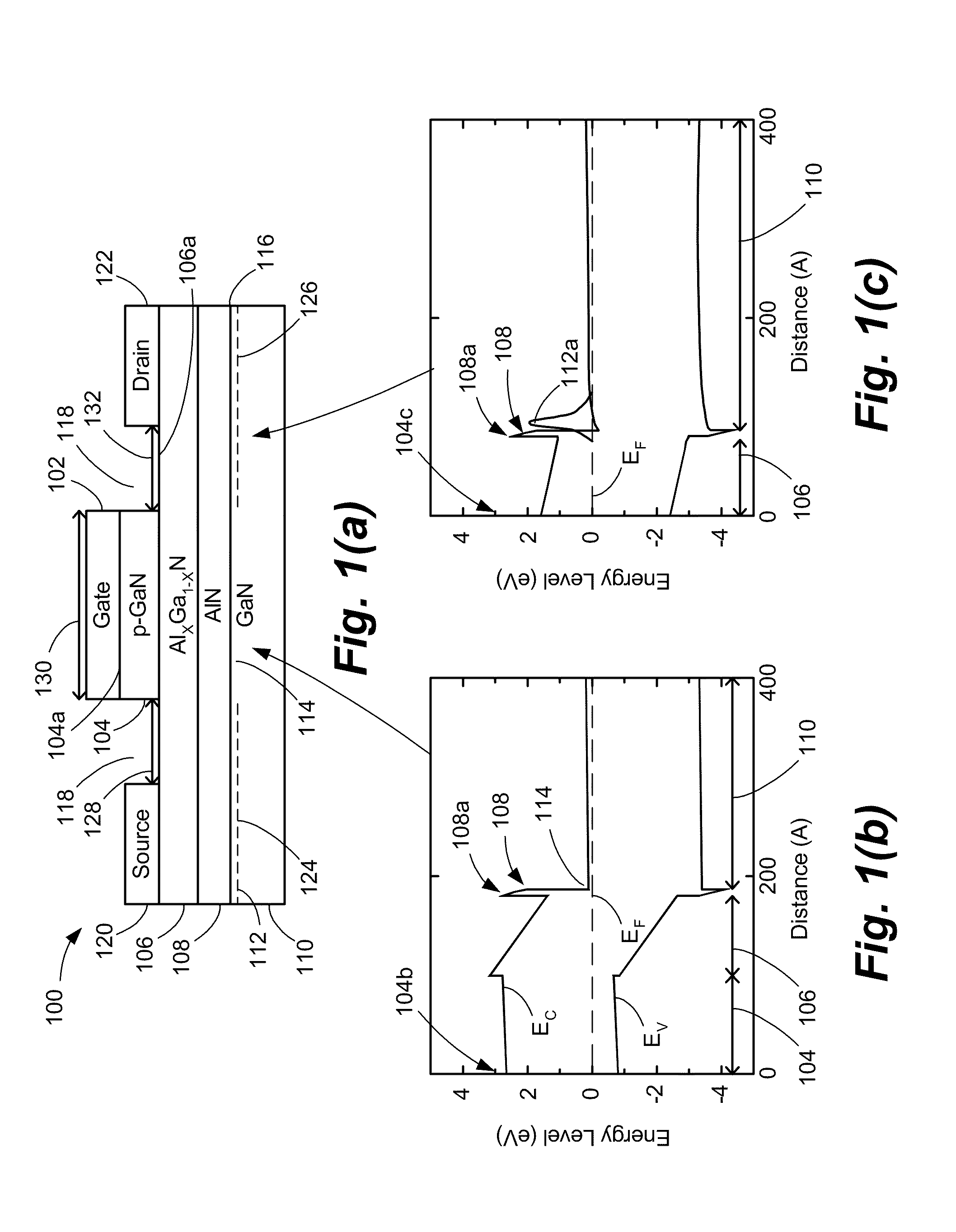

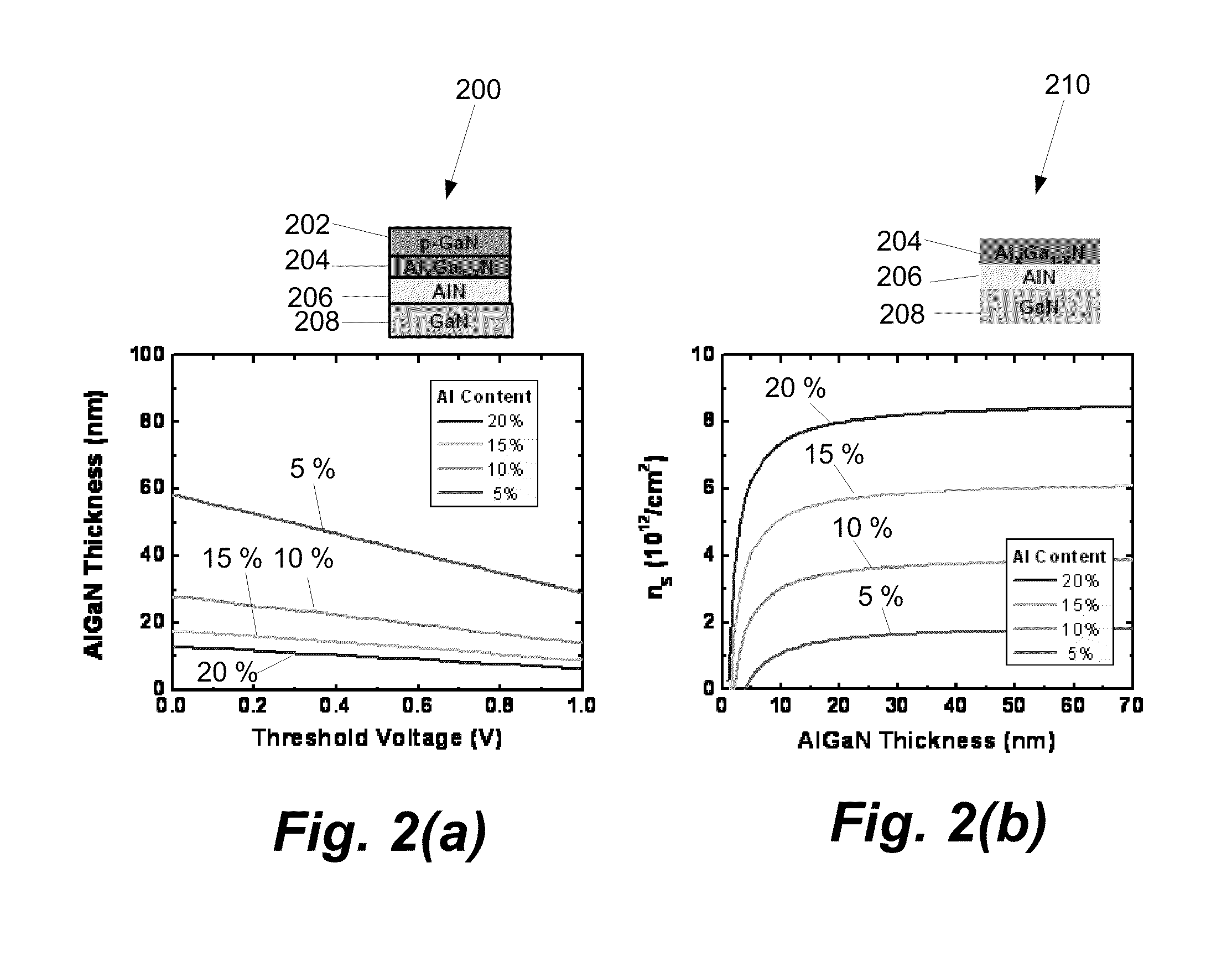

P-GaN/AlGaN/AlN/GaN ENHANCEMENT-MODE FIELD EFFECT TRANSISTOR

ActiveUS20080296618A1Lower on-resistanceHigh electron mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesHigh-electron-mobility transistorField-effect transistor

An enhancement mode High Electron Mobility Transistor (HEMT) comprising a p-type nitride layer between the gate and a channel of the HEMT, for reducing an electron population under the gate. The HEMT may also comprise an Aluminum Nitride (AlN) layer between an AlGaN layer and buffer layer of the HEMT to reduce an on resistance of a channel.

Owner:RGT UNIV OF CALIFORNIA

P-GaN/AlGaN/AlN/GaN enhancement-mode field effect transistor

ActiveUS7728356B2High electron mobilityLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectron populationField-effect transistor

Owner:RGT UNIV OF CALIFORNIA

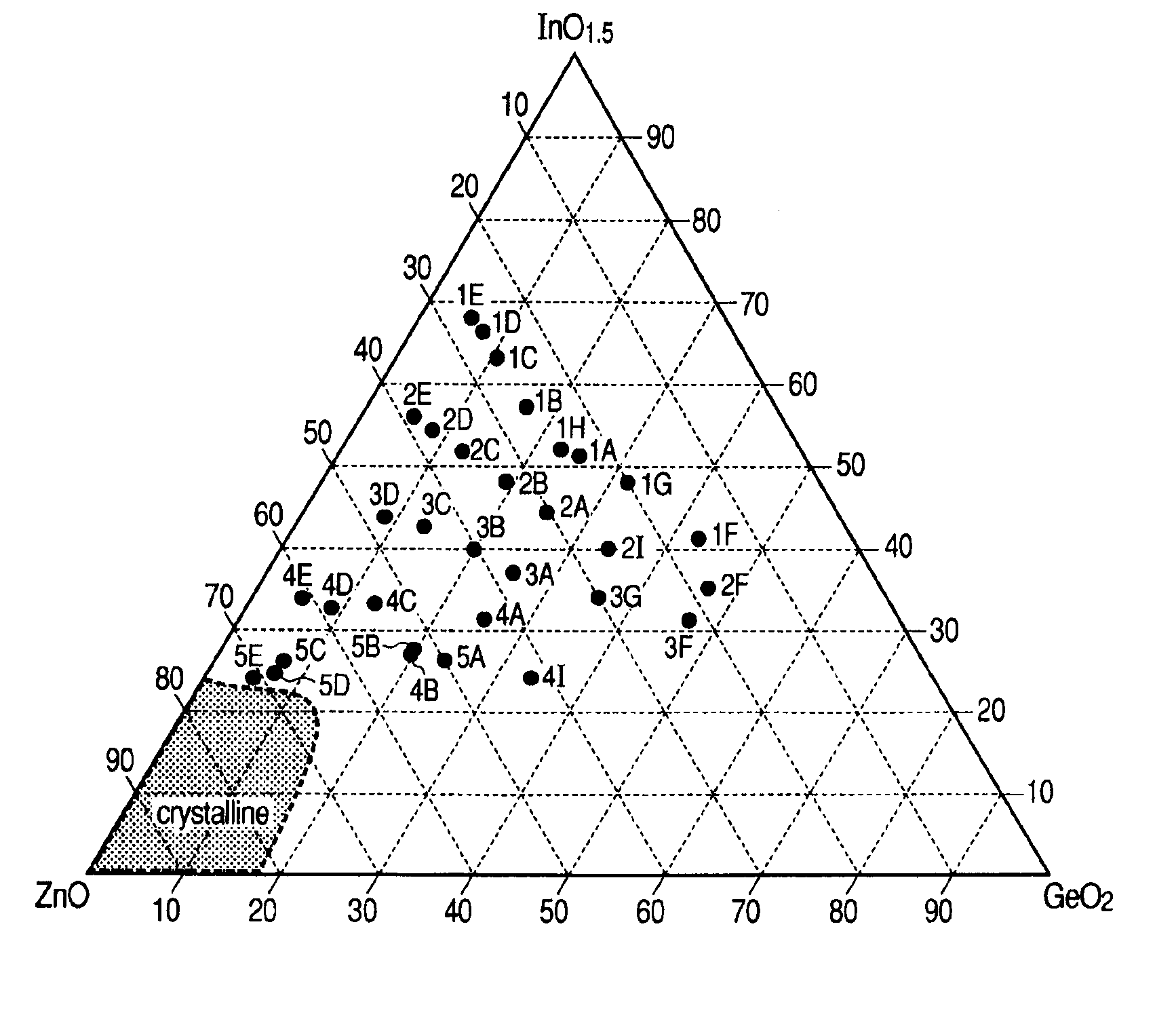

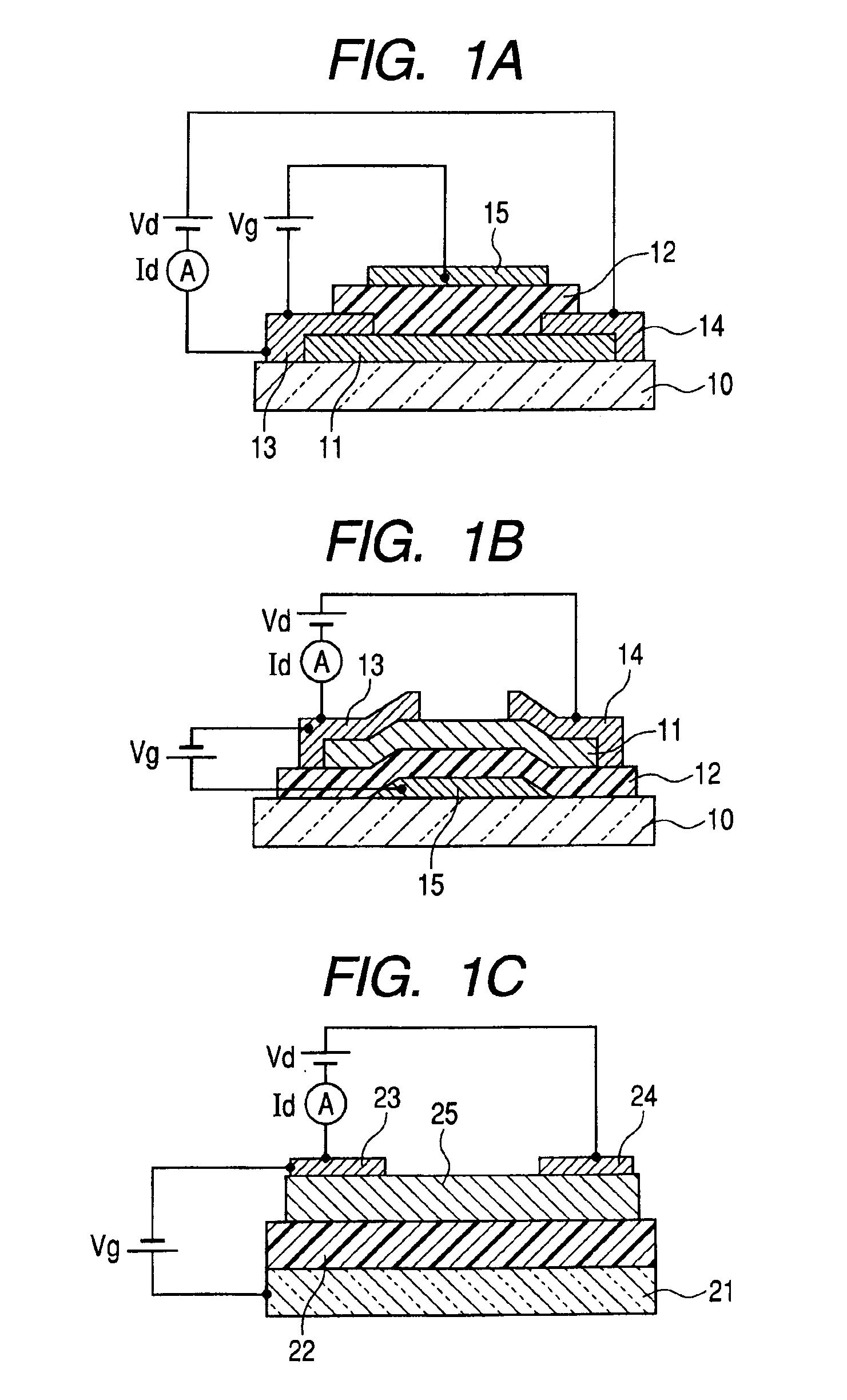

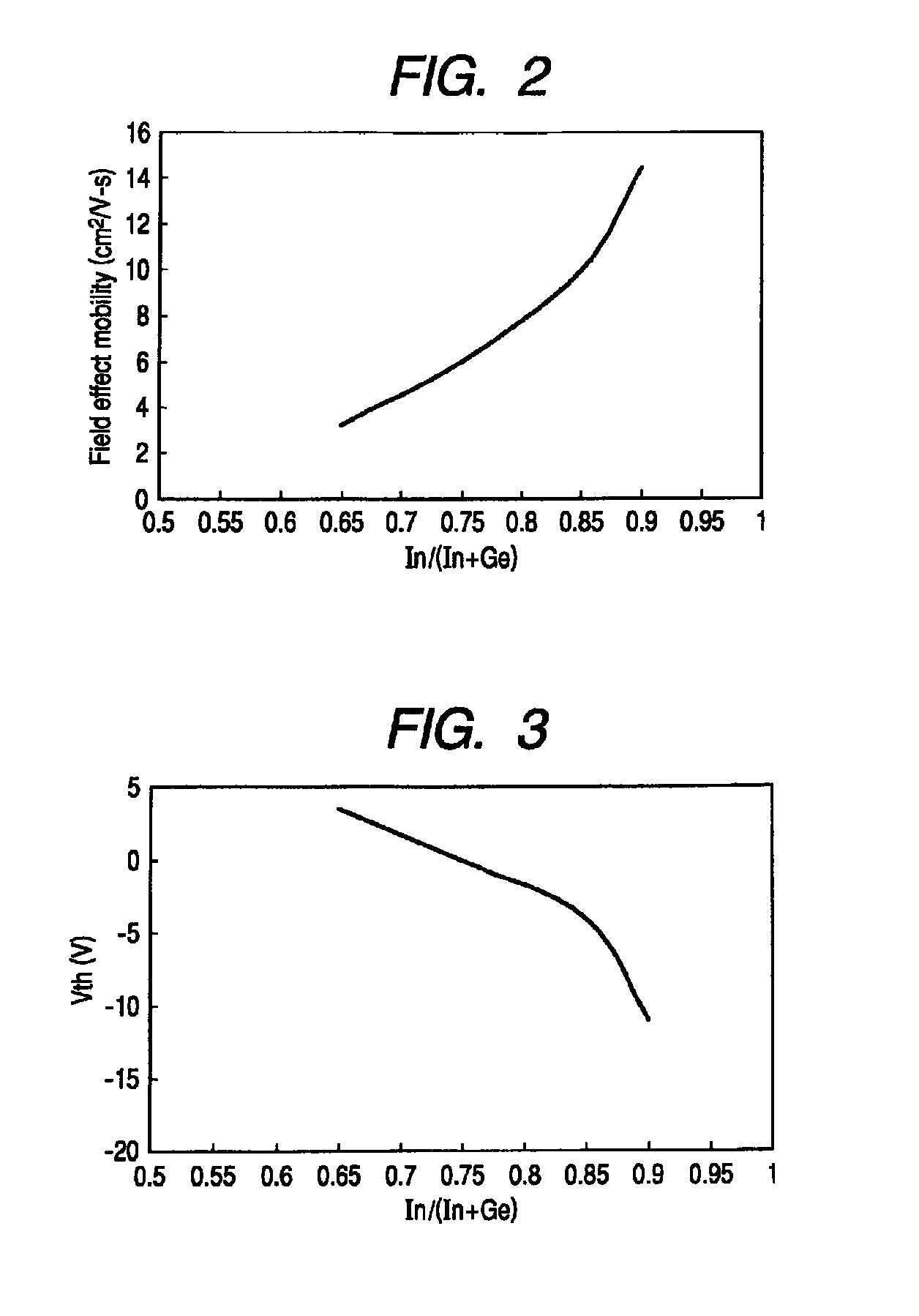

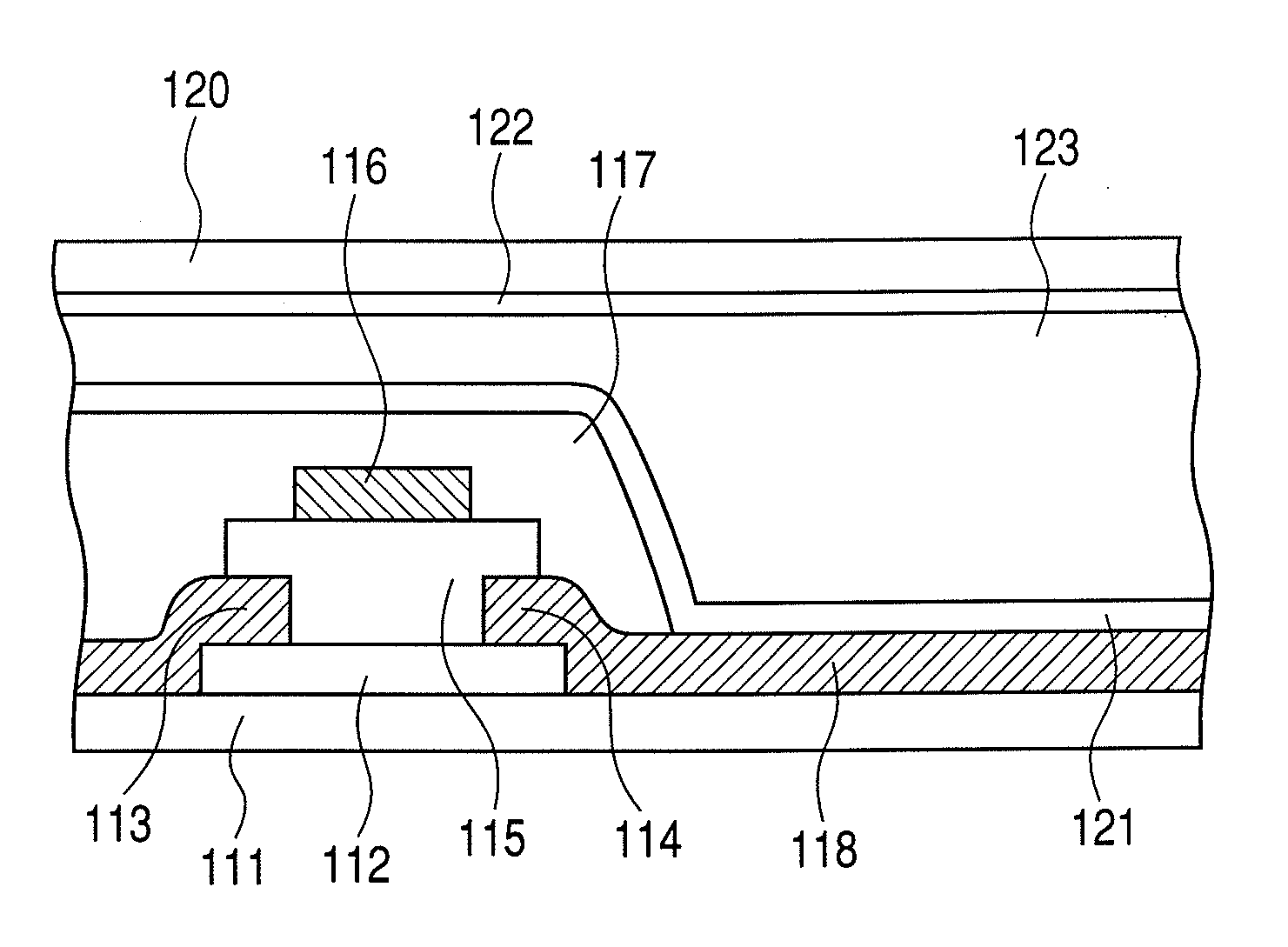

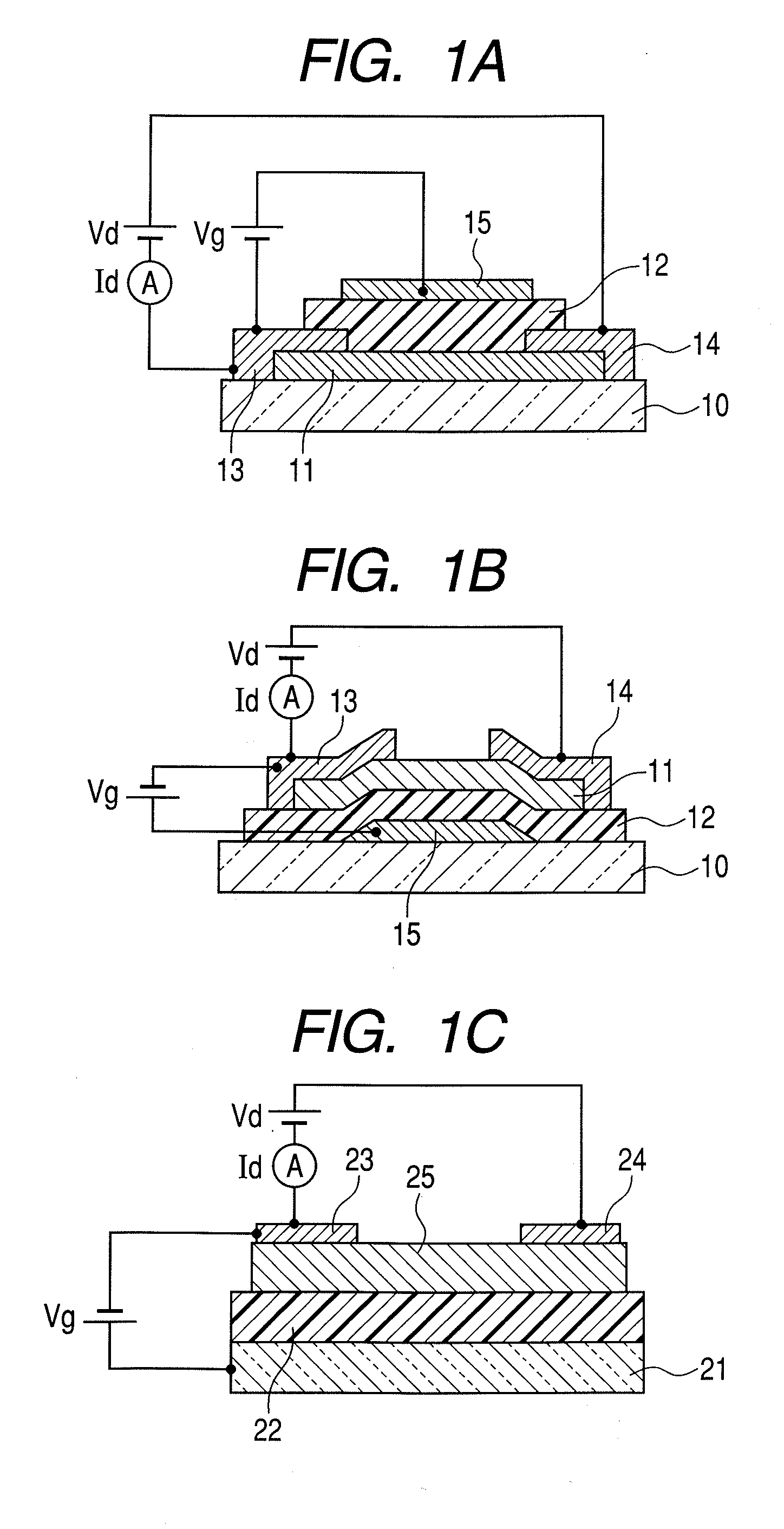

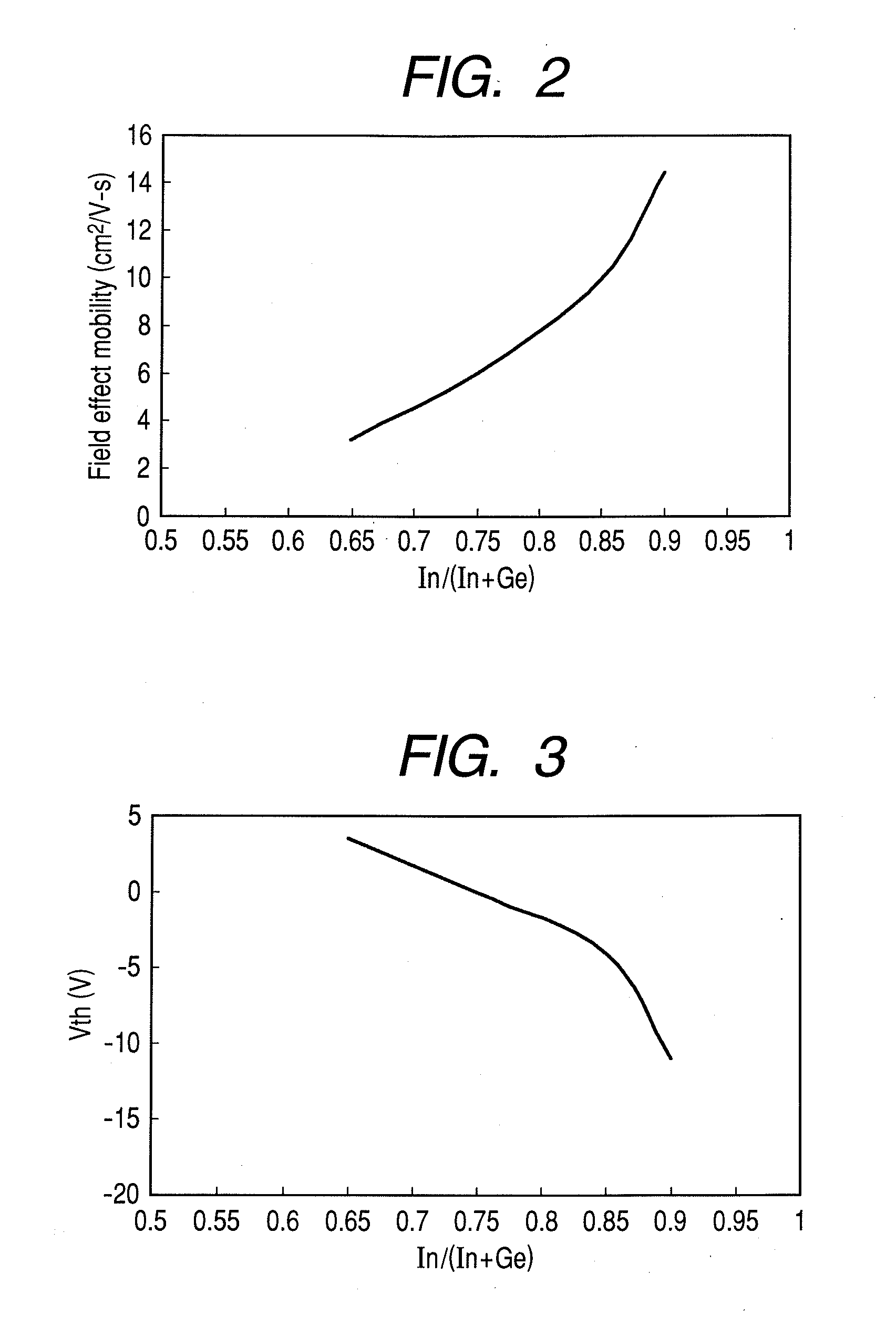

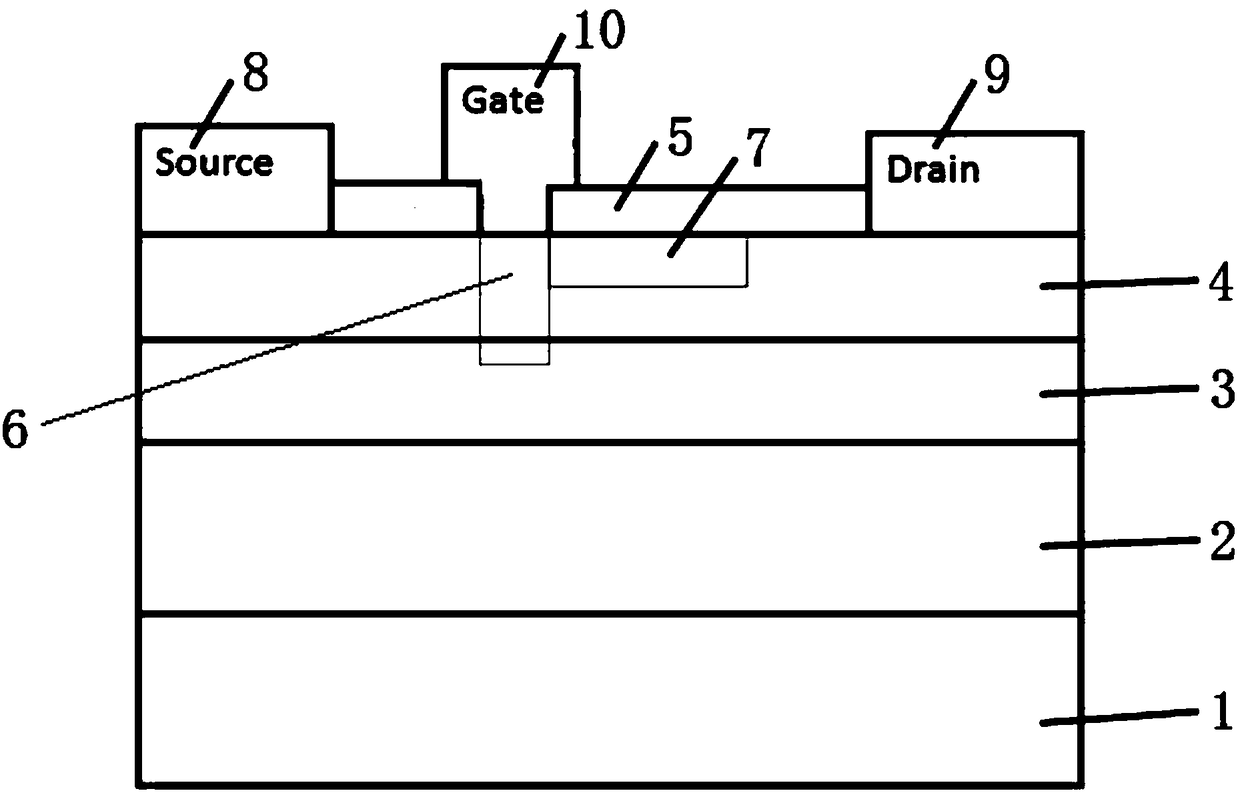

Thin film transistor using an oxide semiconductor and display

ActiveUS8742412B2TFT characteristics can be controlledImprove performanceTransistorVacuum evaporation coatingIndiumInsulation layer

A thin film transistor includes a gate electrode, a gate insulation layer, a channel layer, a source electrode, and a drain electrode formed on a substrate, in which: the channel layer contains indium, germanium, and oxygen; and the channel layer has a compositional ratio expressed by In / (In+Ge) of 0.5 or more and 0.97 or less.

Owner:CANON KK

Thin film transistor and display

ActiveUS20110175081A1Improve featuresTFT characteristics can be controlledTransistorVacuum evaporation coatingInsulation layerIndium

A thin film transistor includes a gate electrode, a gate insulation layer, a channel layer, a source electrode, and a drain electrode formed on a substrate, in which: the channel layer contains indium, germanium, and oxygen; and the channel layer has a compositional ratio expressed by In / (In+Ge) of 0.5 or more and 0.97 or less.

Owner:CANON KK

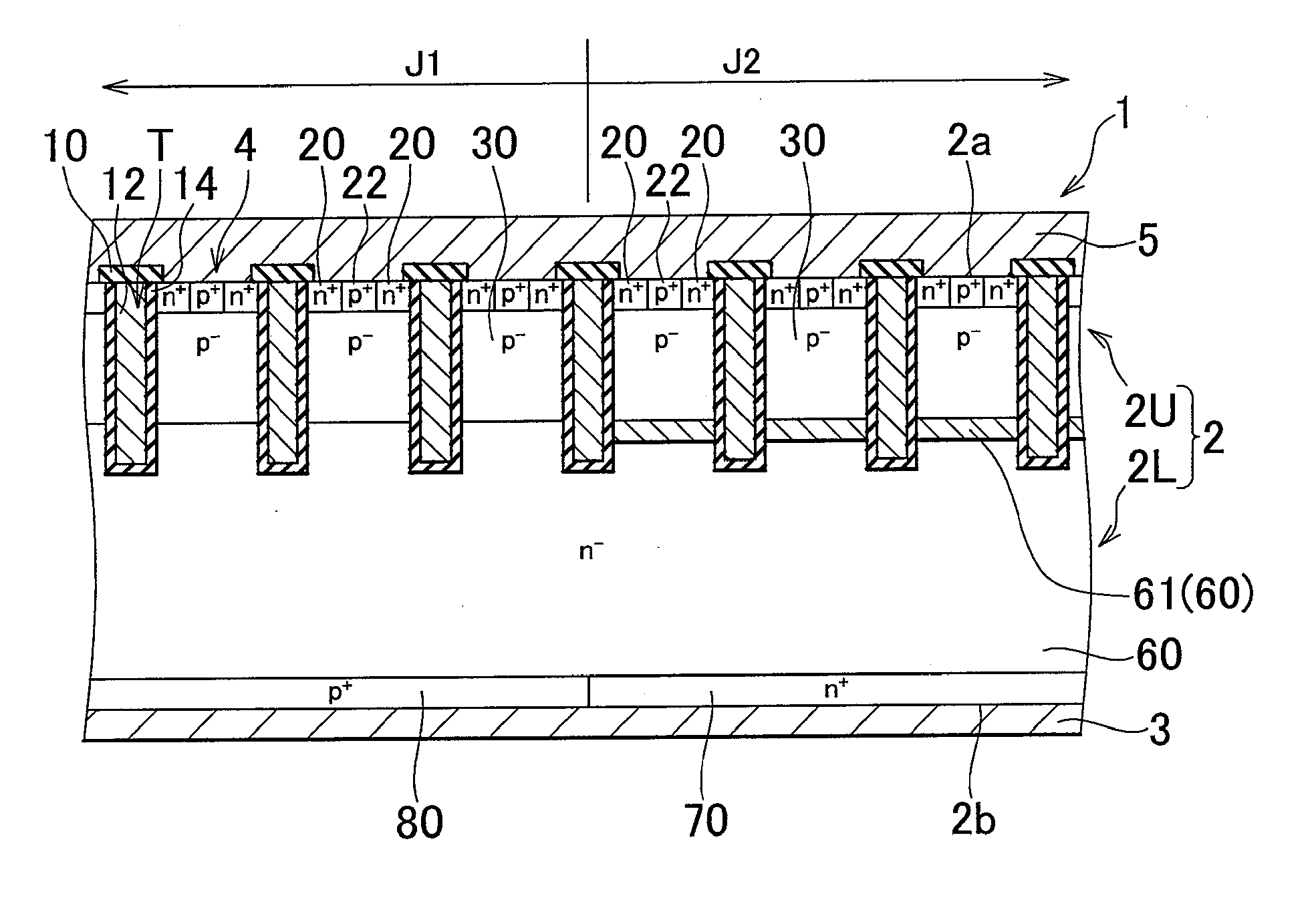

Semiconductor device

InactiveUS20090278166A1Reduce recovery lossReduced life-timeTransistorSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A semiconductor device in which both an IGBT element region and a diode element region exist in the same semiconductor substrate includes a low lifetime region, which is formed in at least a part of a drift layer within the diode element region and shortens the lifetime of holes. A mean value of the lifetime of holes in the drift layer that includes the low lifetime region is shorter within the IGBT element region than within the diode element region.

Owner:TOYOTA JIDOSHA KK

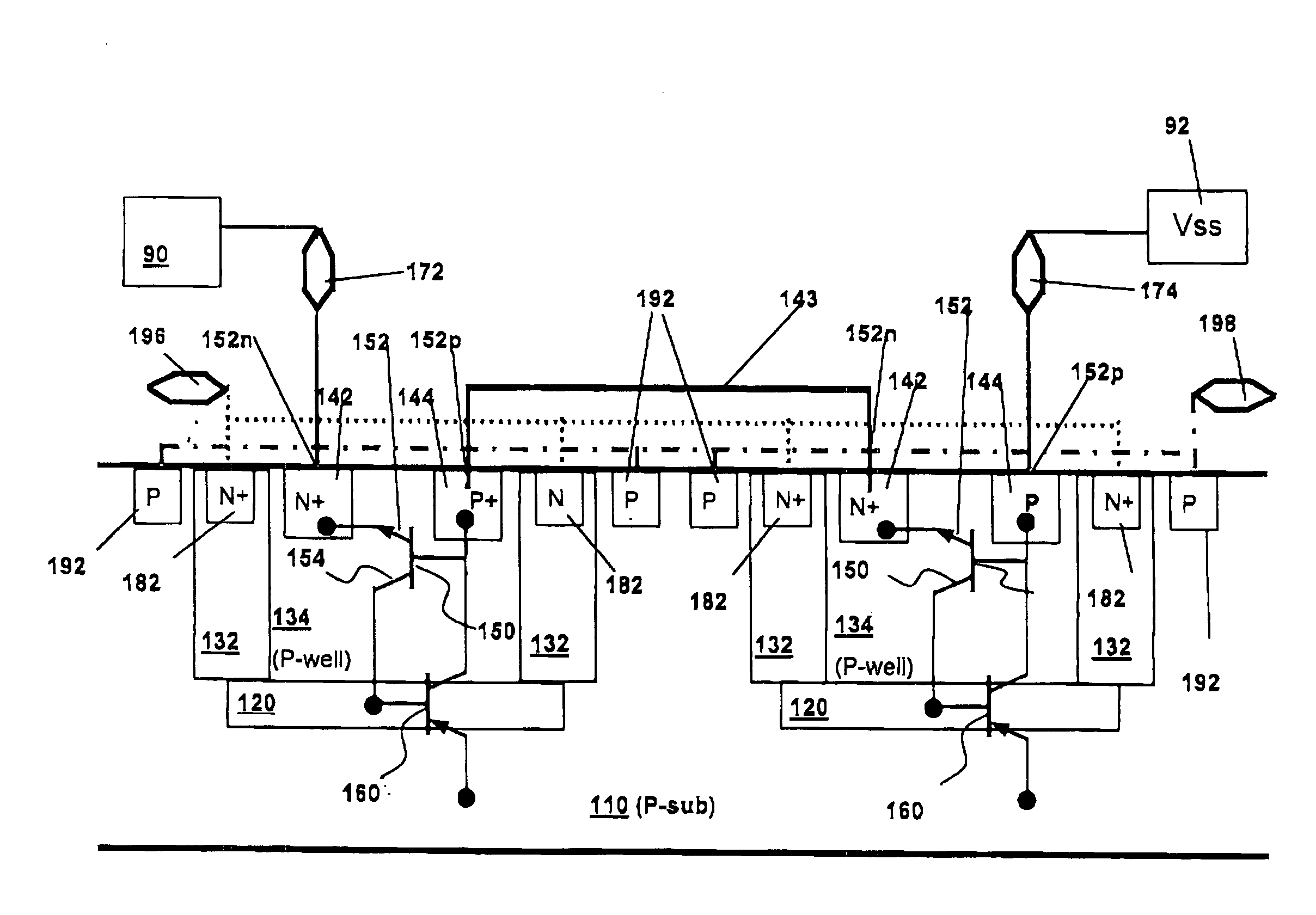

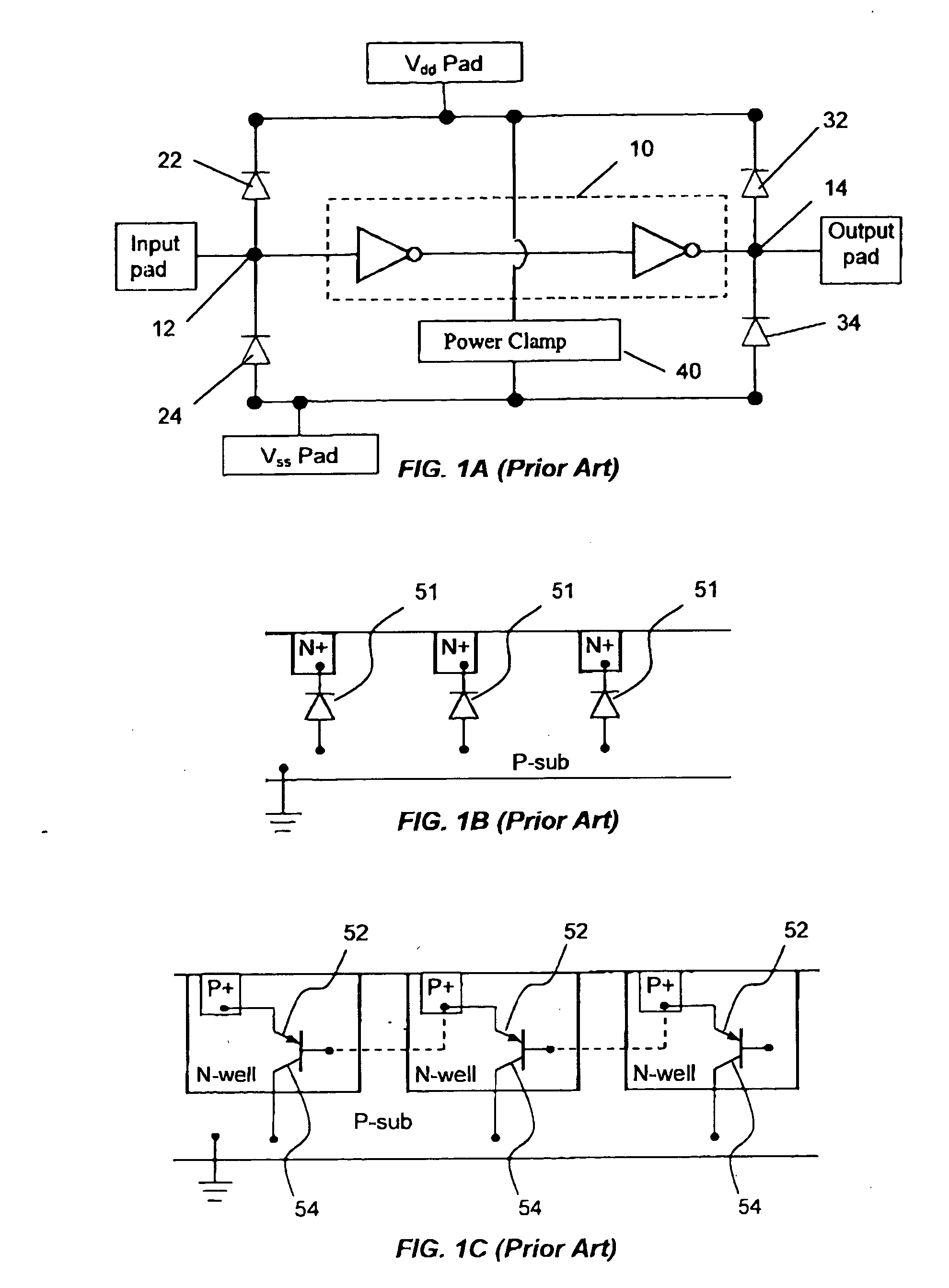

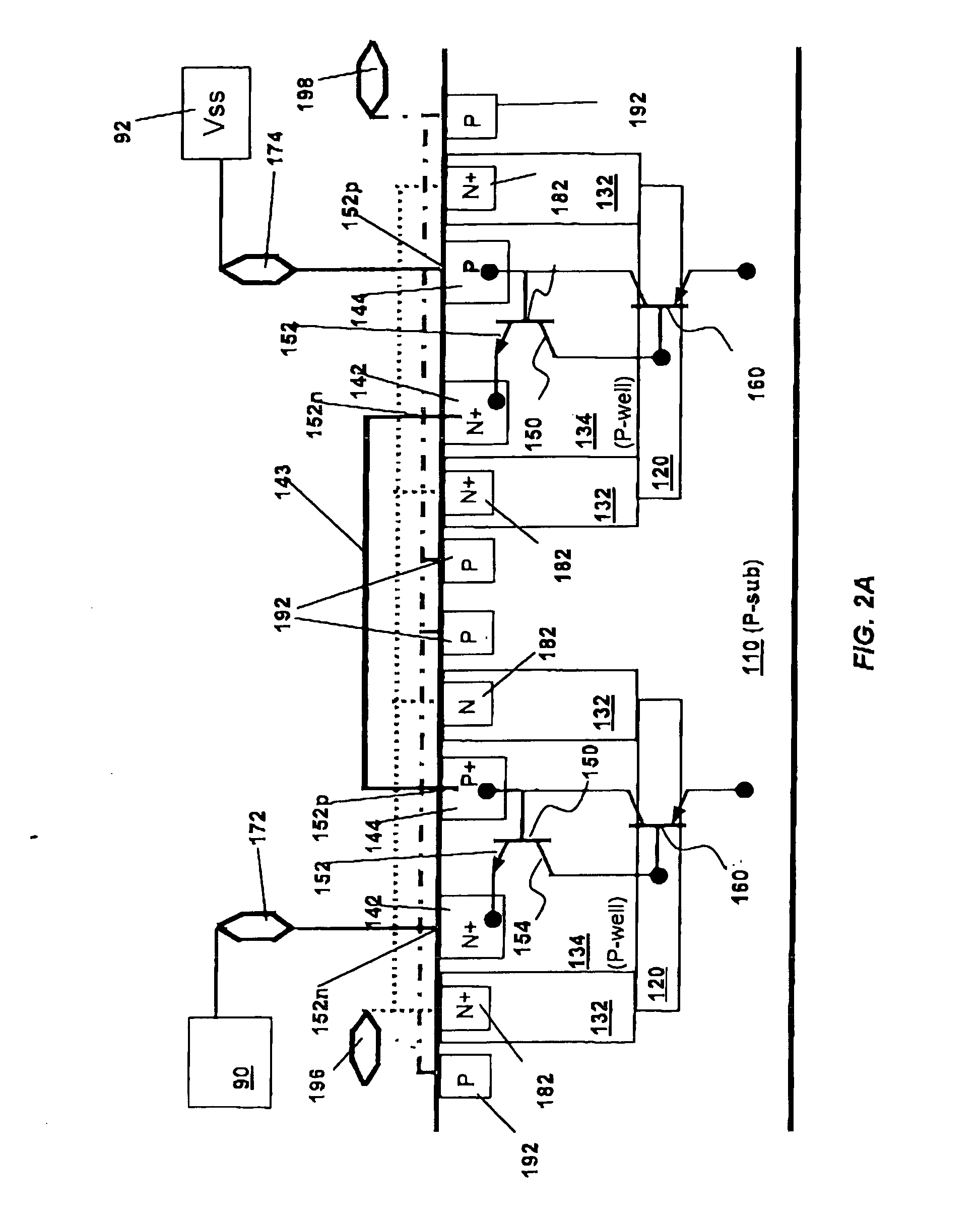

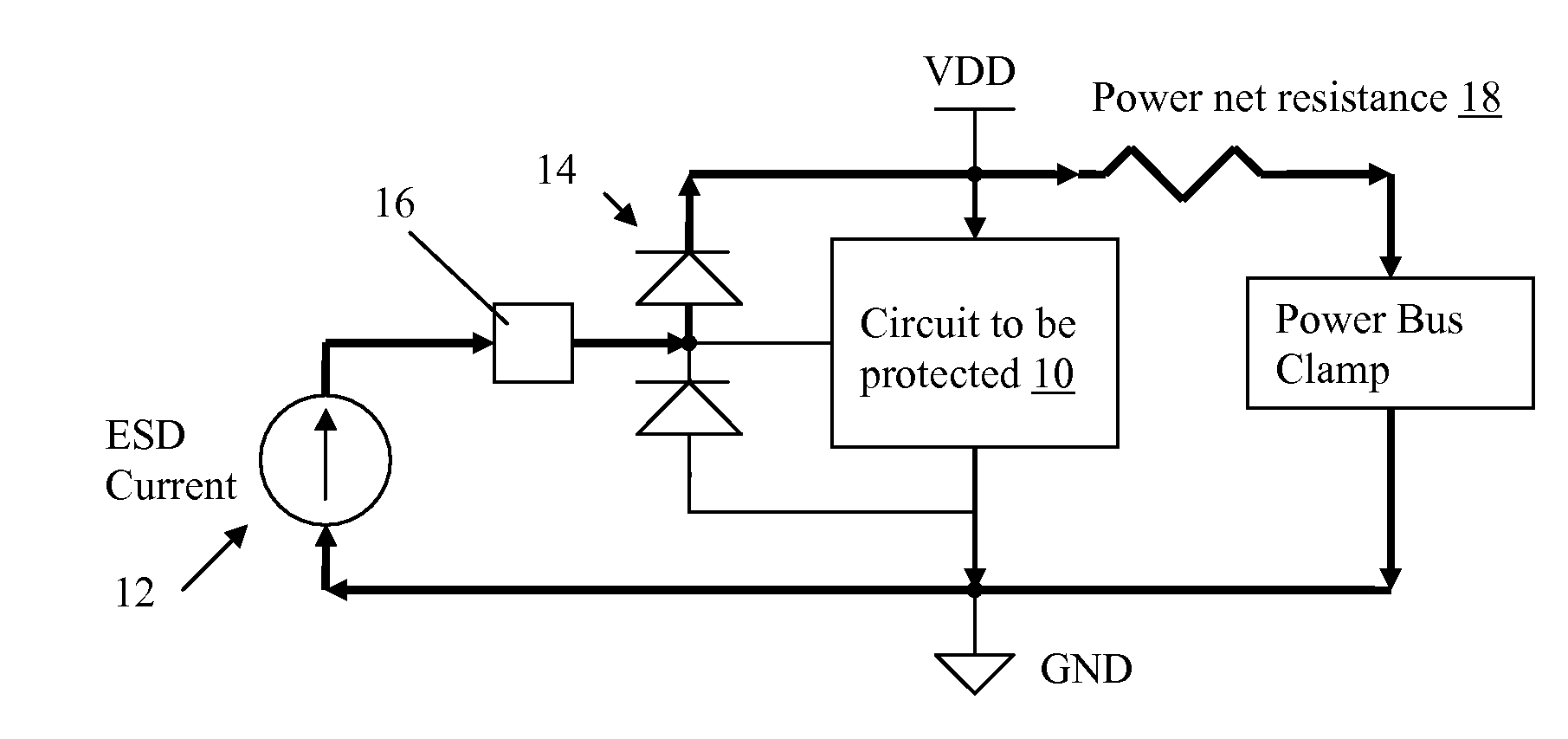

Electrostatic discharge protection for integrated circuit devices

InactiveUS20050045909A1Direct contactProblem can be overcomeTransistorThyristorElectrostatic discharge protectionIntegrated circuit

An apparatus for providing ESD protection to an integrated circuit device comprising a substrate of one type of semiconductor, a first region of a complementary type of semiconductor formed in the substrate, which surrounds a second region of said one type of semiconductor. A plurality of diodes each is formed in one of the plurality of second regions. The at least one first region is disposed between the plurality of second regions and the substrate to prevent direct contact between the second regions and the substrate. The plurality of diodes are connectable in series for coupling to the integrated circuit device for providing ESD protection.

Owner:AGENCY FOR SCI TECH & RES

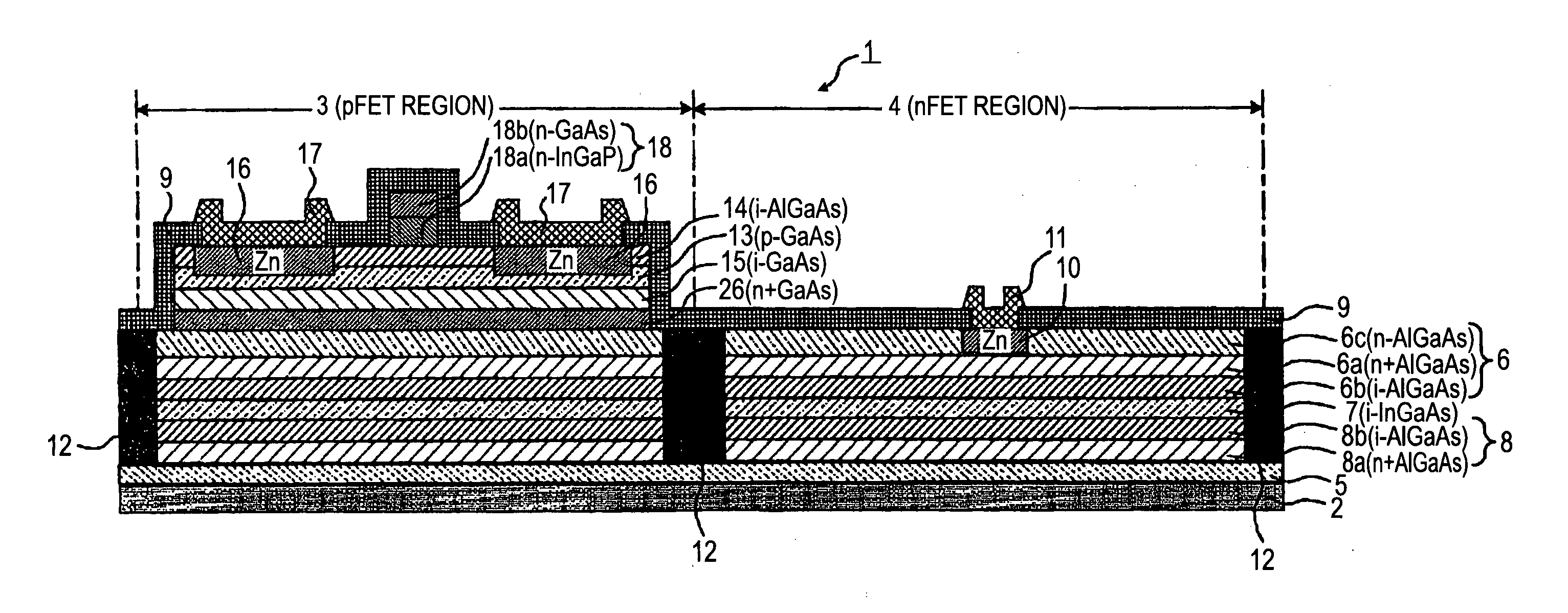

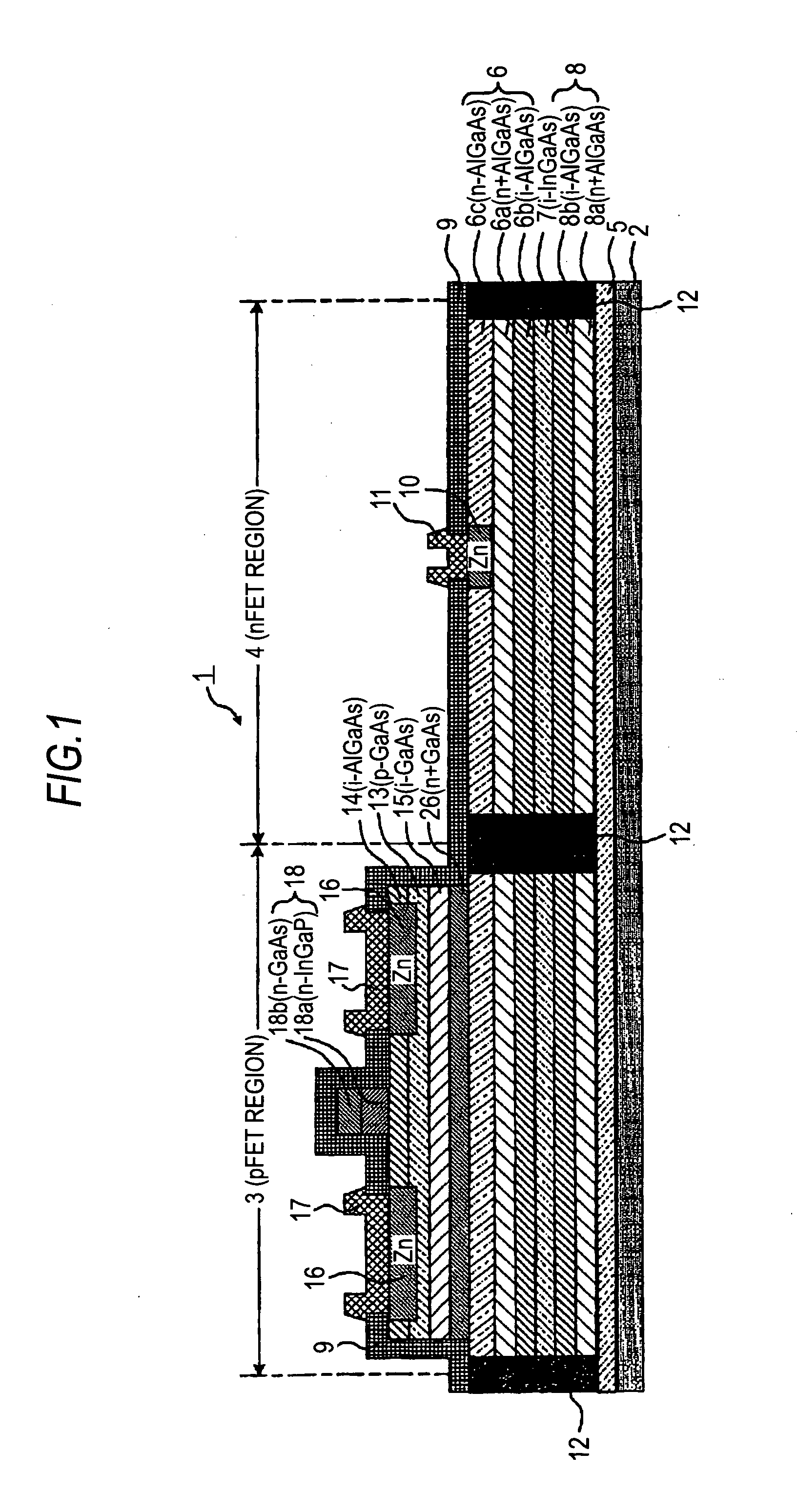

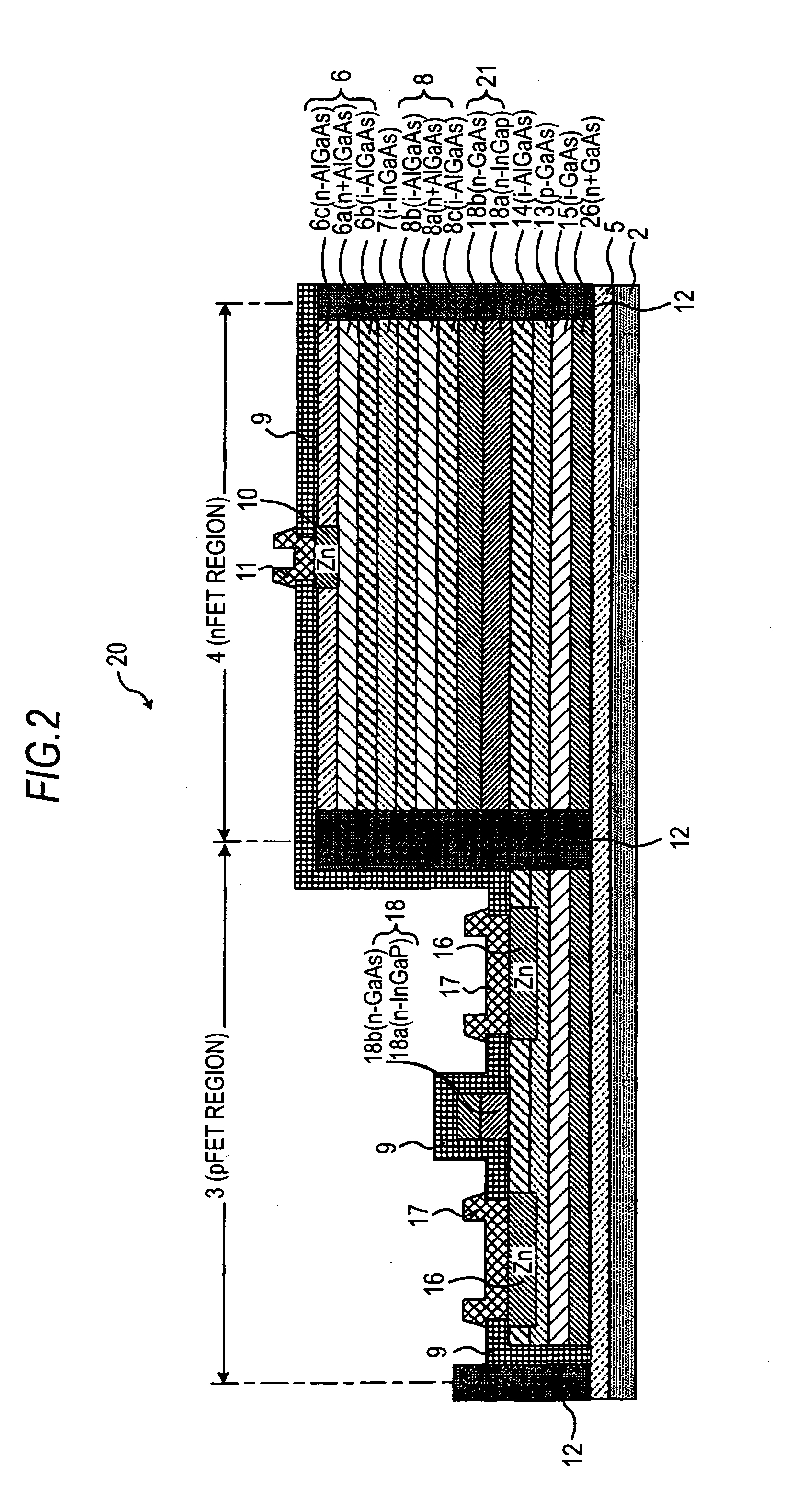

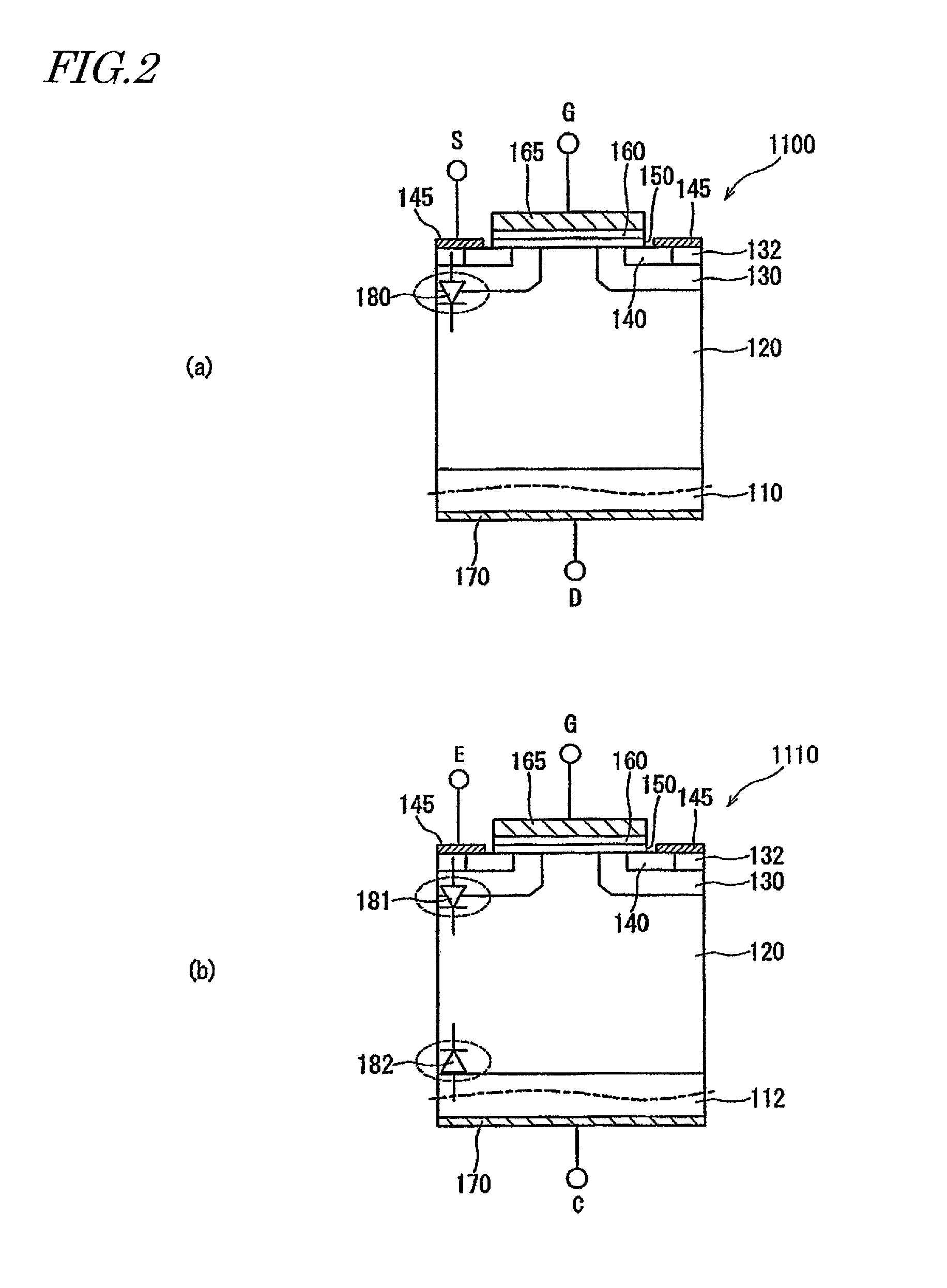

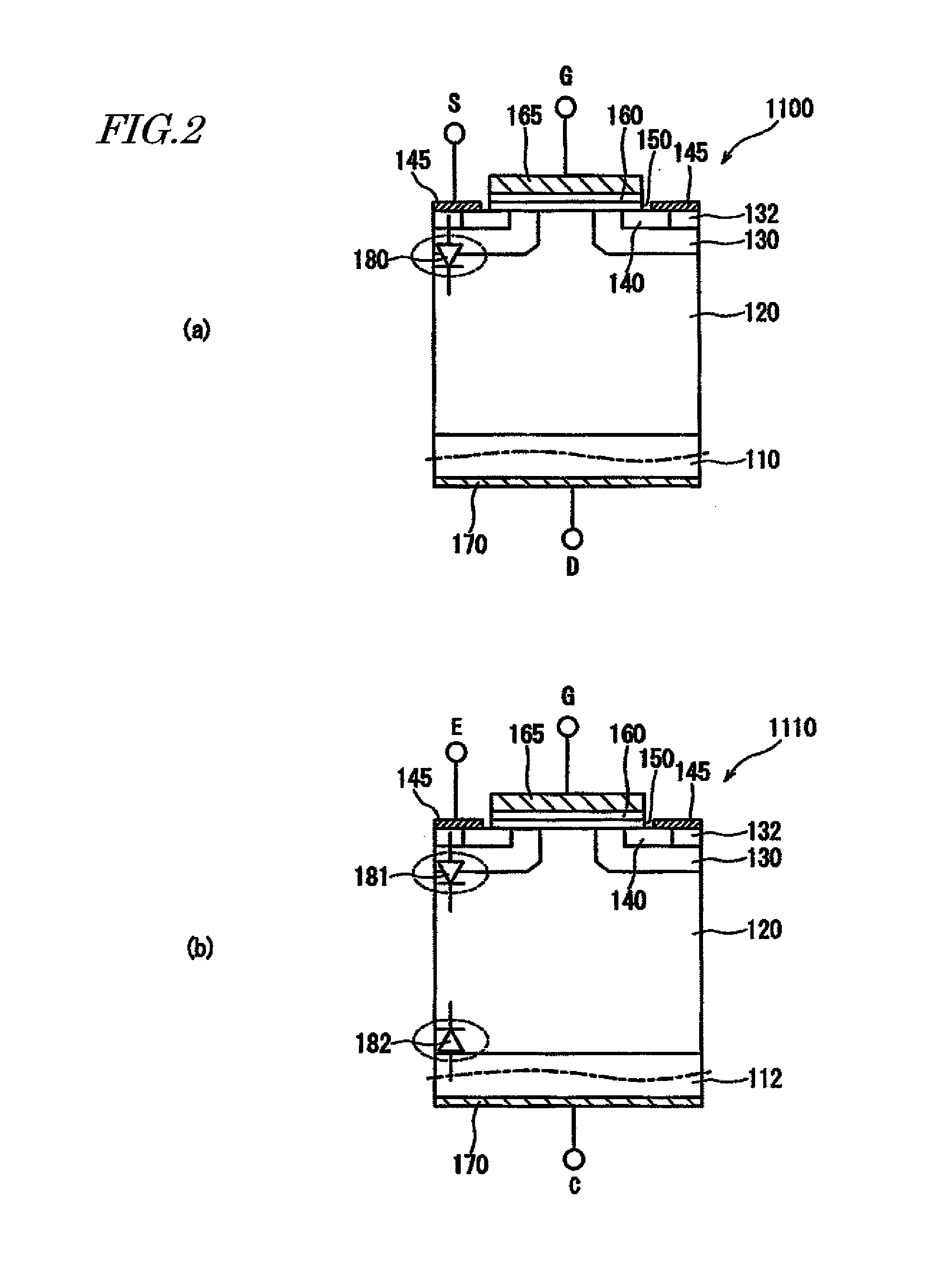

Semiconductor device and method for manufacturing same

ActiveUS20110024798A1Increase the turn-on voltageLeakage currentTransistorSolid-state devicesHeterojunctionField-effect transistor

A semiconductor device includes: a compound semiconductor substrate; an n-channel field-effect transistor region formed on the compound semiconductor substrate, and that includes a first channel layer; an n-type first barrier layer that forms a heterojunction with the first channel layer, and supplies an n-type charge to the first channel layer; and a p-type gate region that has a pn junction-type potential barrier against the n-type first barrier layer; and a p-channel field-effect transistor region formed on the compound semiconductor substrate, and that includes a p-type second channel layer, and an n-type gate region that has a pn junction-type potential barrier against the p-type second channel layer.

Owner:SONY CORP

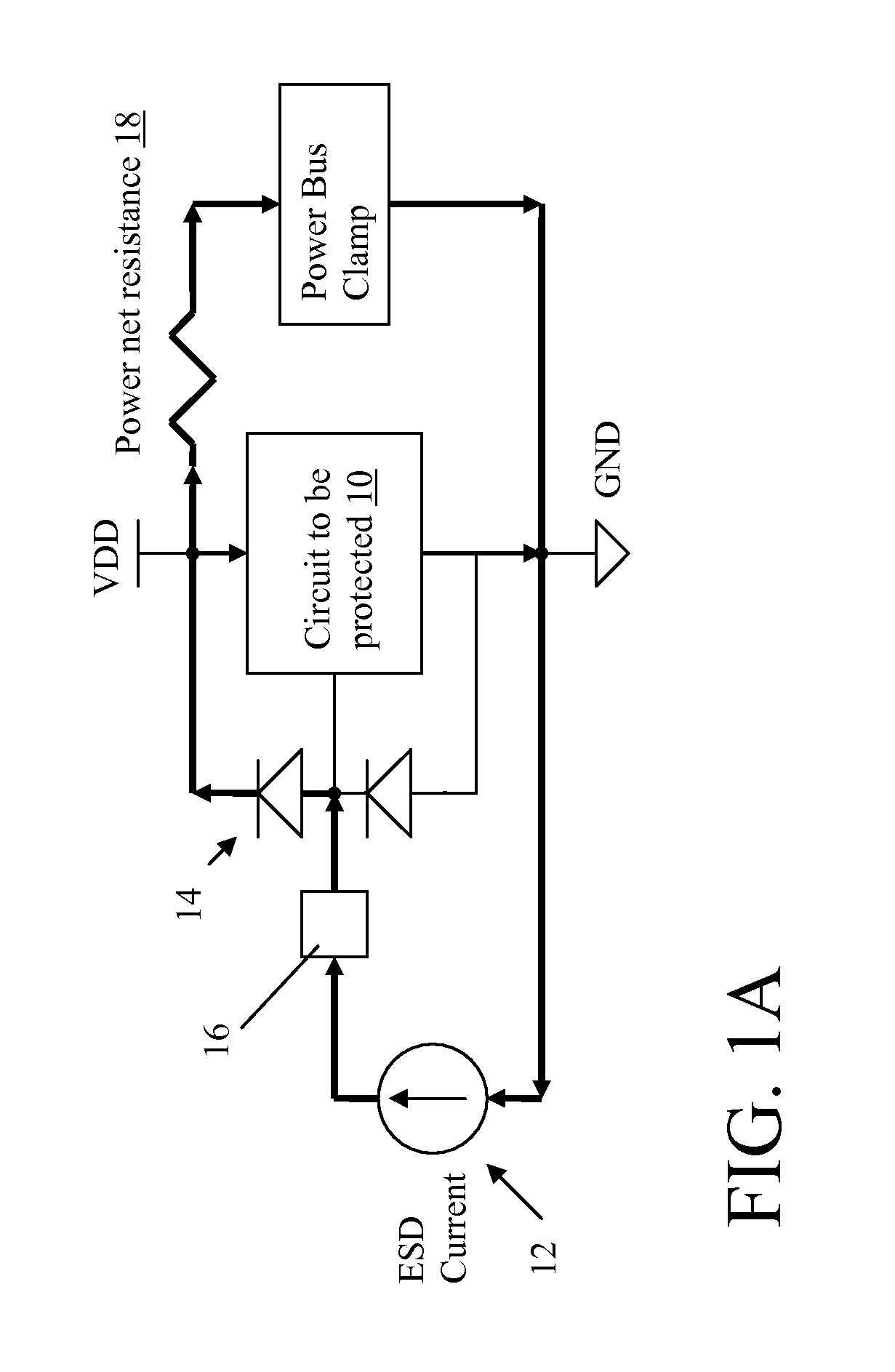

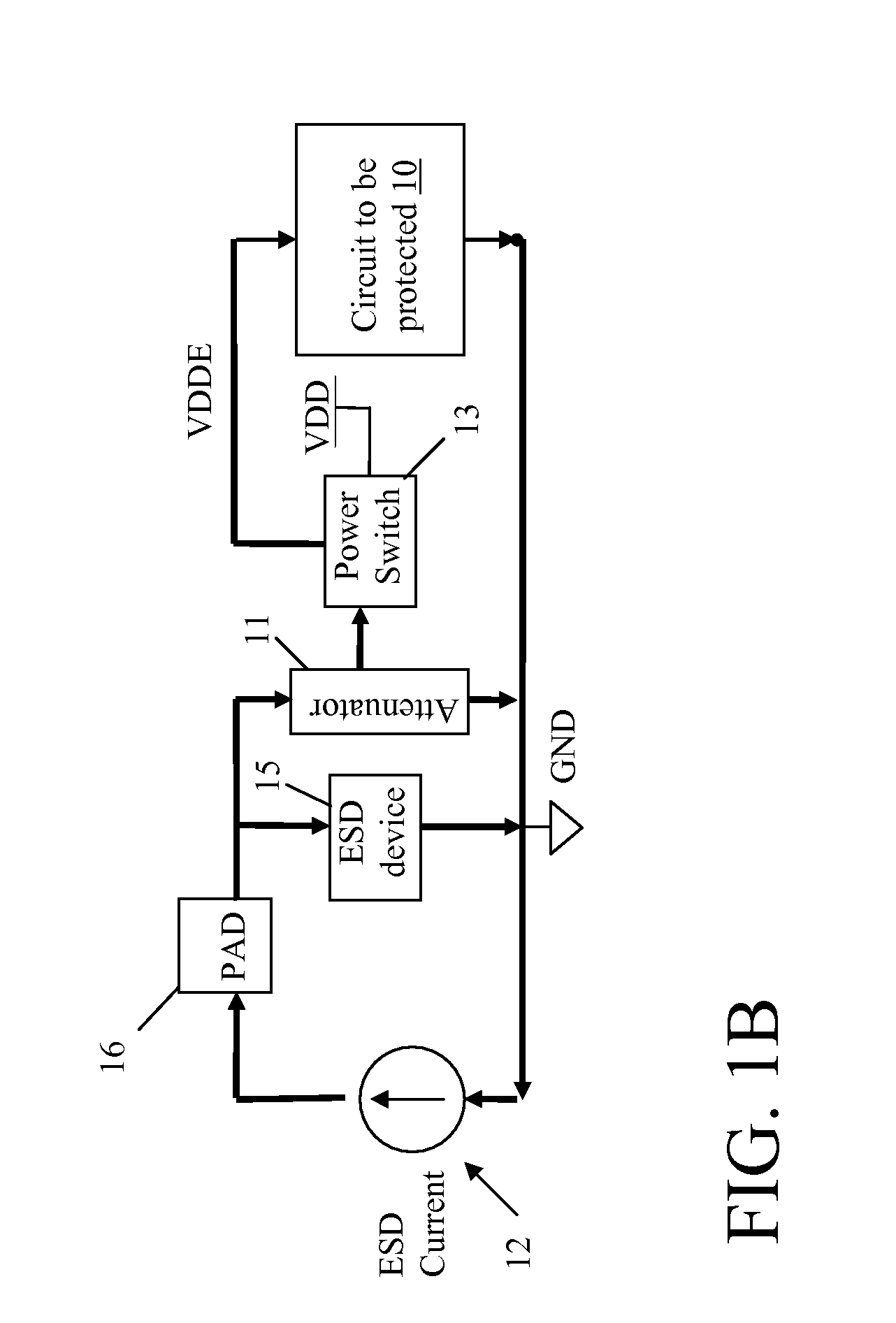

Active ESD Protection

InactiveUS20070297105A1Voltage failureReduce voltage stressSolid-state devicesEmergency protective arrangements for limiting excess voltage/currentNormal modeEngineering

A system and method of electrostatic discharge (ESD) protection in a logic circuit using either state manipulation or current injection. A first system is disclosed that includes an ESD detection circuit for detecting an ESD event; and an ESD control circuit that can change a state of the logic circuit from a normal mode to an ESD mode in response to a signal received from the ESD detection circuit. A second system is disclosed that includes an attenuator circuit coupled to a chip pad; and a switch for diverting current from the attenuator circuit to an internal node of the logic circuit during an ESD event to reduce a voltage at the chip pad.

Owner:IBM CORP

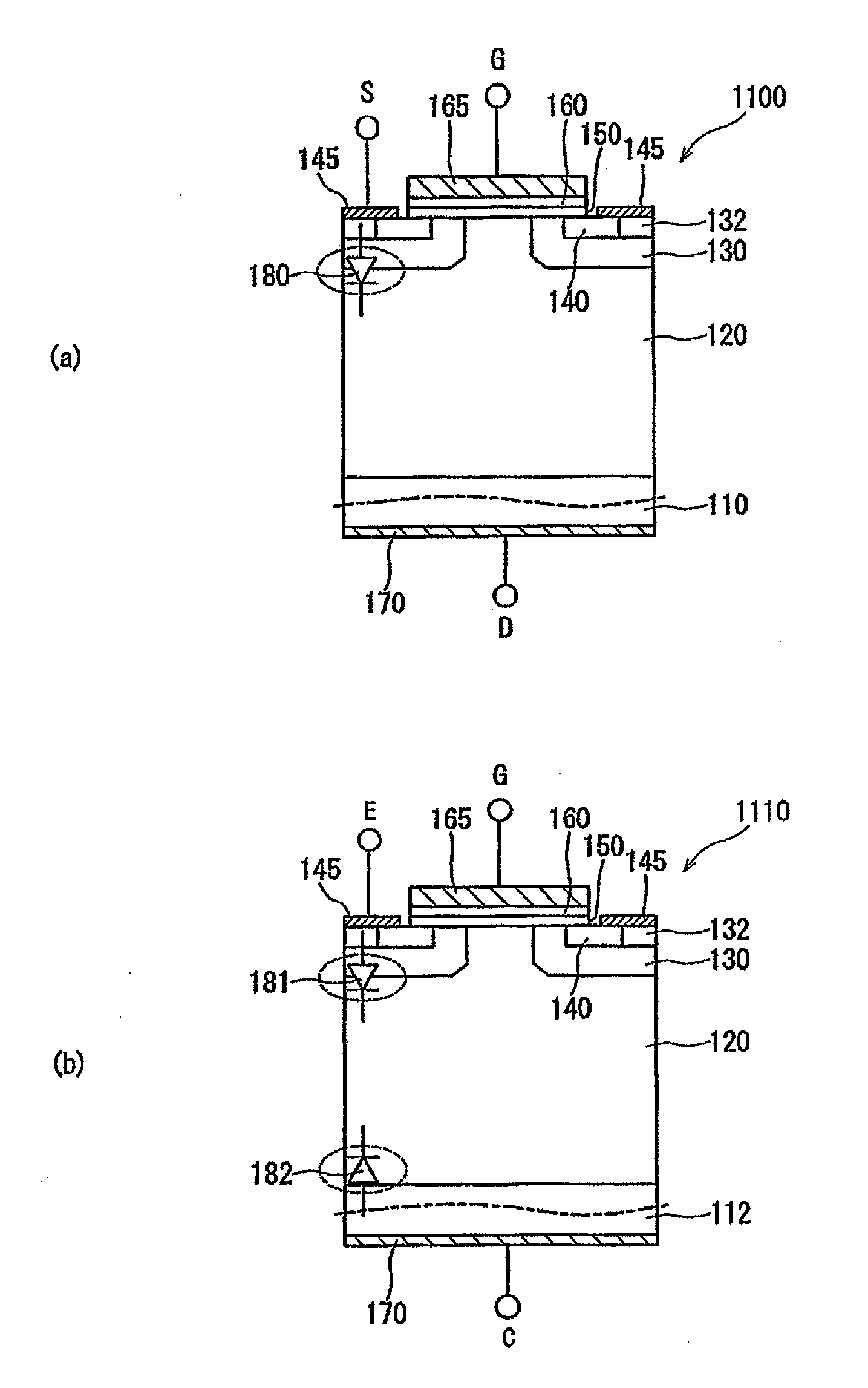

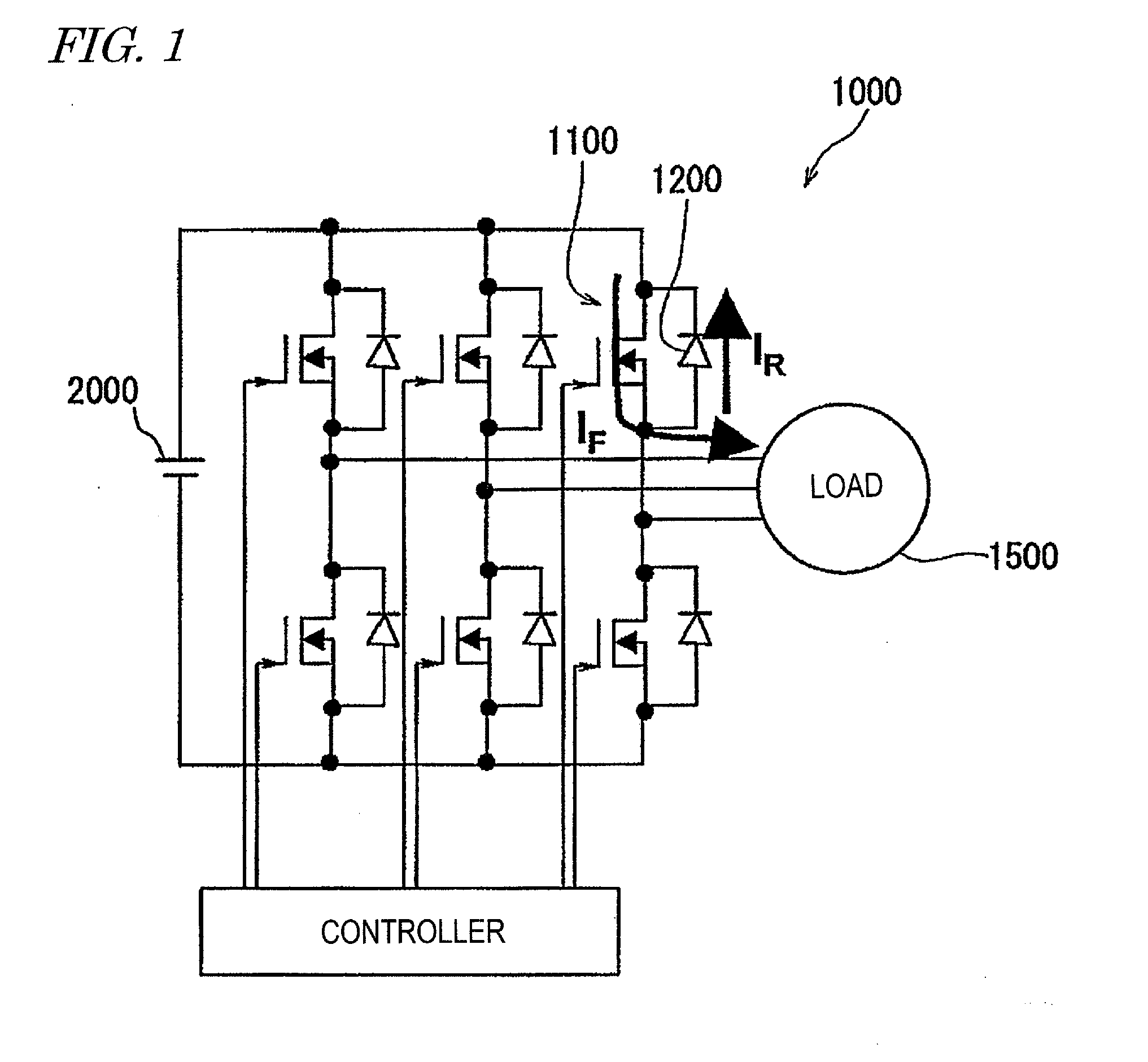

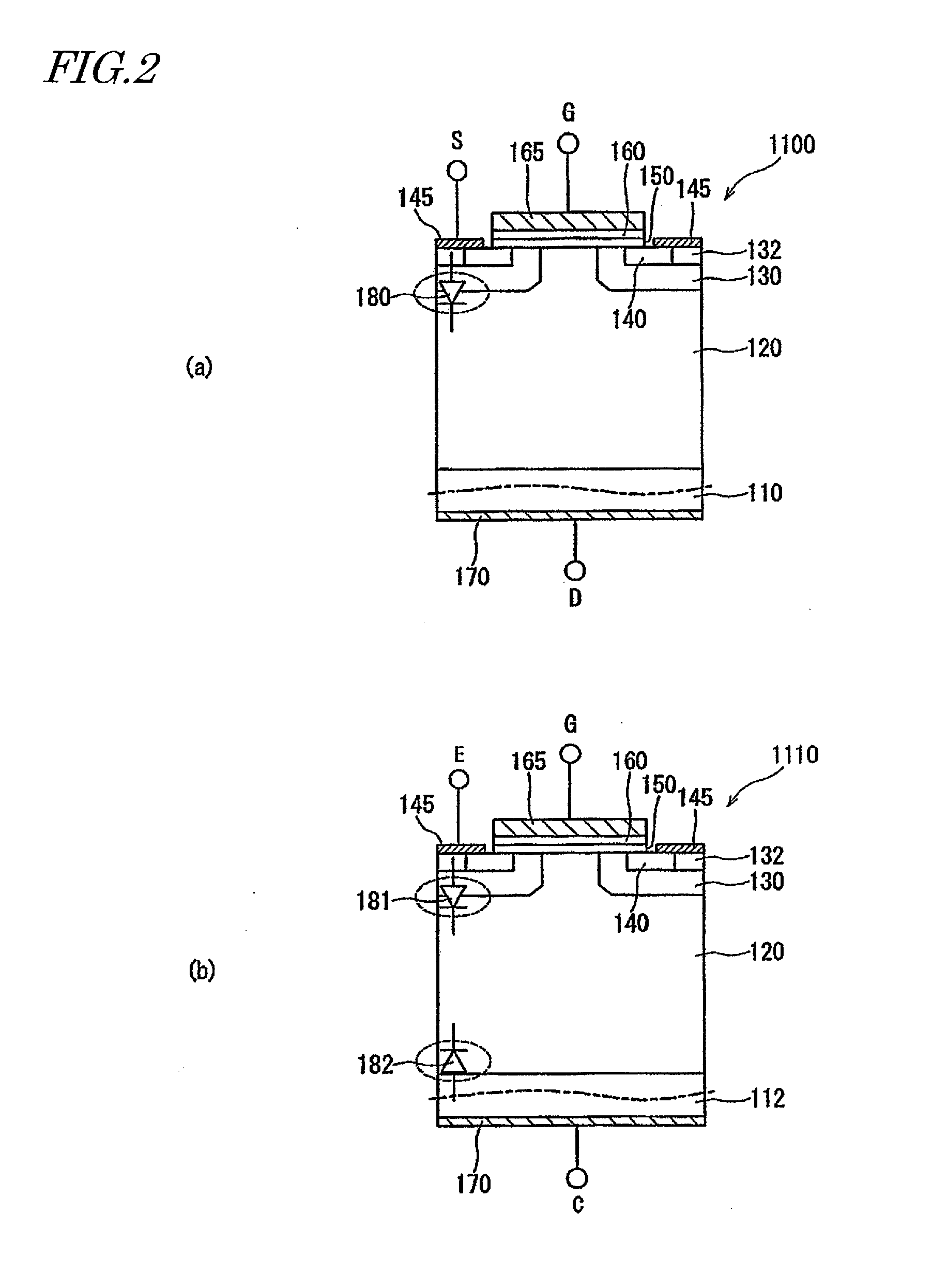

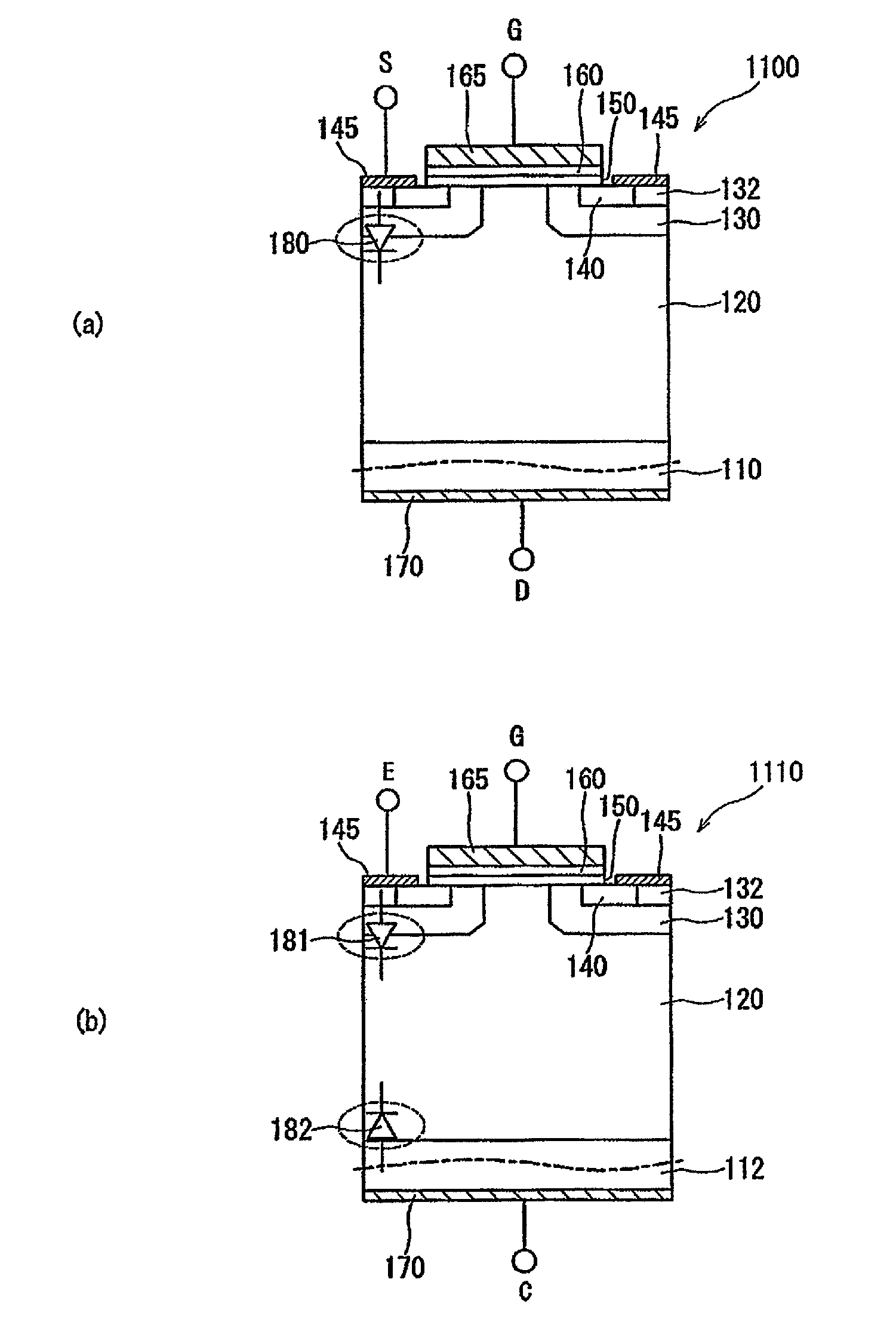

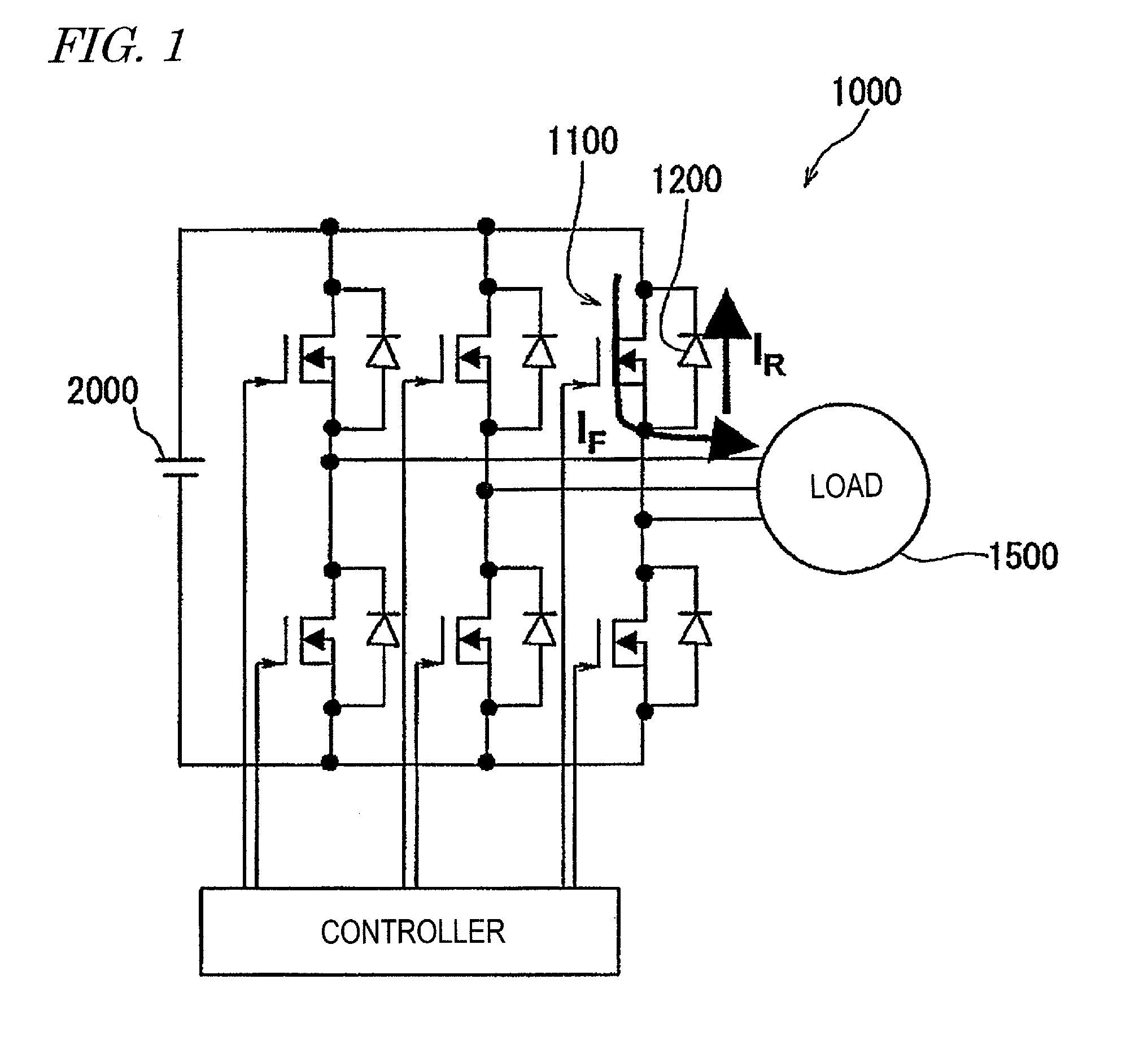

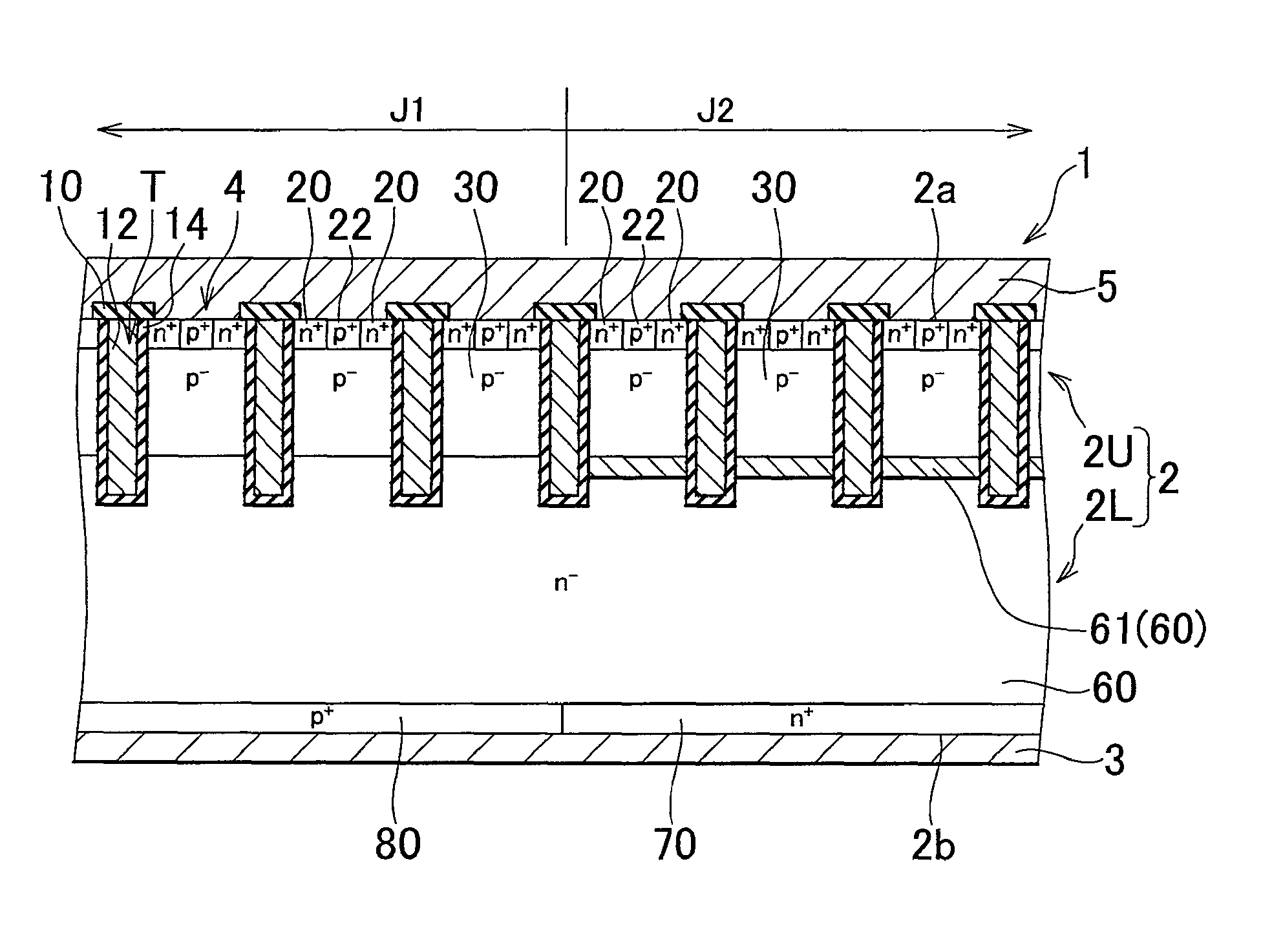

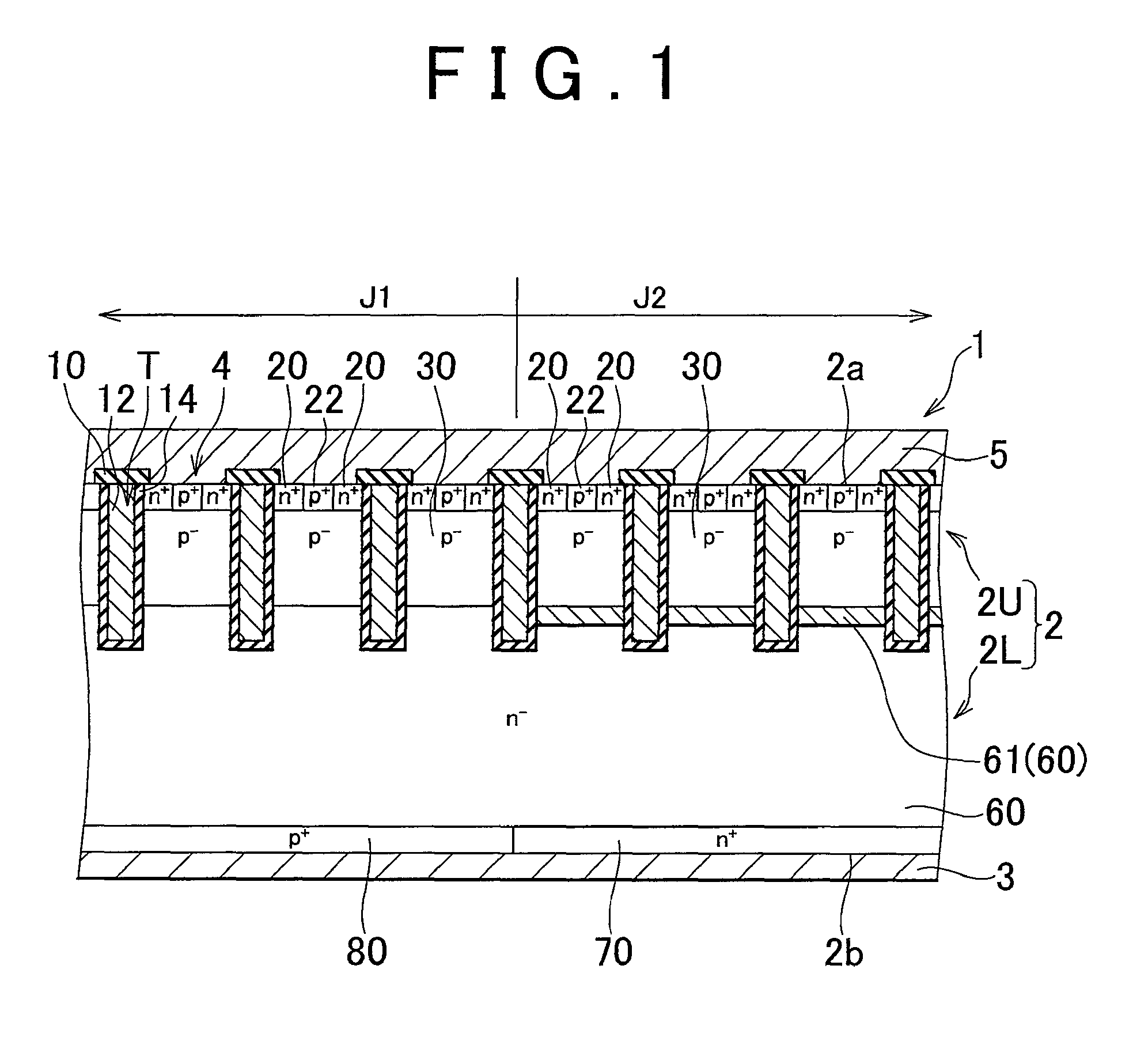

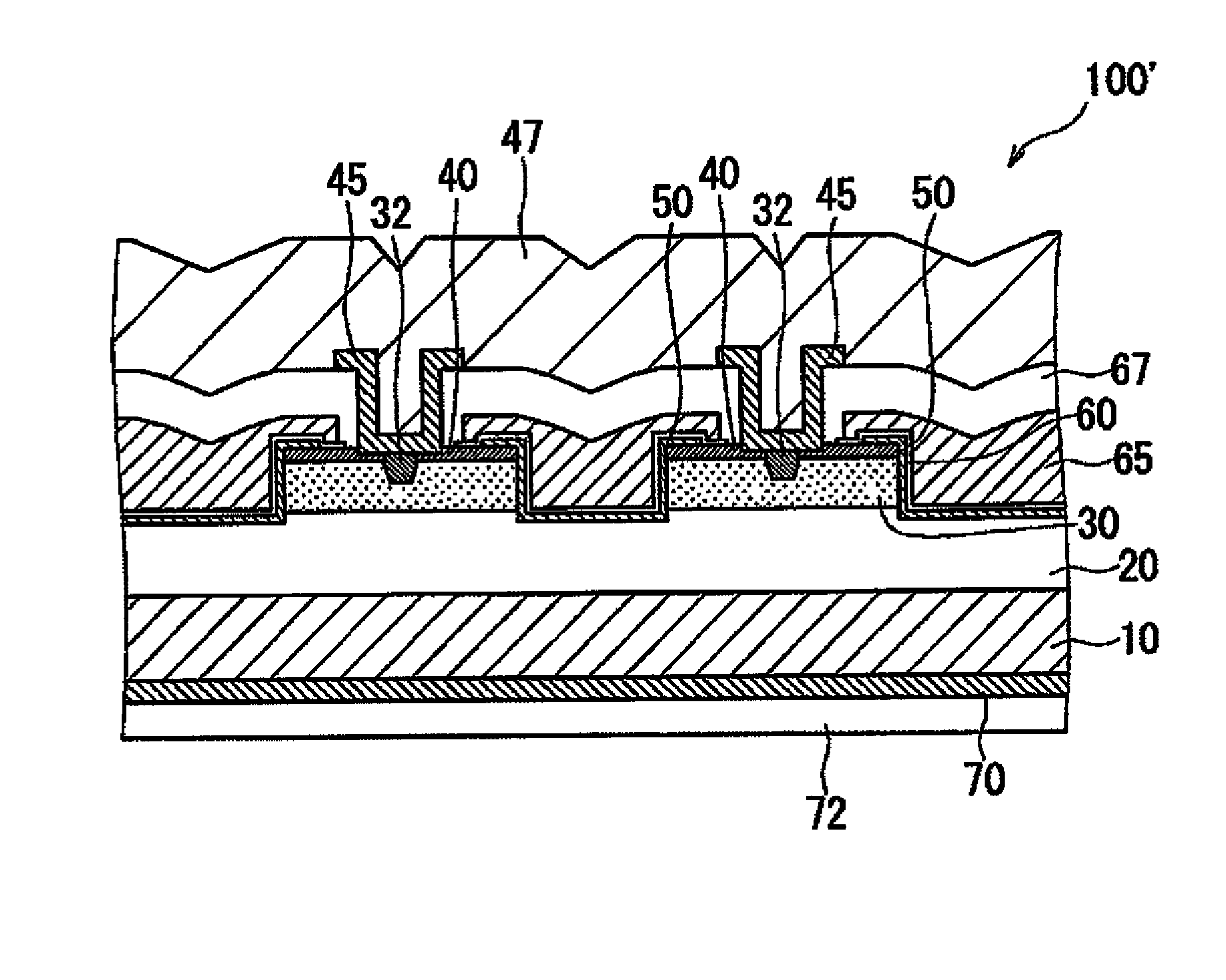

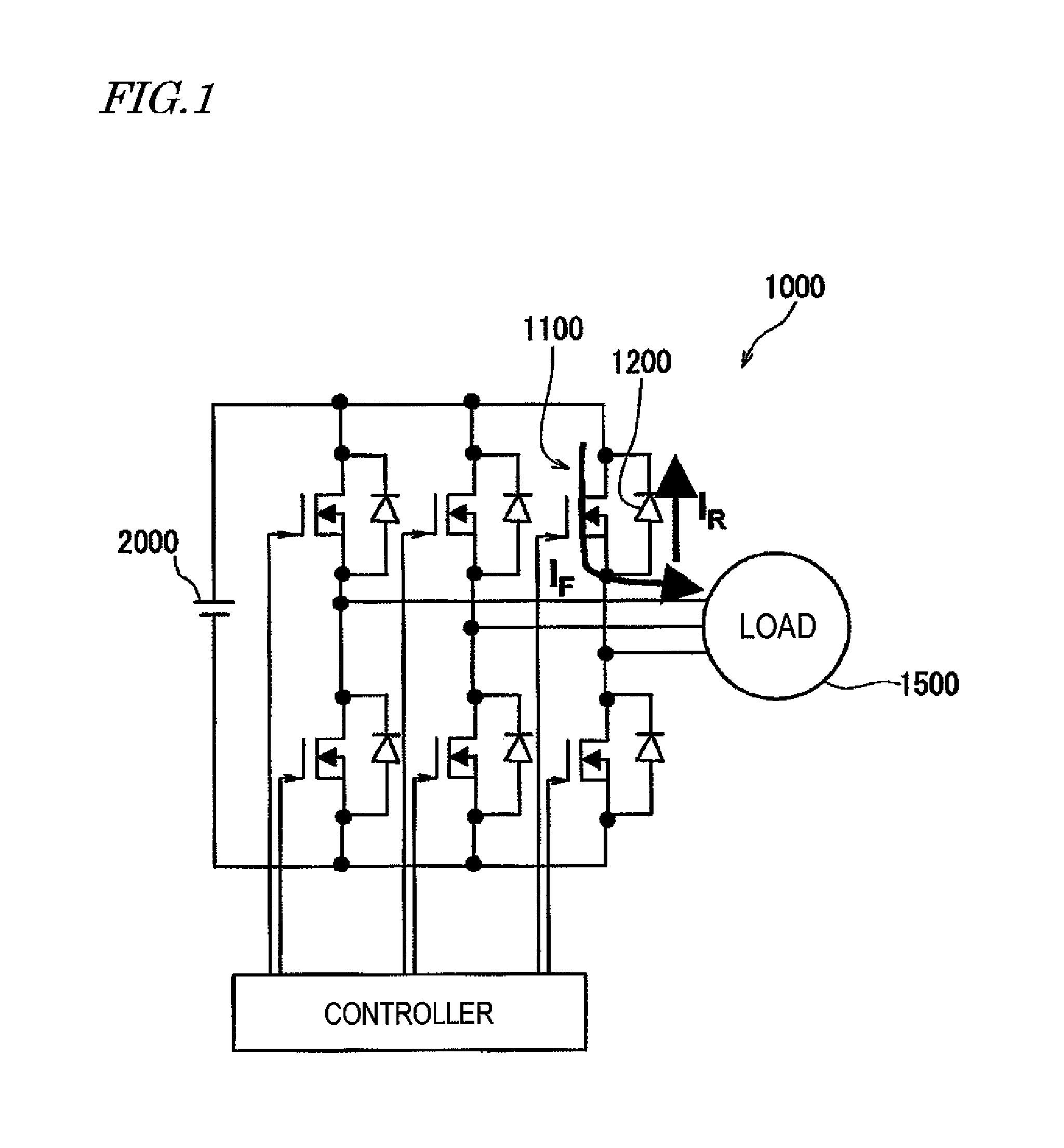

Semiconductor element, semiconductor device, and electric power converter

ActiveUS20120139623A1Increase the number ofIncrease ratingsTransistorEfficient power electronics conversionElectricityDevice material

A semiconductor element 100 including an MISFET according to the present invention is characterized by having diode characteristics in a reverse direction through an epitaxial channel layer 50. The semiconductor element 100 includes a semiconductor layer 20 of a first conductivity type, a body region 30 of a second conductivity type, source and drain regions 40 and 75 of the first conductivity type, an epitaxial channel layer 50 in contact with the body region, source and drain electrodes 45 and 70, a gate insulating film 60, and a gate electrode 65. If the voltage applied to the gate electrode of the MISFET is smaller than a threshold voltage, the semiconductor element 100 functions as a diode in which current flows from the source electrode 45 to the drain electrode 70 through the epitaxial channel layer 50. The absolute value of the turn-on voltage of this diode is smaller than that of the turn-on voltage of a body diode that is formed of the body region and the first silicon carbide semiconductor layer.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Semiconductor element, semiconductor device, and electric power converter

ActiveUS8283973B2Increase the number ofIncrease ratingsTransistorEfficient power electronics conversionDevice materialBody region

A semiconductor element 100 including an MISFET according to the present invention is characterized by having diode characteristics in a reverse direction through an epitaxial channel layer 50. The semiconductor element 100 includes a semiconductor layer 20 of a first conductivity type, a body region 30 of a second conductivity type, source and drain regions 40 and 75 of the first conductivity type, an epitaxial channel layer 50 in contact with the body region, source and drain electrodes 45 and 70, a gate insulating film 60, and a gate electrode 65. If the voltage applied to the gate electrode of the MISFET is smaller than a threshold voltage, the semiconductor element 100 functions as a diode in which current flows from the source electrode 45 to the drain electrode 70 through the epitaxial channel layer 50. The absolute value of the turn-on voltage of this diode is smaller than that of the turn-on voltage of a body diode that is formed of the body region and the first silicon carbide semiconductor layer.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

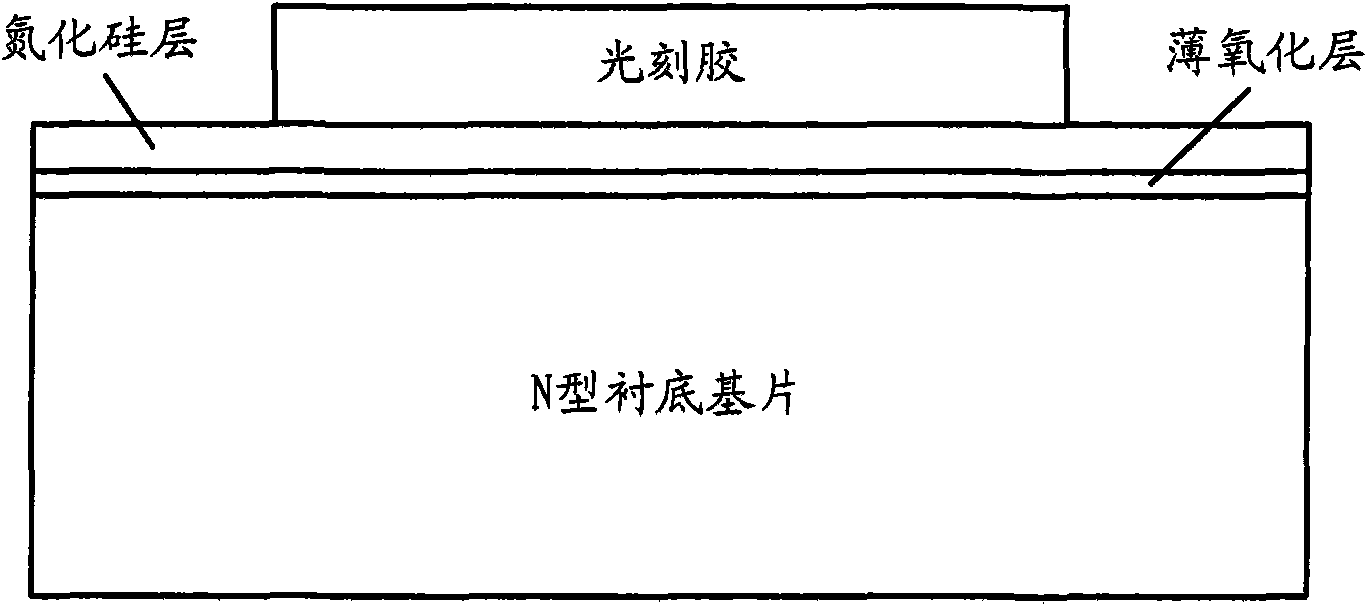

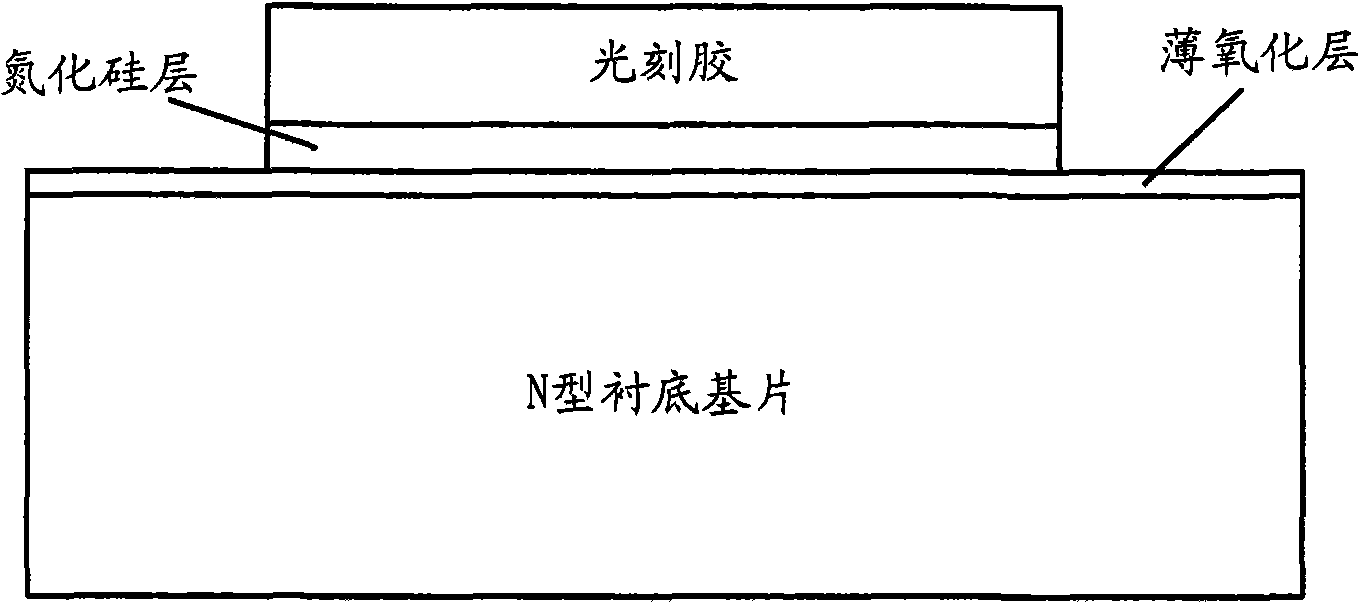

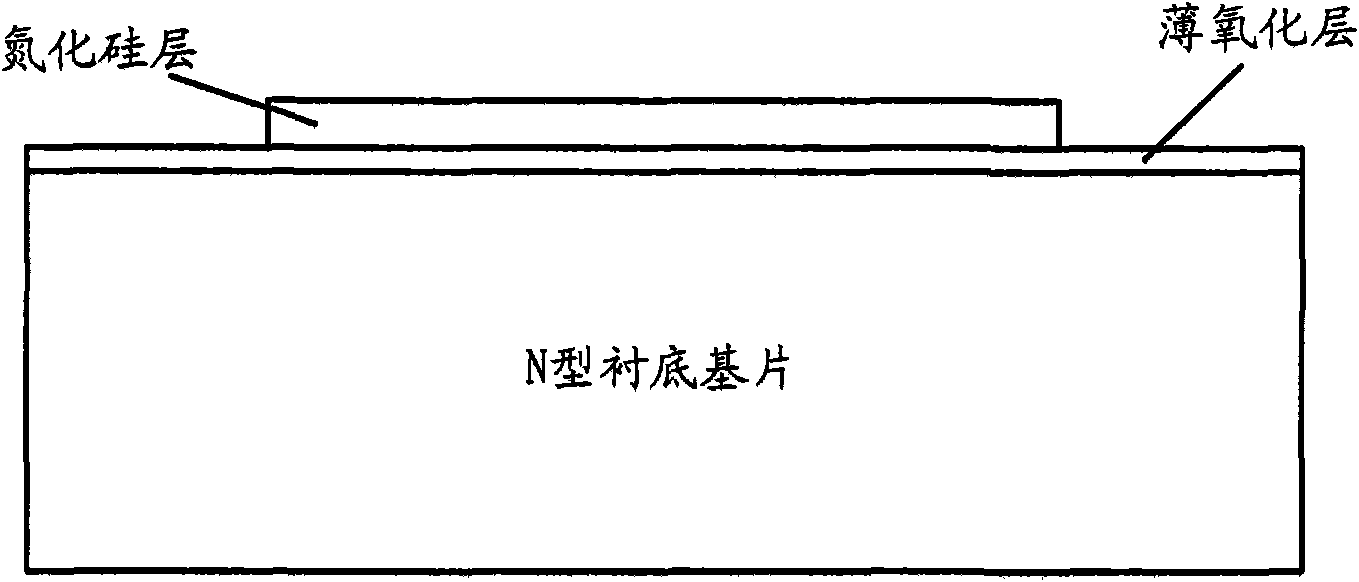

P-channel depletion MOS (metal oxide semiconductor) transistor and preparation method thereof

InactiveCN102136425ASimple manufacturing processImprove electrical performanceSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerBoron

The invention discloses a P-channel depletion MOS (metal oxide semiconductor) transistor and a preparation method thereof. The method comprises the following steps: preparing a field oxide layer on the upper surface outside an area of an MOS electrode to be prepared of an N-type substrate, and preparing a gate oxide layer on an area which is not covered by the field oxide layer; preparing an undoped polysilicon layer on an area of an MOS gate to be prepared on the gate oxide layer; injecting boron ions of the set dosage into the area which is not covered by the field oxide layer above the N-type substrate so that the undoped polysilicon layer forms a P-type polysilicon layer and the surface layer on the N-type substrate which is not covered by the undoped polysilicon layer and the field oxide layer forms a P-type source (drain) area; and performing annealing treatment on the N-type substrate after the source (drain) area and the P-type polysilicon layer are formed so as to obtain the P-channel depletion MOS transistor. The method simplifies the preparation process and increases the start voltage of the transistor.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

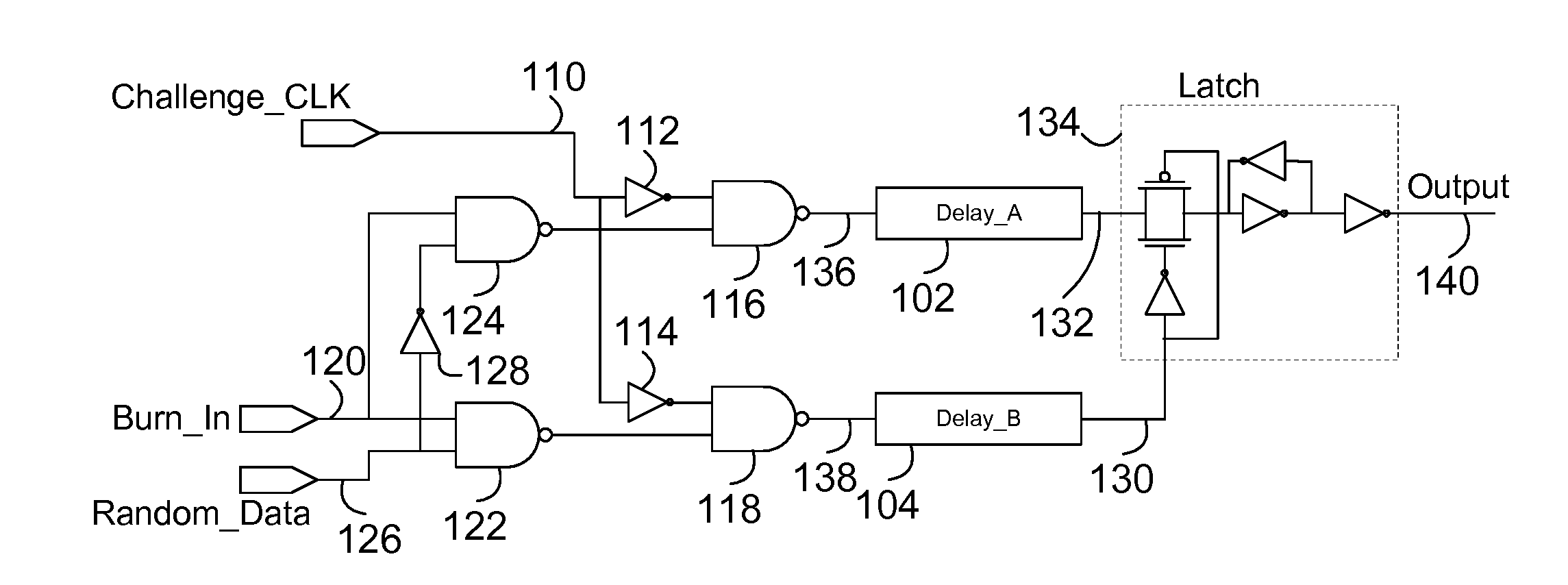

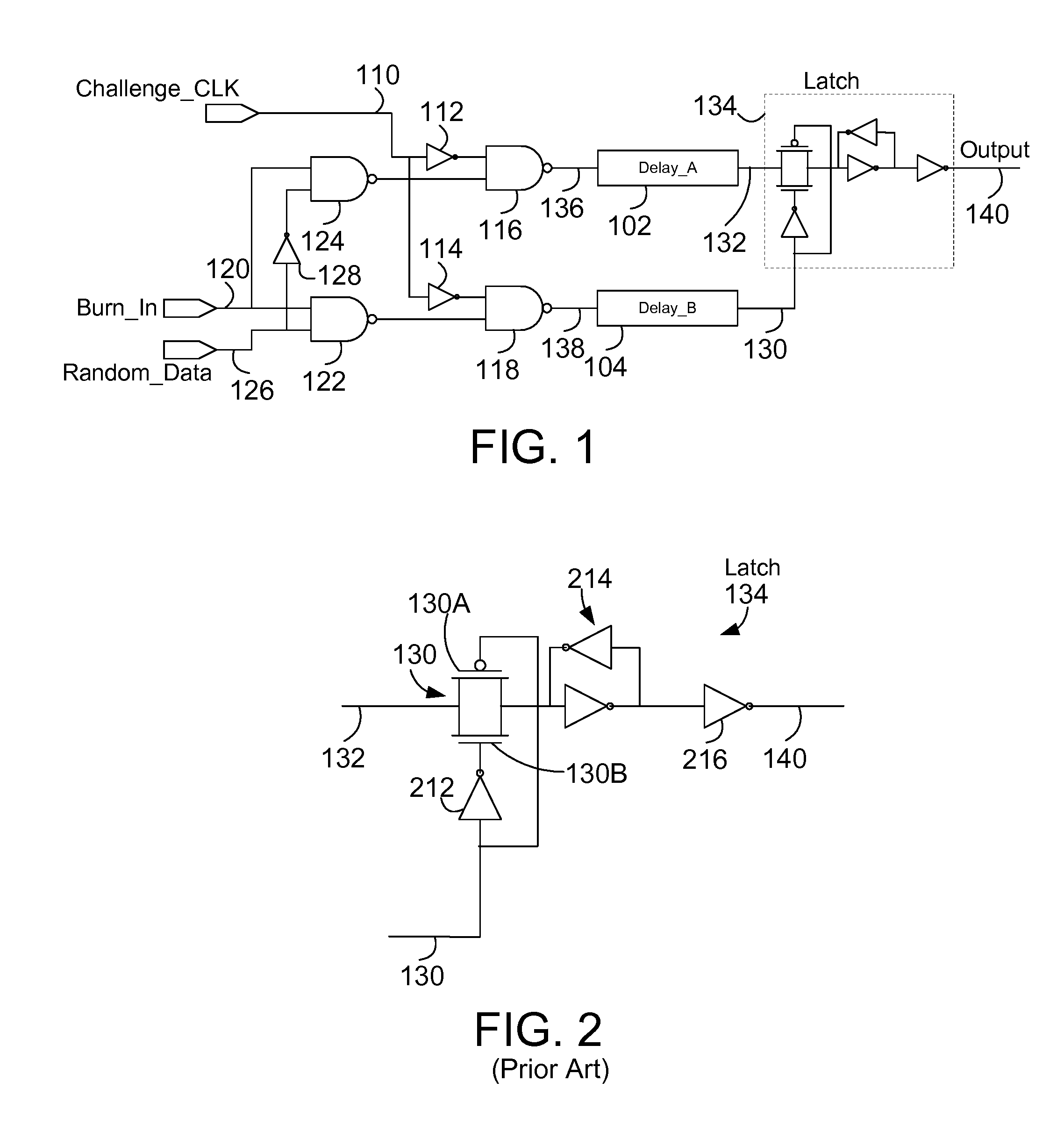

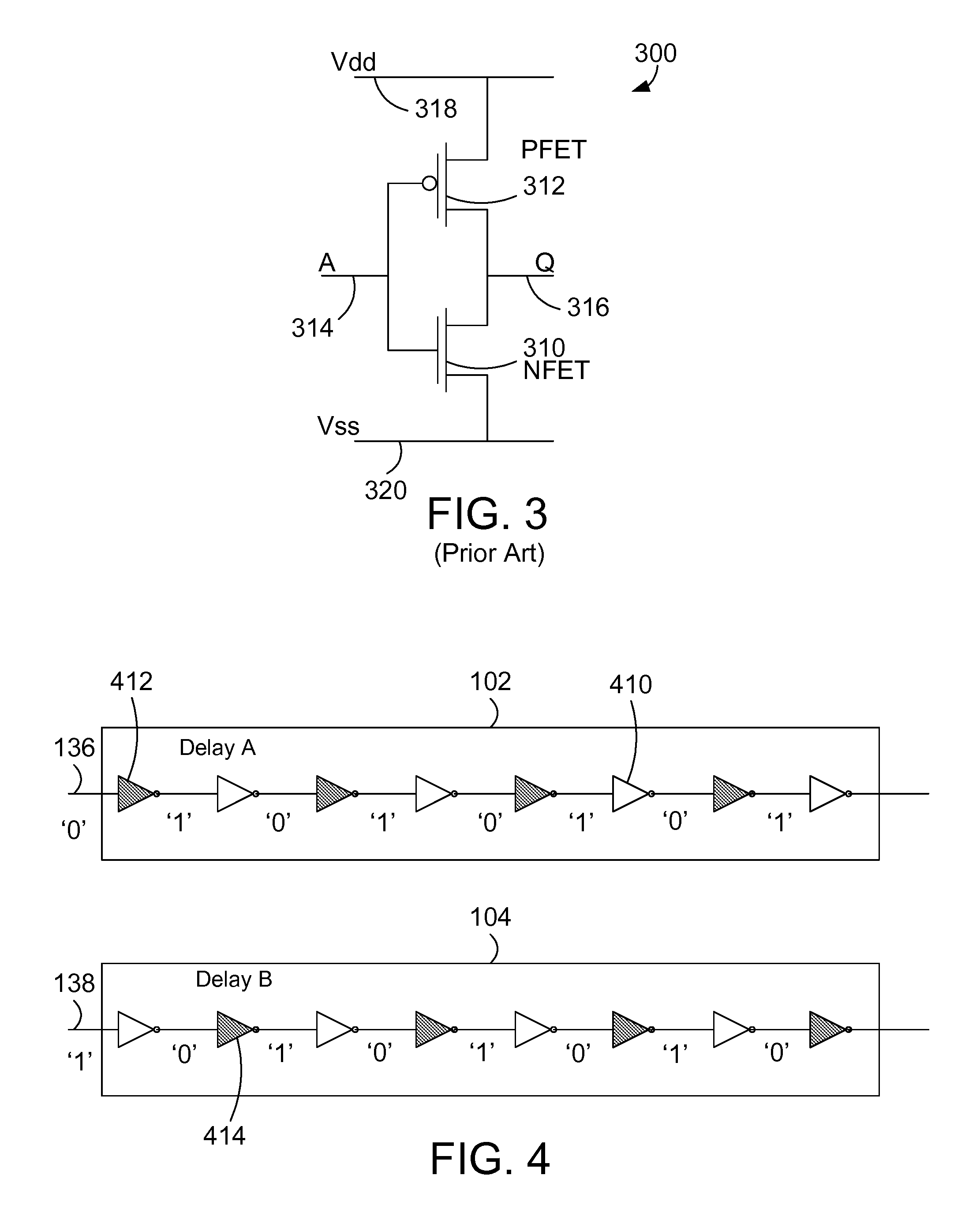

Delay chain burn-in for increased repeatability of physically unclonable functions

InactiveUS8159260B1Good repeatabilityAdditional variationDigital data processing detailsUnauthorized memory use protectionPhysical unclonable functionRepeatability

A circuit and method increases the repeatability of physically undetectable functions (PUFs) by enhancing the variation of signal delay through two delay chains during chip burn-in. A burn-in circuit holds the inputs of the two delay chains at opposite random values during the burn-in process. All the PFETs in the delay chains with a low value at the input will be burned in with a higher turn on voltage. Since the PFETs affected in the two delay chains are driven by opposite transitions at burn-in, alternating sets of delay components in the two delay chains are affected by the burn-in cycle. Under normal operation, both of the delay chains see the same input so only one chain has an increase in delay to achieve a statistically reliable difference in the two delay paths thereby increasing the overall repeatability of the PUF circuit.

Owner:INT BUSINESS MASCH CORP

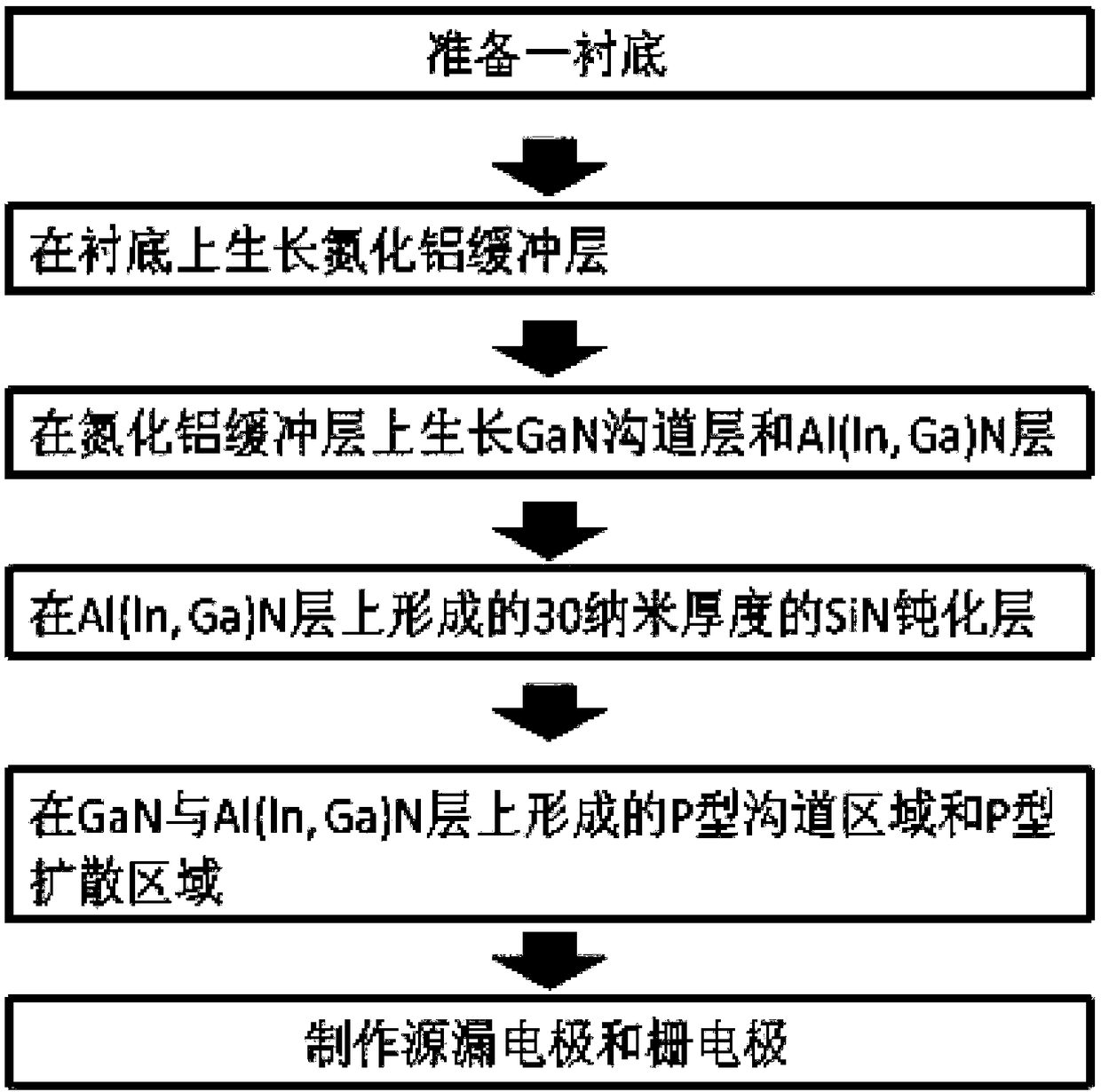

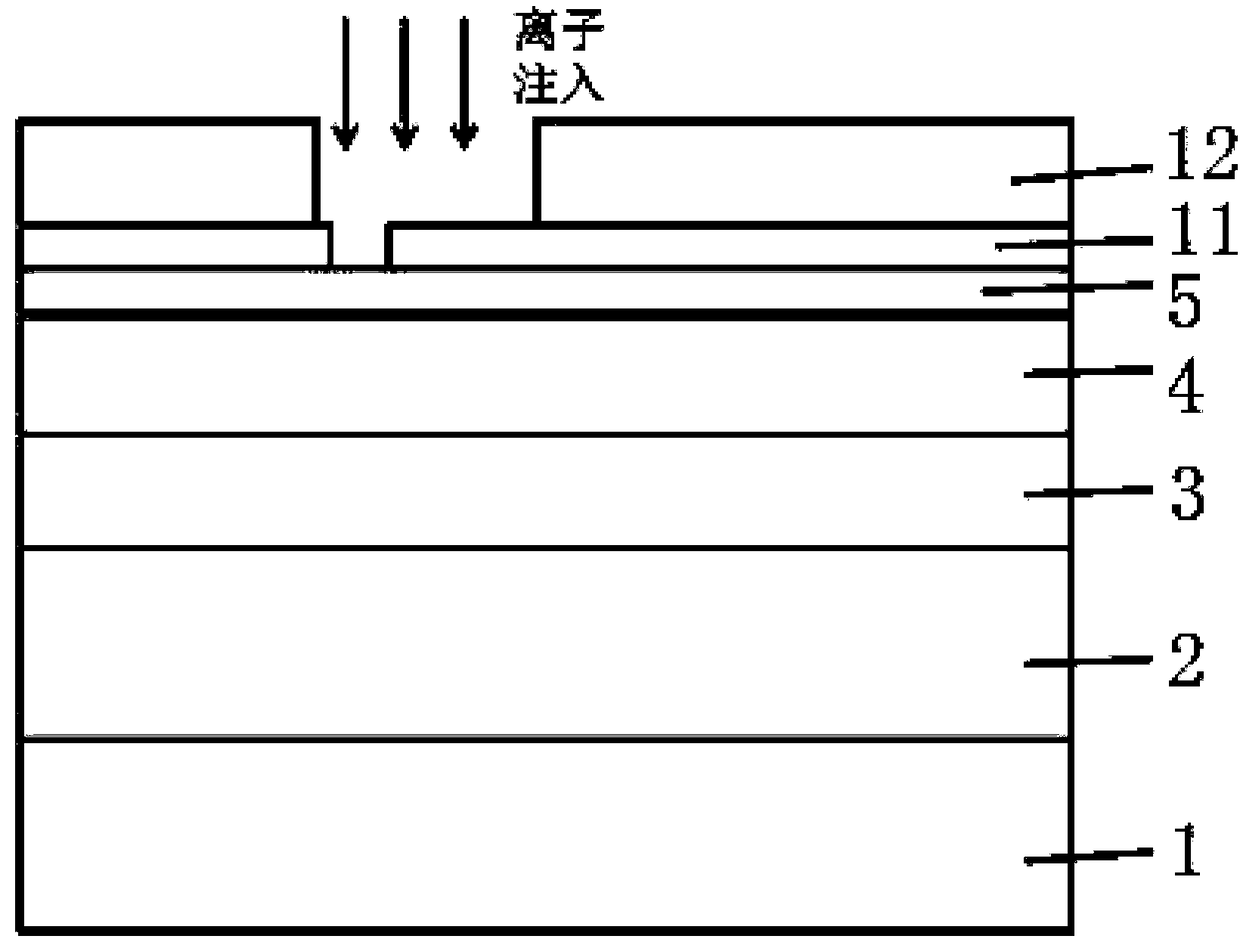

GaN-based HEMT device and preparation method thereof

ActiveCN108110054AImprove breakdown voltageIncrease the turn-on voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGallium nitrideIon implantation

The invention discloses a GaN-based HEMT device comprising a substrate layer, an aluminum nitride buffer layer, a gallium nitride channel layer, an Al(ln,Ga,Sc)N barrier layer and a silicon nitride passivation layer which are laminated from the bottom to the top in turn. The GaN-based HEMT device also comprises a P-type channel region which is arranged in the gallium nitride channel layer and theAl(ln,Ga,Sc)N barrier layer, a P-type diffusion region which is arranged in the Al(ln,Ga,Sc)N barrier layer, a source electrode and a drain electrode which are arranged on the Al(ln,Ga,Sc)N barrier layer, and a gate electrode which is arranged on the Al(ln,Ga,Sc)N barrier layer, wherein the P-type diffusion region is arranged between the gate electrode and the drain electrode. The invention also discloses a preparation method of the GaN-based HEMT device. The gallium nitride channel layer etching process involved in the manufacturing process of the GaN-based HEMT device relying on the etchingprocess in the prior art is omitted and changed into the ion injection process so that the consistency of the GaN-based HEMT device manufacturing process can be enhanced.

Owner:WAYTHON INTELLIGENT TECH SUZHOU CO LTD

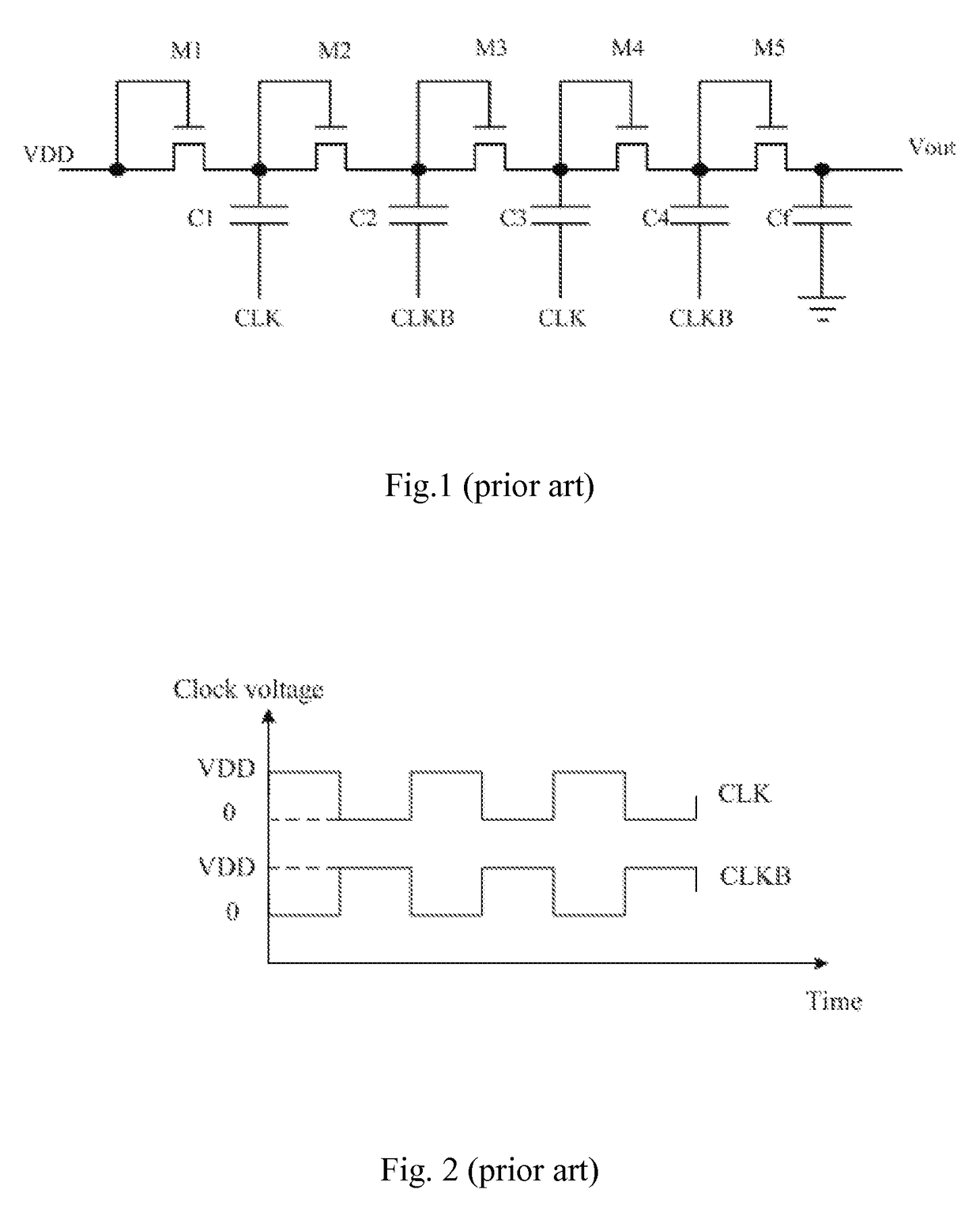

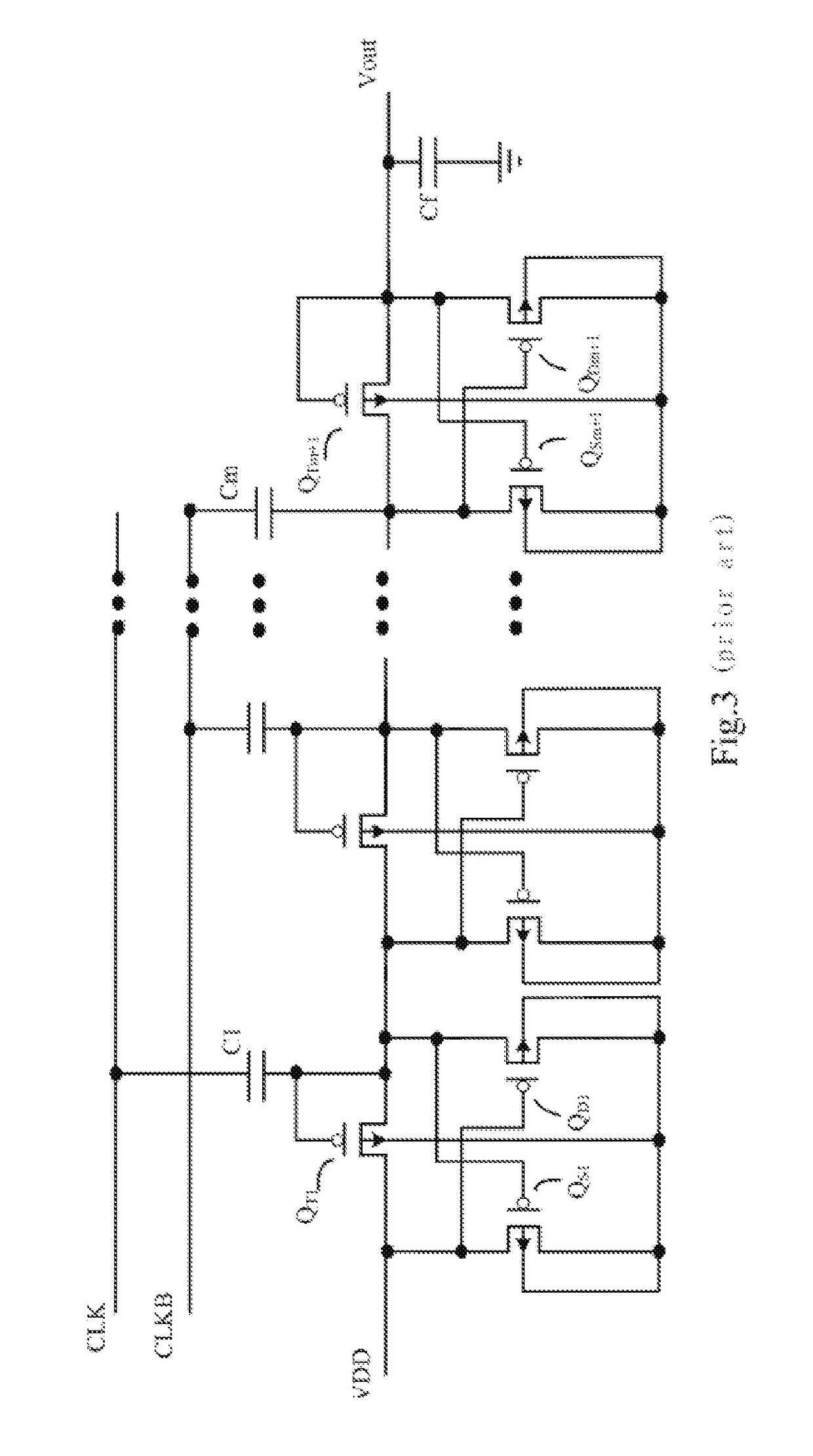

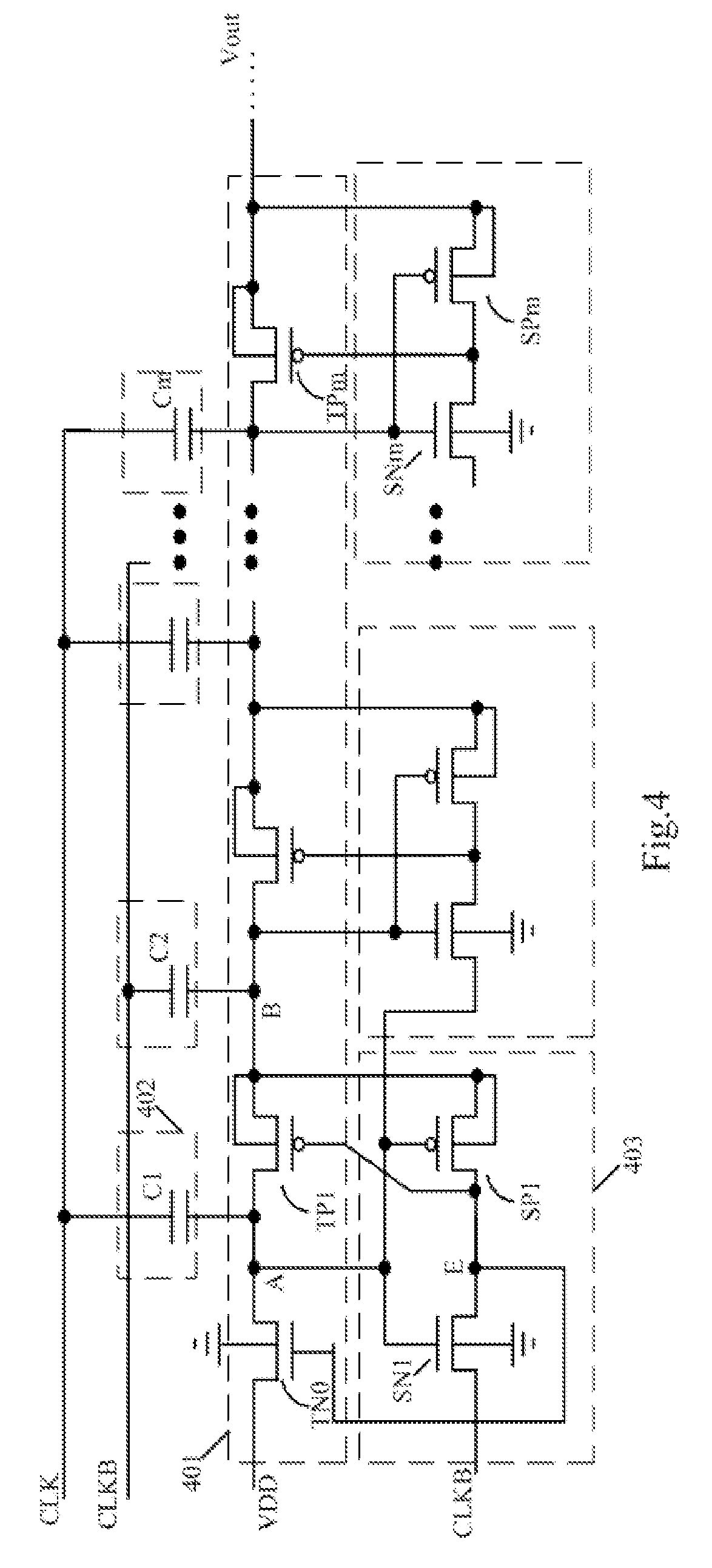

Charge pump circuit

ActiveUS8120413B2Avoid leakage currentRaise the threshold voltageAc-dc conversionApparatus without intermediate ac conversionEngineeringHigh transmission

A charge pump circuit includes a switch unit adapted to transmit charges from the input of the charge pump to the output of the charge pump; a transmission unit adapted to control turn-on or cut-off of an MOS transistor in the switch unit; and a charging unit in one-to-one correspondence with a PMOS transistor in the switch unit and adapted to store charges to boost the transmission voltage. A first NMOS transistor and at least two PMOS transistor are used as the switch unit during transmission of the charges, so that normal work can be enabled with high transmission efficiency in the case of a low source voltage.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

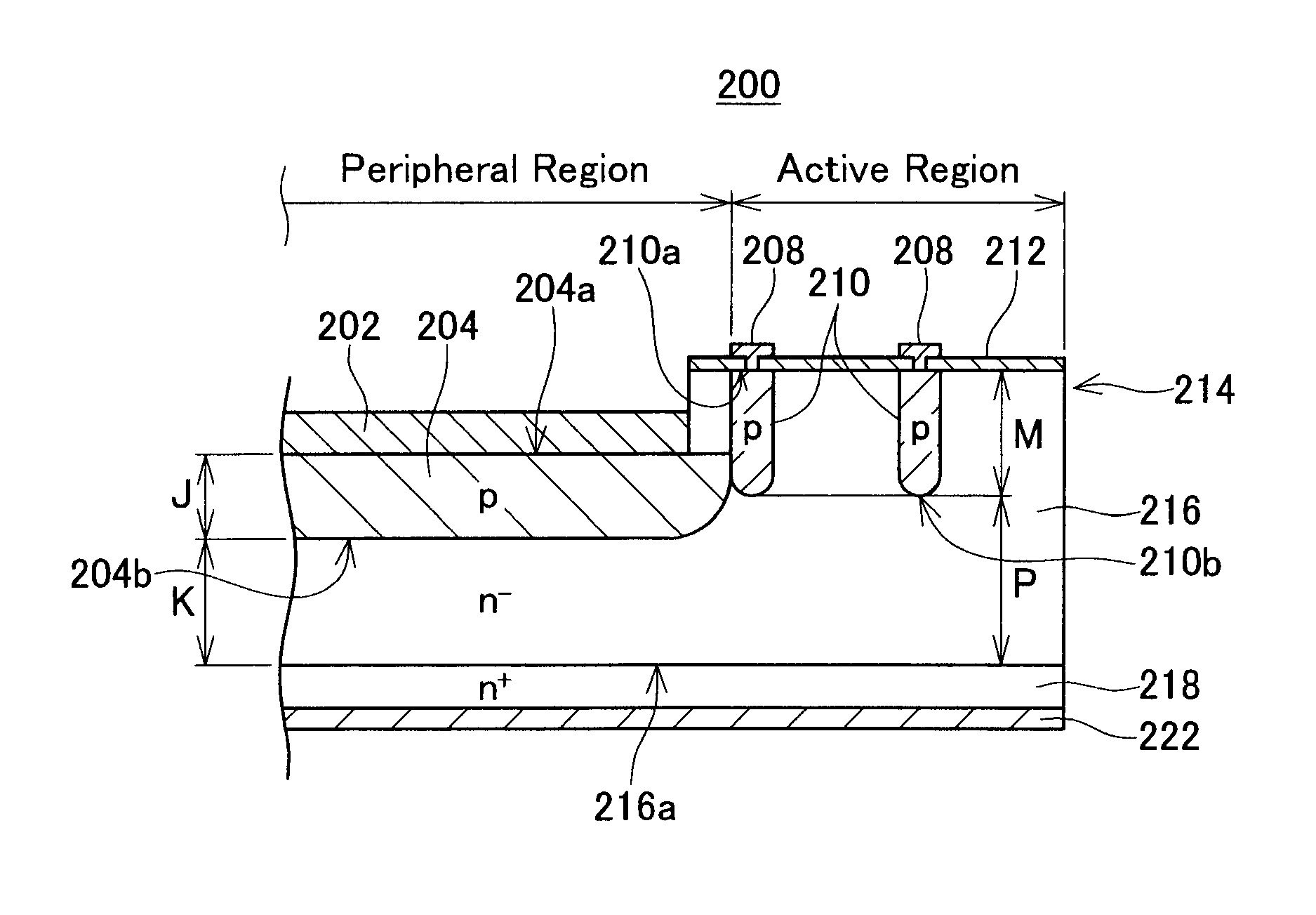

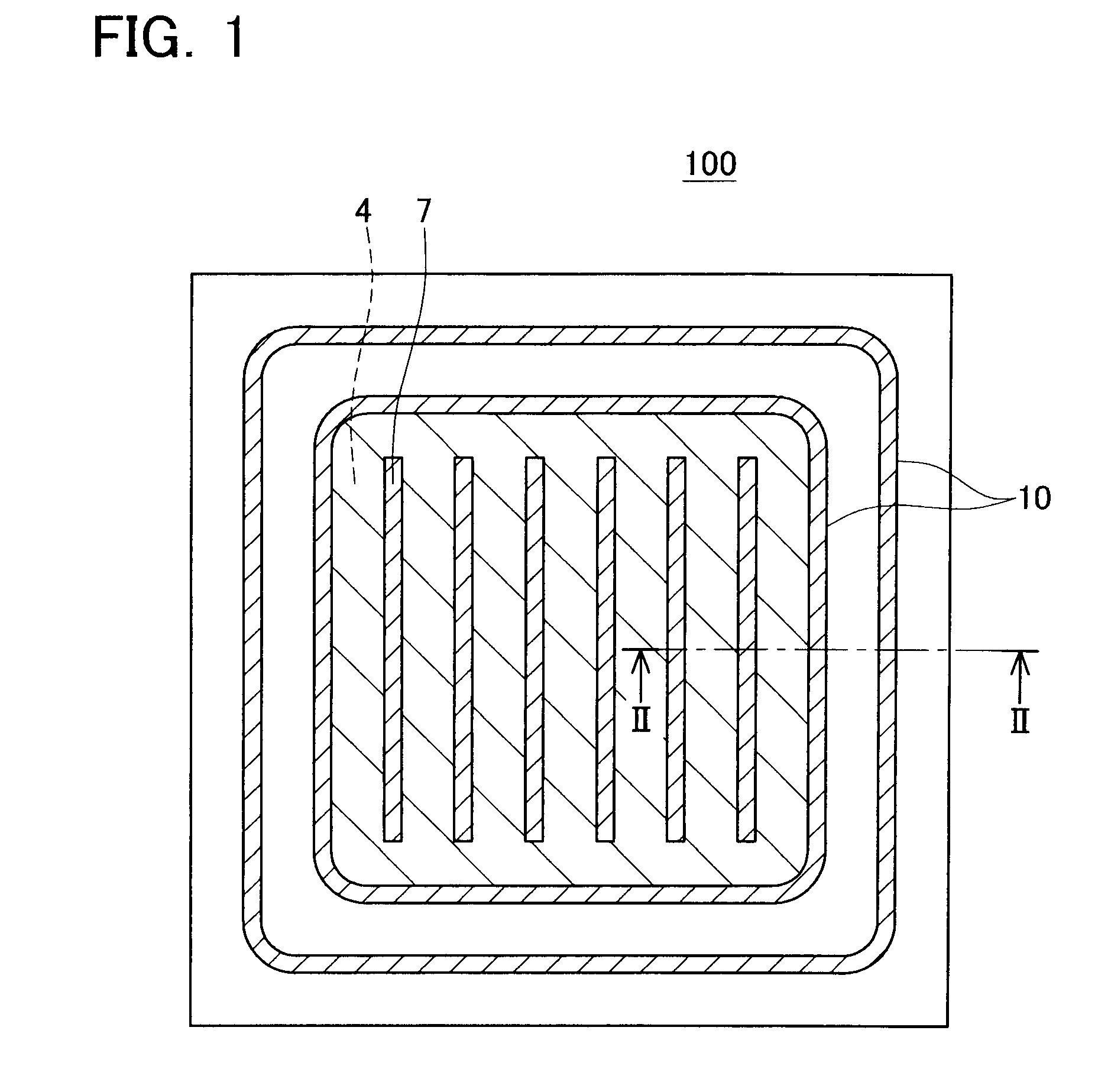

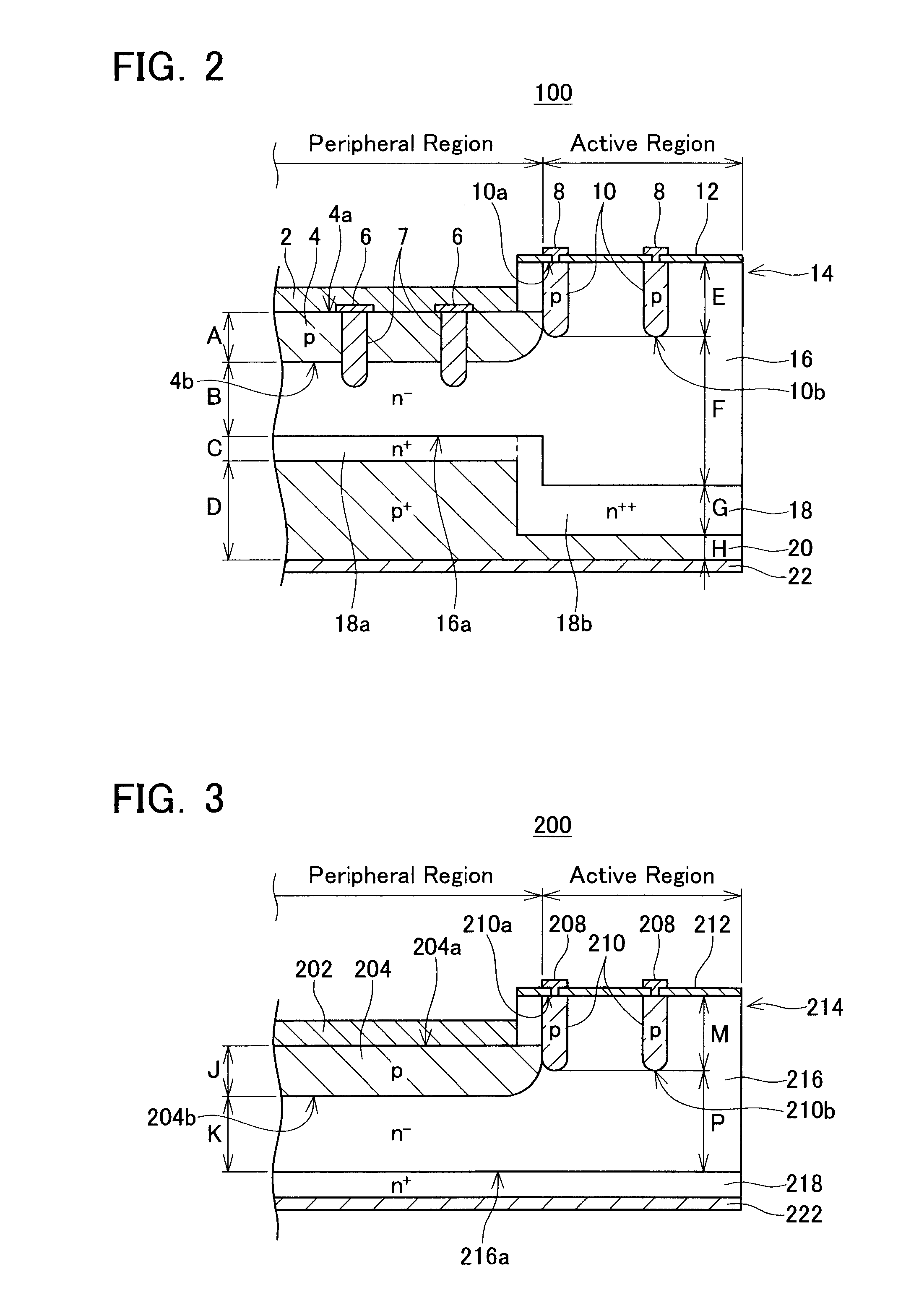

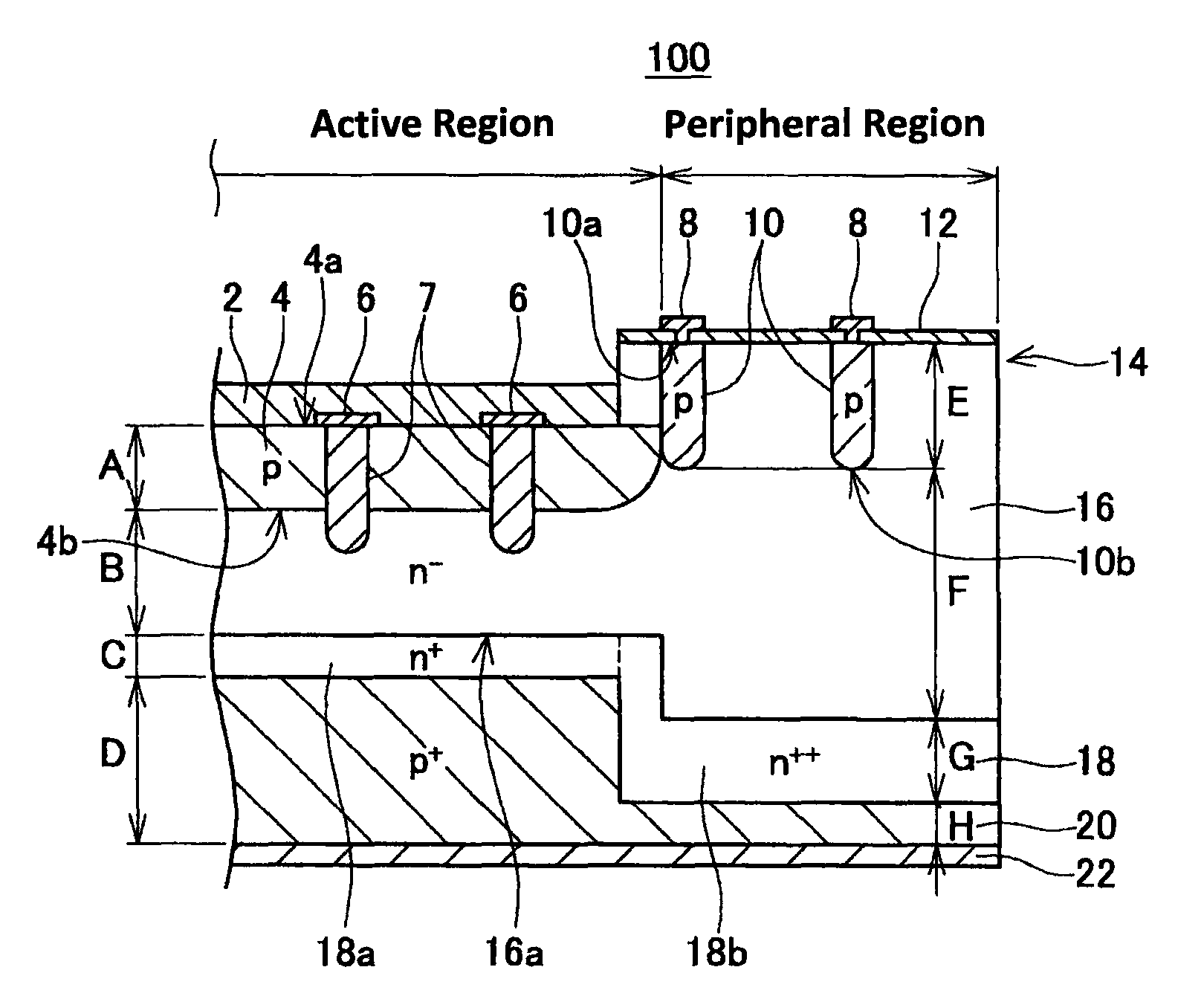

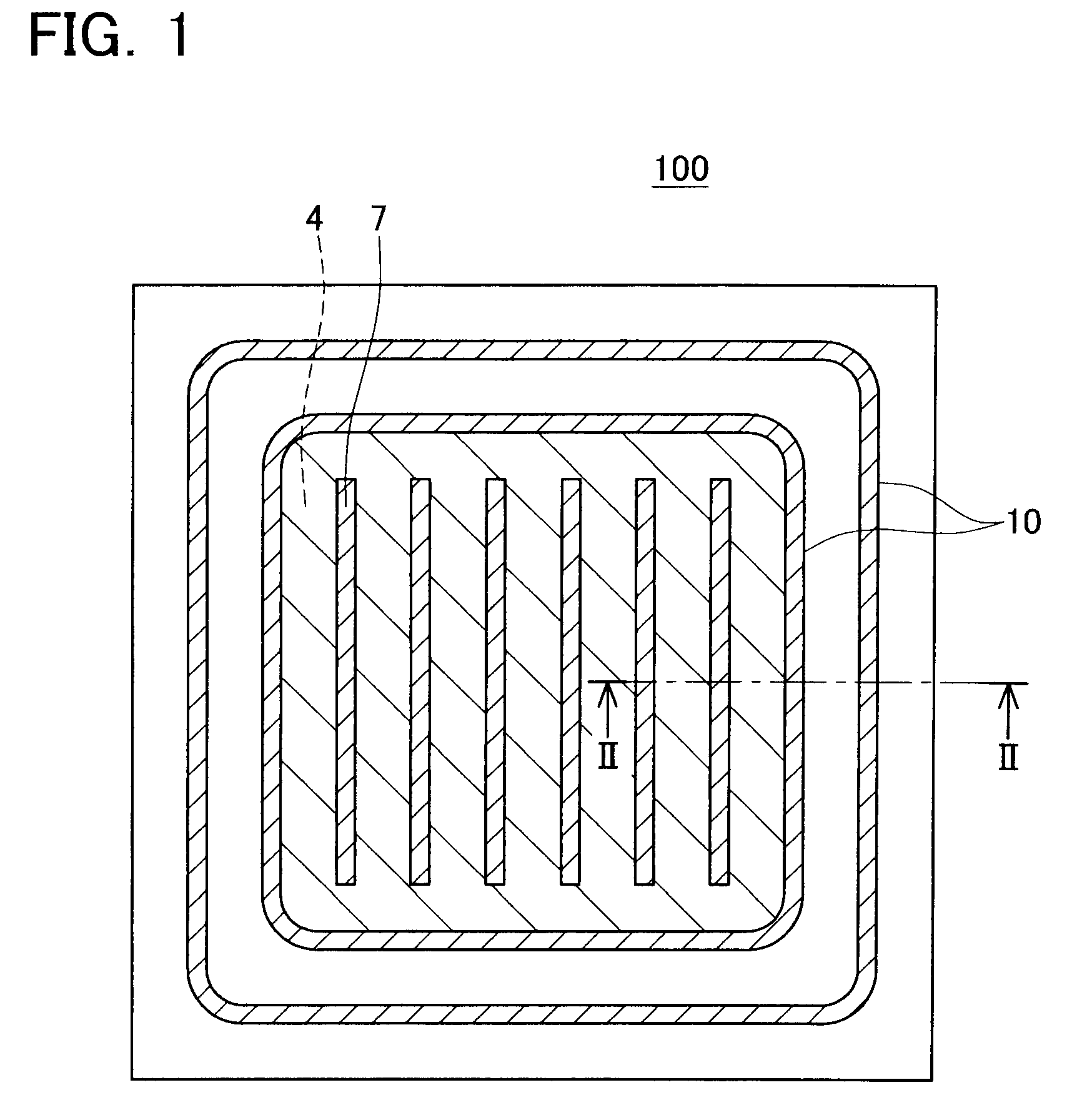

Semiconductor device

ActiveUS20100224907A1Improve dielectric breakdown strengthIncrease the on-resistanceSemiconductor/solid-state device detailsSolid-state devicesBody regionPhysics

To provide a semiconductor device in which dielectric breakdown strength in a peripheral region is increased without increasing on-resistance. An IGBT comprises a body region, guard ring, and collector layer. The body region is formed within an active region in a surface layer of a drift layer. The guard ring is formed within a peripheral region in the surface layer of the drift layer, and surrounds the body region. The collector layer is formed at a back surface side of the drift layer, and is formed across the active region and the peripheral region. A distance F between a back surface of the guard ring and the back surface of the drift layer is greater than a distance between a back surface of the body region and the back surface of the drift layer. A thickness H of the collector layer in the peripheral region is smaller than a thickness D of the collector layer in the active region.

Owner:DENSO CORP

IGBT semiconductor device

ActiveUS7973363B2Increasing the thicknessLow efficiencyThyristorSemiconductor/solid-state device detailsPower semiconductor deviceSurface layer

To provide a semiconductor device in which dielectric breakdown strength in a peripheral region is increased without increasing on-resistance. An IGBT comprises a body region, guard ring, and collector layer. The body region is formed within an active region in a surface layer of a drift layer. The guard ring is formed within a peripheral region in the surface layer of the drift layer, and surrounds the body region. The collector layer is formed at a back surface side of the drift layer, and is formed across the active region and the peripheral region. A distance F between a back surface of the guard ring and the back surface of the drift layer is greater than a distance between a back surface of the body region and the back surface of the drift layer. A thickness H of the collector layer in the peripheral region is smaller than a thickness D of the collector layer in the active region.

Owner:DENSO CORP

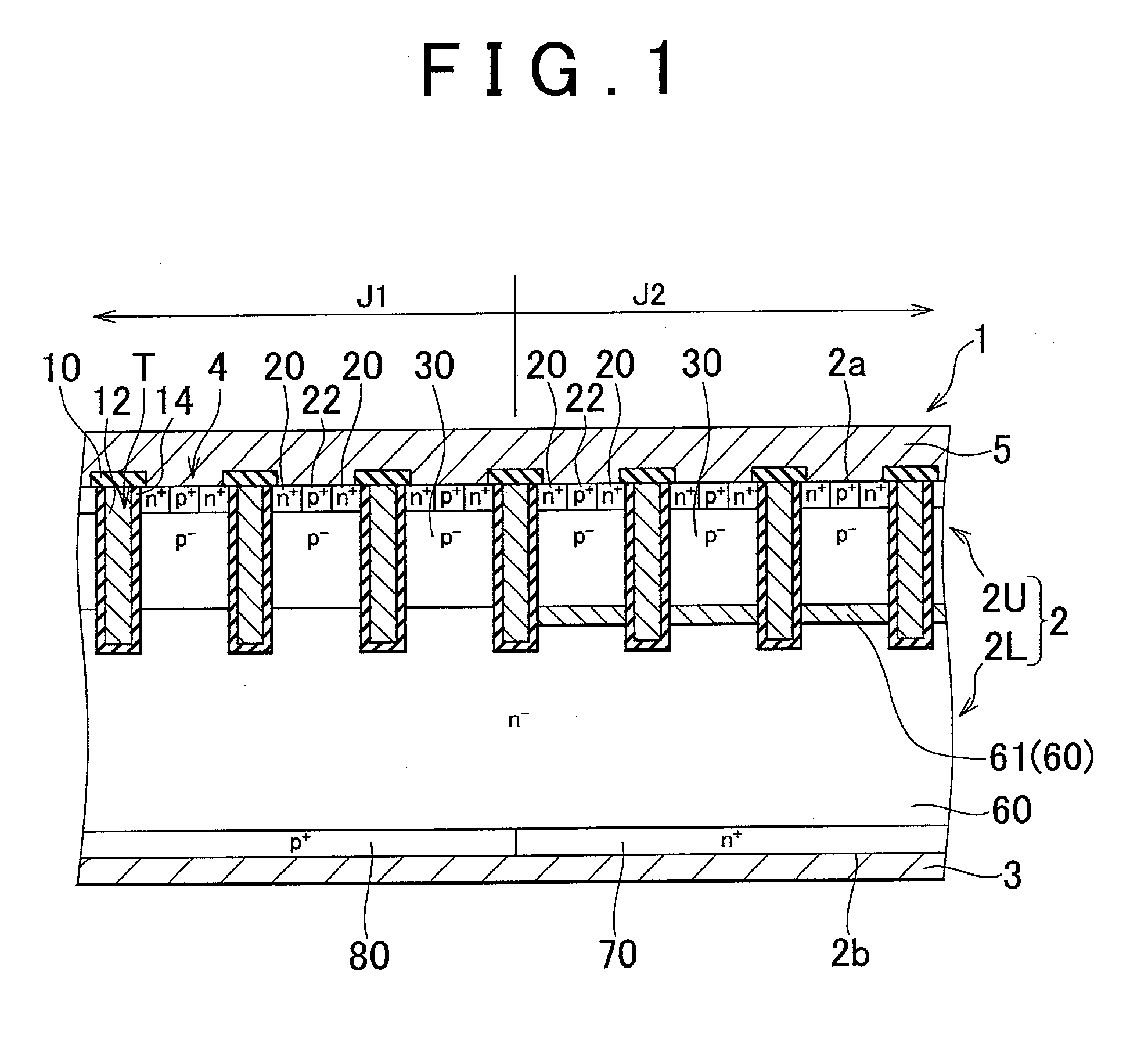

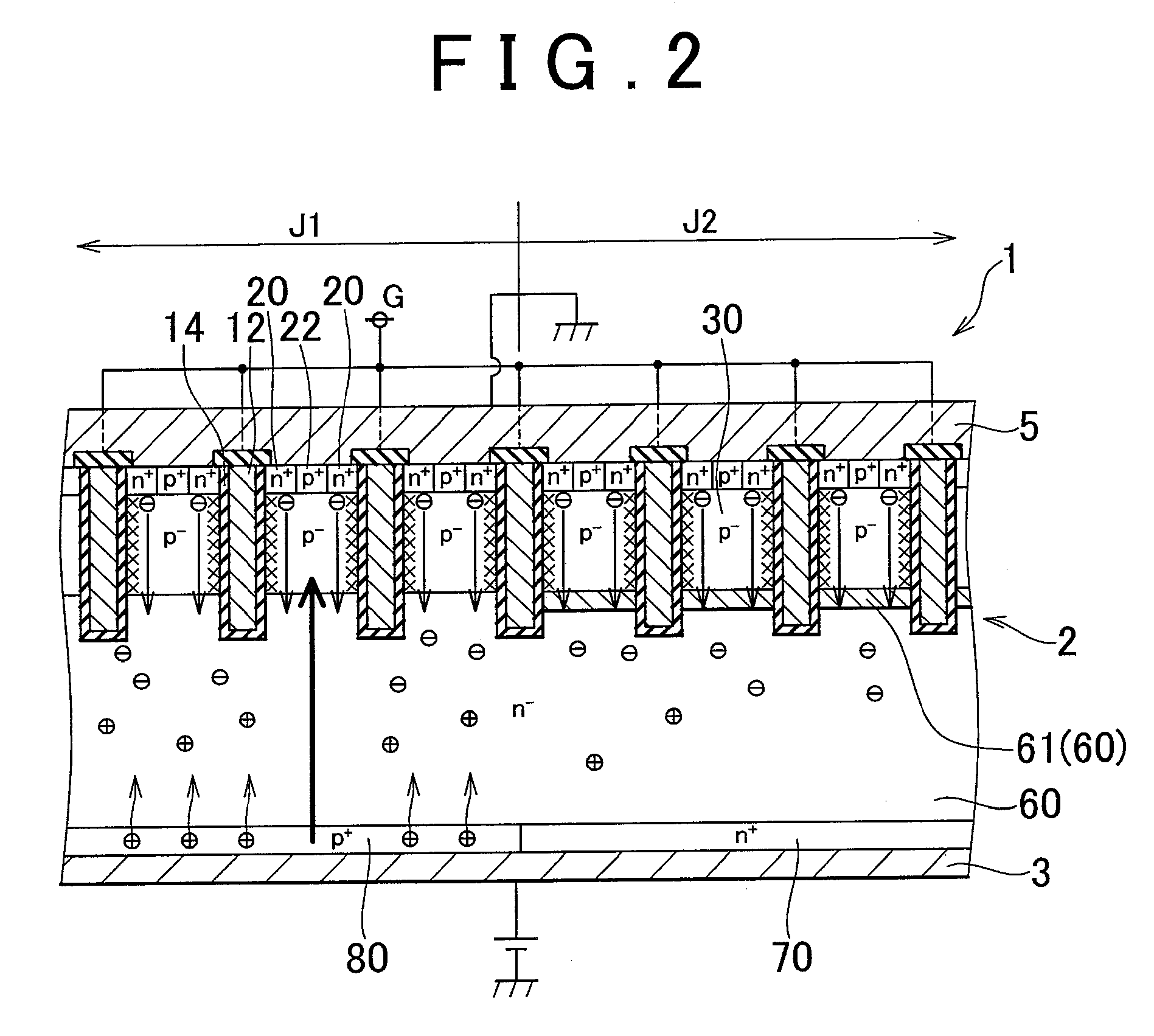

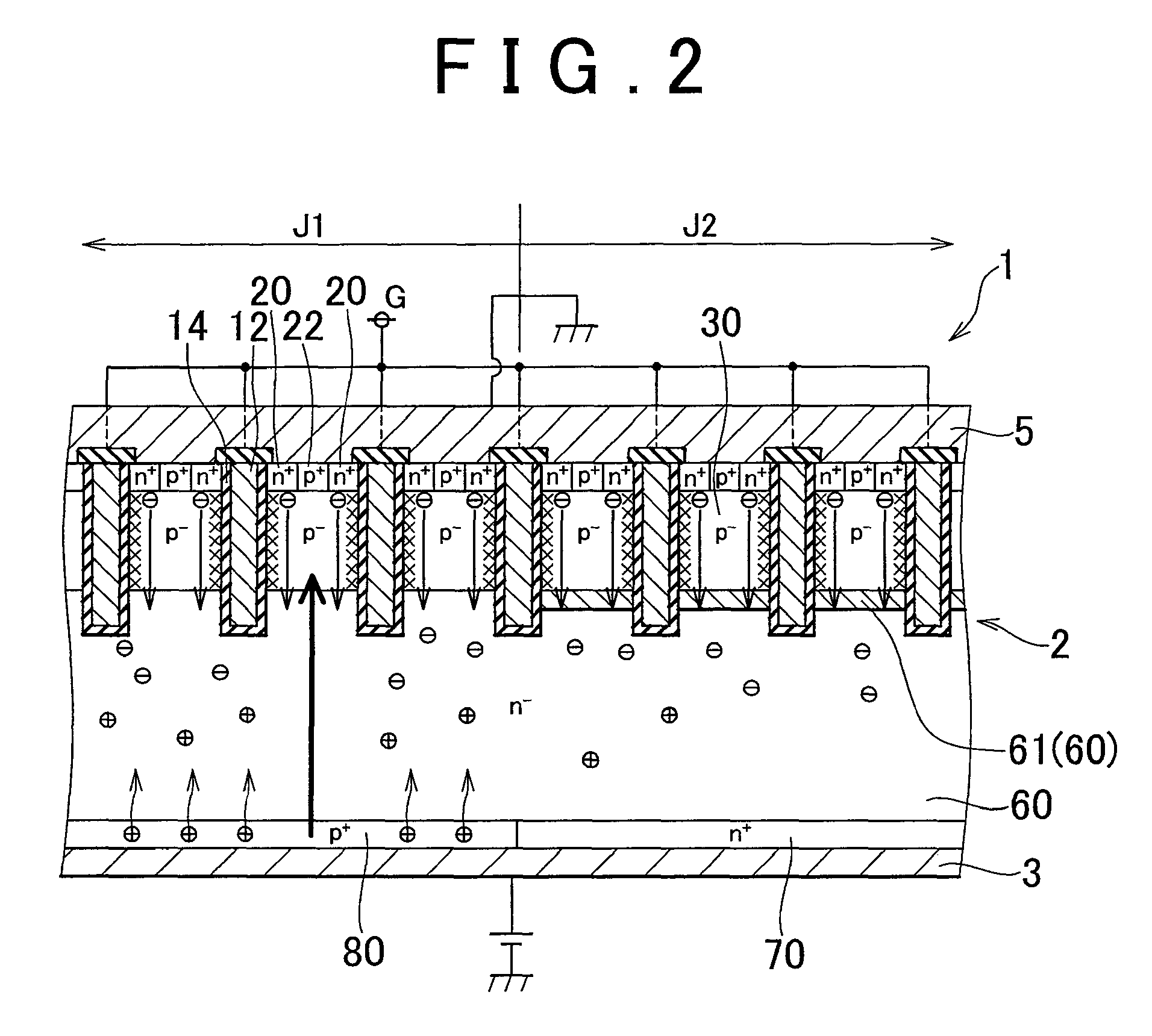

Semiconductor device having IGBT and diode

InactiveUS7952143B2Reduce recovery lossIncrease the turn-on voltageTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

Owner:TOYOTA JIDOSHA KK

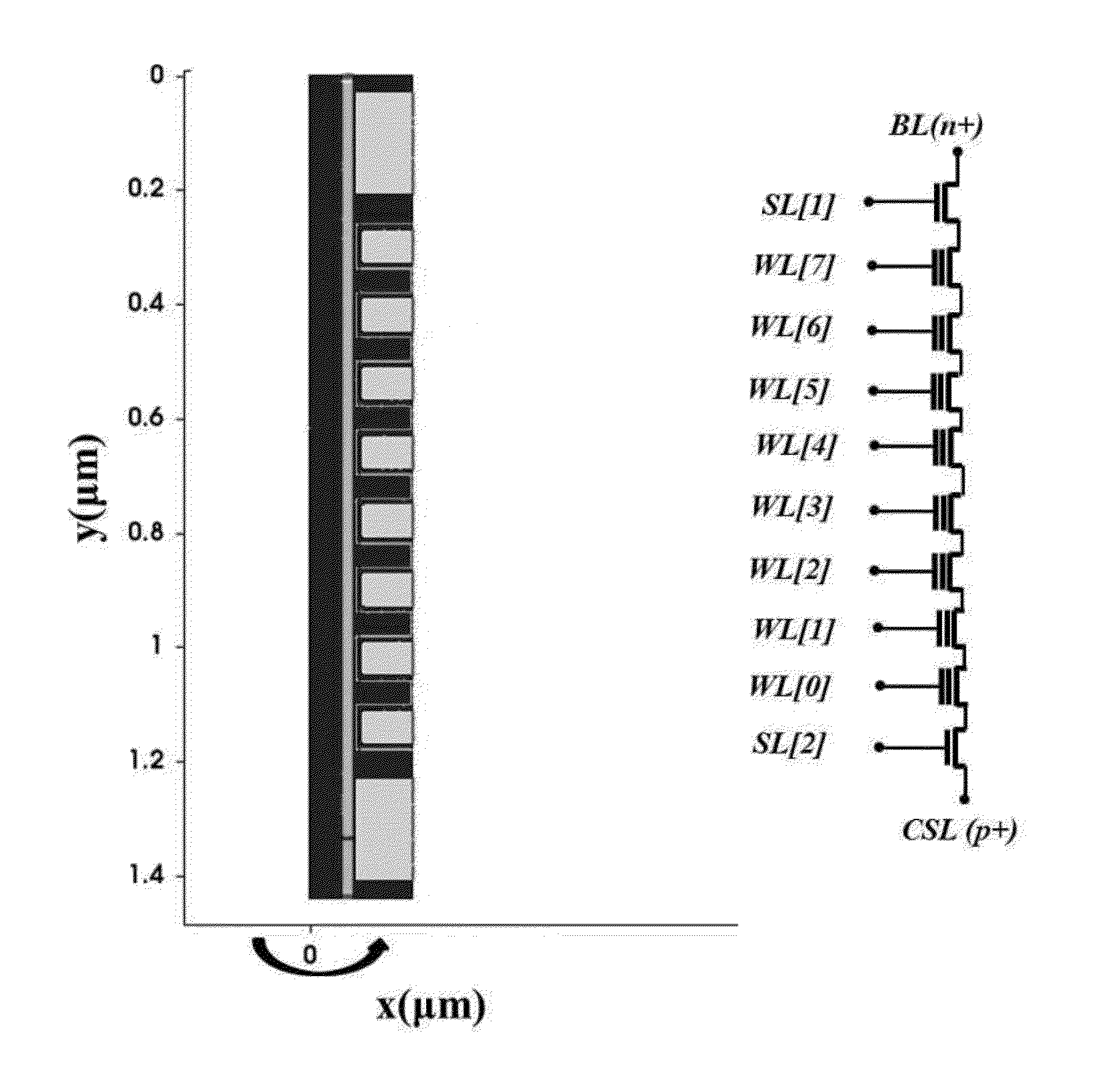

Cell string and reading method for the cell string

ActiveUS20150348639A1Small distribution of threshold voltageGood refresh marginSolid-state devicesRead-only memoriesMechanical engineeringMaterials science

Provided are a cell string and a reading method for the cell string. The cell string includes a semiconductor body formed on a surface of an insulating layer, first and second semiconductor regions formed at respective ends of the semiconductor body and are formed by being doped with different types of impurities, two or more control electrodes which are separated from each other to be electrically isolated, and a gate insulating film stack which is formed between the semiconductor body and the control electrodes, wherein the semiconductor body is configured to include at least two layers, and adjacent layers of the semiconductor body have different energy band gaps, wherein the semiconductor body is formed by an intrinsic semiconductor or a semiconductor being doped with impurities, and wherein the first and second semiconductor regions are doped with impurities of which concentration is higher than that of the semiconductor body.

Owner:SEOUL NAT UNIV R&DB FOUND

Spiro compound and application thereof

InactiveCN109796296ALower turn-on voltageImprove external quantum efficiencySolid-state devicesSemiconductor/solid-state device manufacturingElectricityOrganic electroluminescence

The invention belongs to the field of organic electroluminescent materials, and discloses a spiro compound and application thereof. The spiro compound has good thermal stability and device stability.The spiro compound serves as a main body material of a luminescent layer of an anelectroluminescent device, or an object material is doped in the luminescent layer of the electroluminescent device, the cut-in voltage of the device is significantly lowered, the luminous efficiency is improved, and the stability of the device is obviously improved.

Owner:AAC TECH NANJING

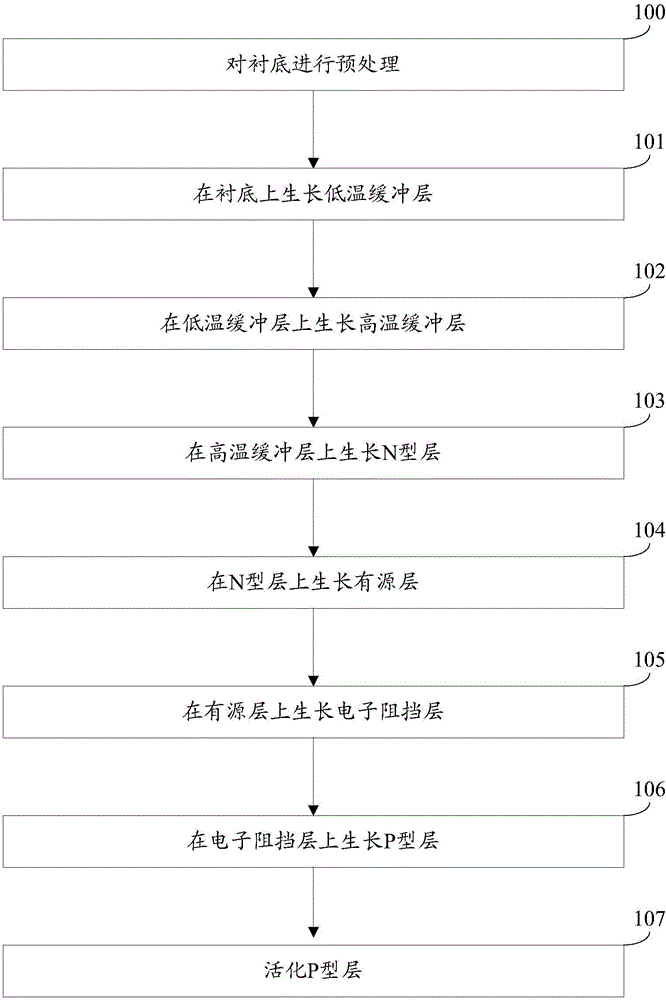

Growth method for light-emitting diode epitaxial wafer

ActiveCN105957927AReduced activityIncorporating efficiency benefitsSemiconductor devicesQuantum wellHigh pressure

The invention discloses a growth method for a light-emitting diode epitaxial wafer, and belongs to the technical field of semiconductors. The method comprises the step: sequentially growing a low-temperature buffering layer, a high-temperature buffering layer, an N-type layer, an active layer, an electronic blocking layer and a P-type layer on a substrate. The active layer comprises a first sub-layer and a second sub-layer, and the growth atmospheres of a quantum well layer in the first sub-layer, a quantum barrier layer in the first sub-layer, a quantum well layer in the second sub-layer and a quantum barrier layer in the second sub-layer are sequentially N2 and H2 mixed gas, pure H2, pure N2, and N2 and H2 mixed gas. The quantum well layer in the first sub-layer employs a variable pressure and variable temperature growth mode, and the quantum barrier layer in the first sub-layer employs a high-pressure and high-temperature growth mode. The quantum well layer in the second sub-layer employs a low-pressure and low-temperature growth mode, and the quantum barrier layer in the second sub-layer employs a variable pressure growth mode. The quantum barrier layer in the first sub-layer employs trimethyl gallium as a gallium source. The method improves the light-emitting efficiency.

Owner:HC SEMITEK SUZHOU

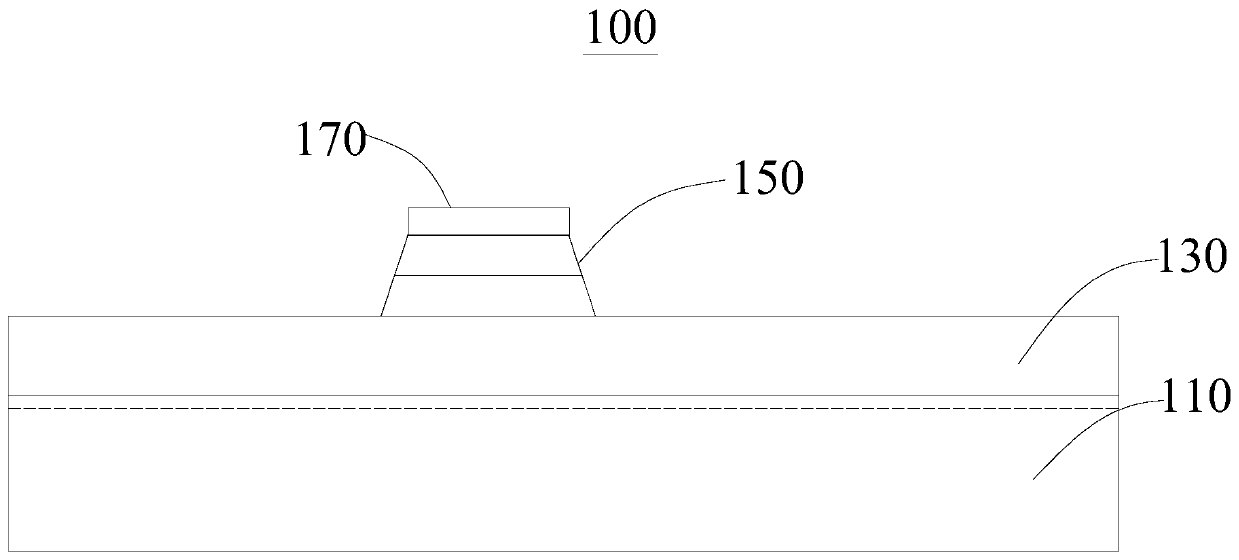

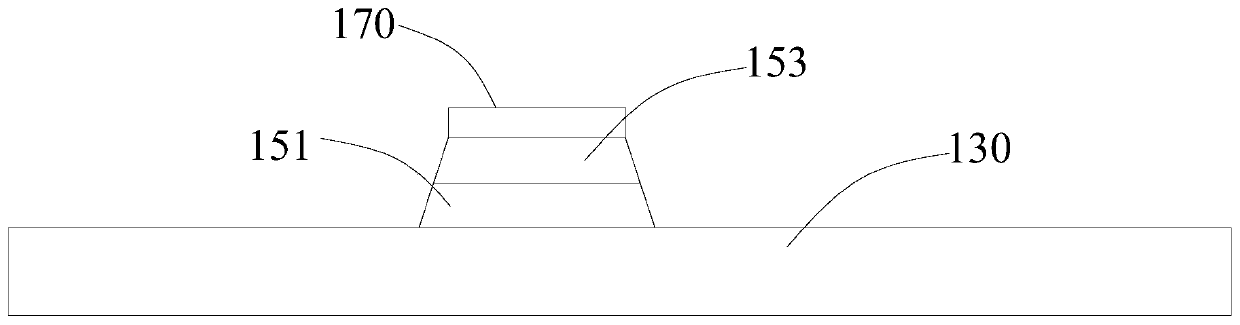

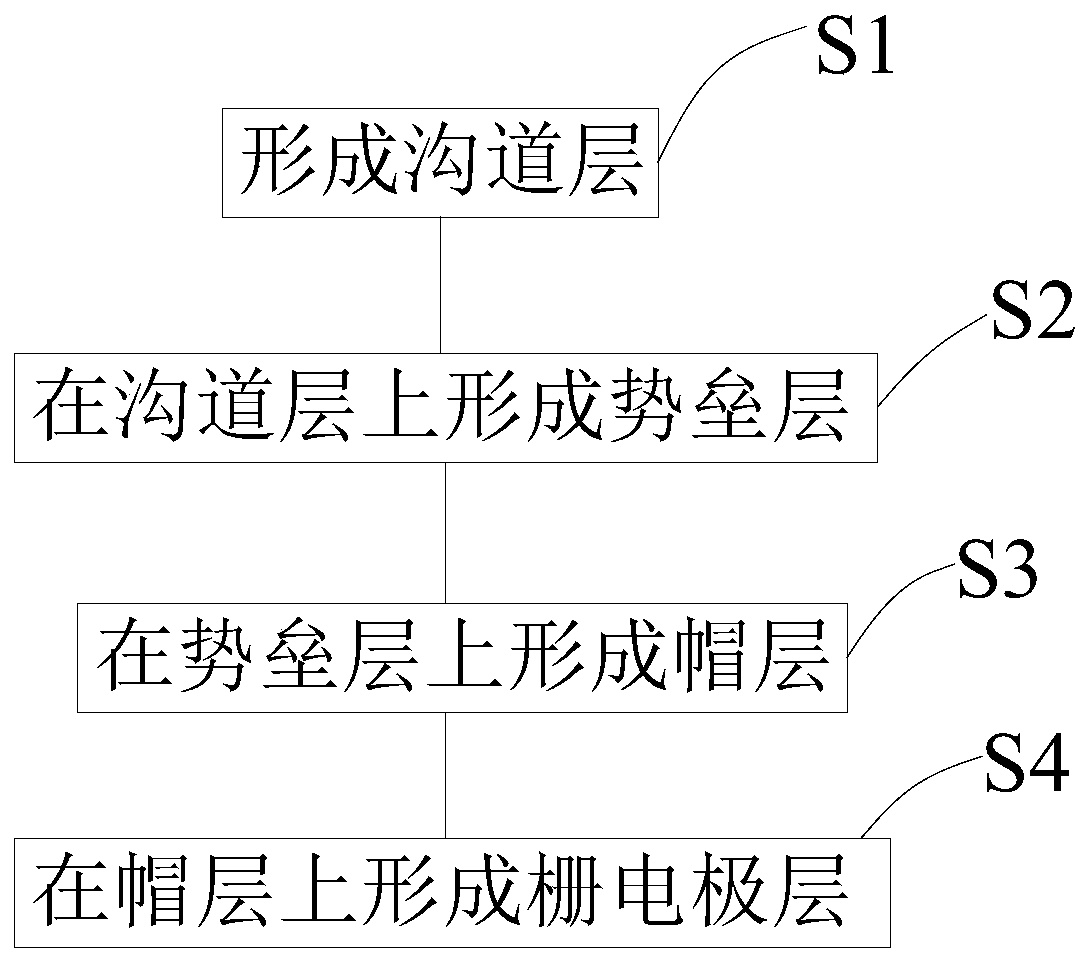

Gate structure, manufacturing method of gate structure, and enhanced semiconductor device

ActiveCN110429132AImprove uniformityGood repeatabilitySemiconductor/solid-state device manufacturingSemiconductor devicesEtchingFermi level

A gate structure, a manufacturing method of the gate structure, and an enhanced semiconductor device relate to the semiconductor technology field. The gate structure includes a channel layer, a barrier layer arranged on the channel layer, a cap layer arranged on the barrier layer, and a gate electrode layer arranged on the cap layer. The cap layer has a crystal polarization orientation which is opposite to the barrier layer. A cap layer material with an opposite polarity orientation of the barrier layer is used so that an interface between the barrier layer and the cap layer has extremely strong negatively polarized charges and a conduction band energy level is bent upwardly. The conduction band energy level of the barrier layer and the channel layer is raised above a Fermi level, a two-dimensional electron gas / two-dimensional cavity gas at the interface between the barrier layer and the channel layer can be effectively exhausted so as to increase a turn-on voltage. Simultaneously, different chemical properties of different crystal polarization orientations are used to realize self-termination wet etching of a gate pattern so as to increase uniformity and repeatability of device manufacturing.

Owner:GUANGDONG INST OF SEMICON IND TECH

Semiconductor element, semiconductor device, and power converter

ActiveUS8410489B2Increase the number ofIncrease ratingsEfficient power electronics conversionAc-dc conversionDevice materialBody region

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

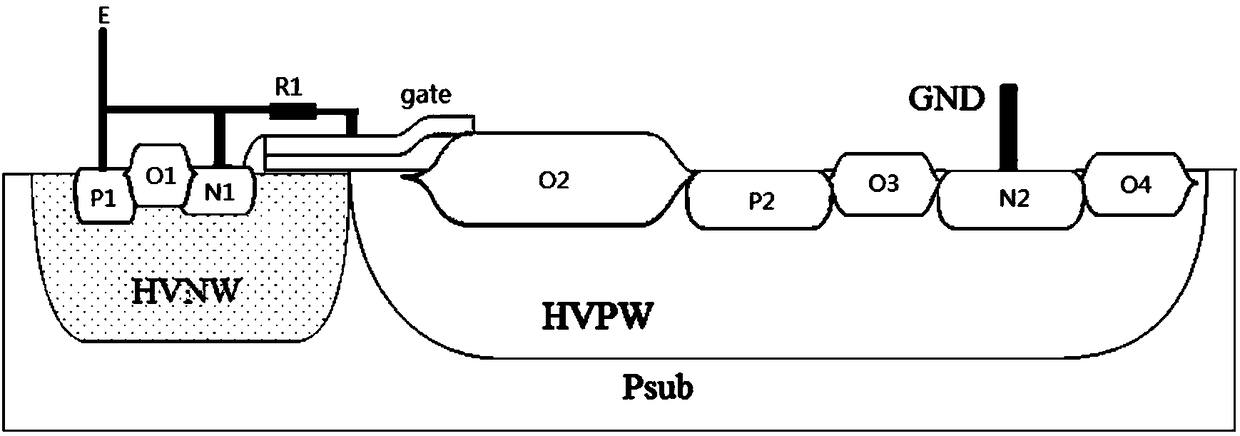

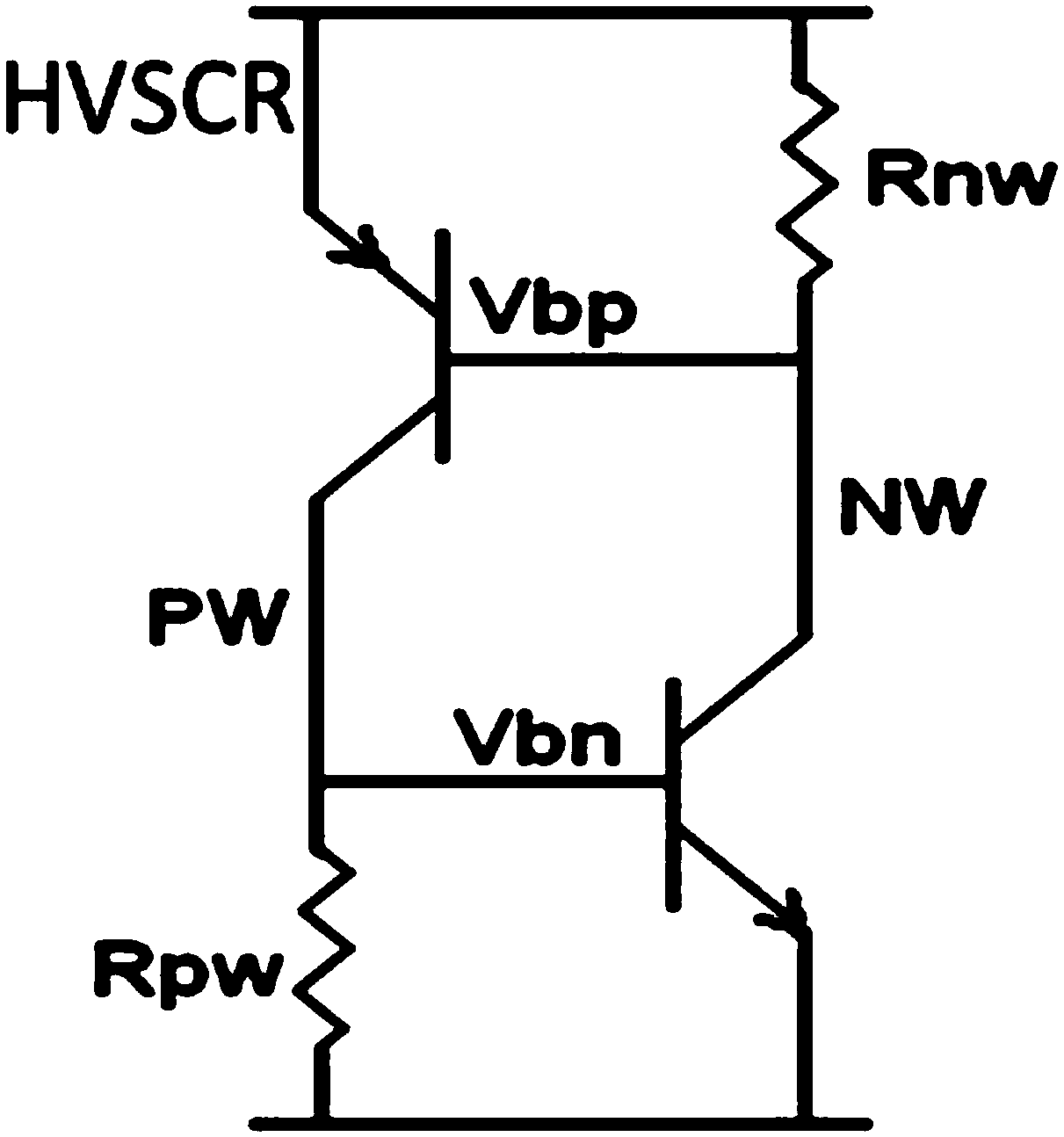

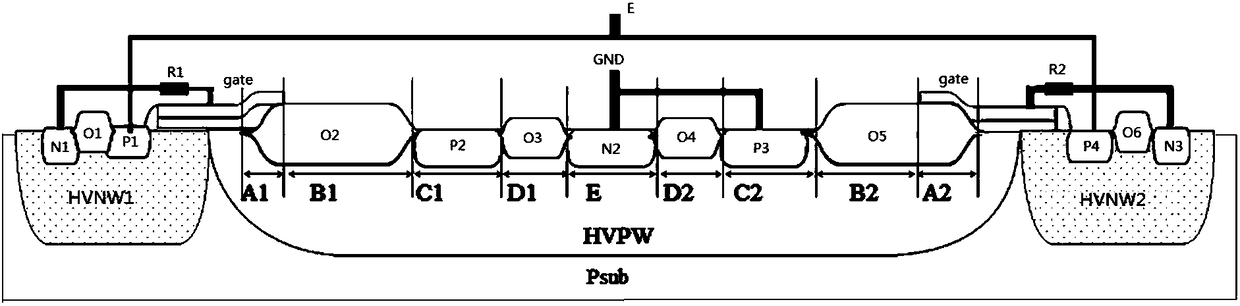

ESD (electrostatic discharge) device structure

ActiveCN108281420AIncrease RbIncrease widthTransistorSolid-state devicesSilicon-controlled rectifierLDMOS

The invention discloses an ESD (electrostatic discharge) device structure, comprising: a first P-LDMOS (P-type laterally diffused metal oxide semiconductor), a second P-LDMOS and a parasitic SCR (silicon controlled rectifier). The first P-LDMOS and the second P-LDMOS share a high-voltage P well (HVPW); an N+ AREA is arranged in the high-voltage P well (HVPW) between a drain of the first P-LDMOS and a drain of the second P-LDMOS to form the parasitic SCR; the first parasitic SCR and the second parasitic SCR have identical structure and are of bilateral asymmetric structure by centering on the N+ area. The ESD device structure has the advantages that ESD capacity of a device after being turned on can be improved, maintaining voltage and current can also be increased for the device, and latch-up risk of the ESD device is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

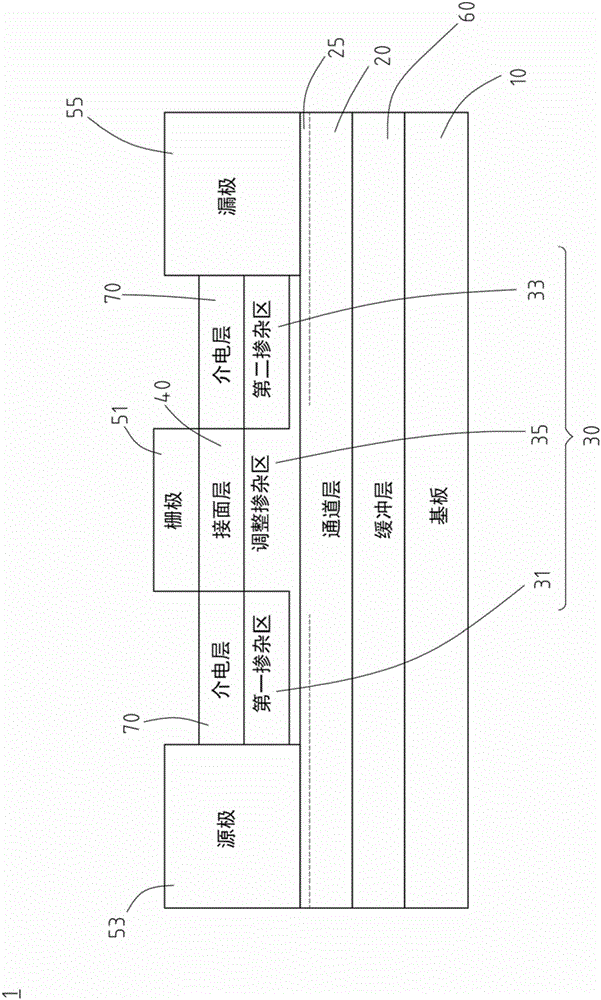

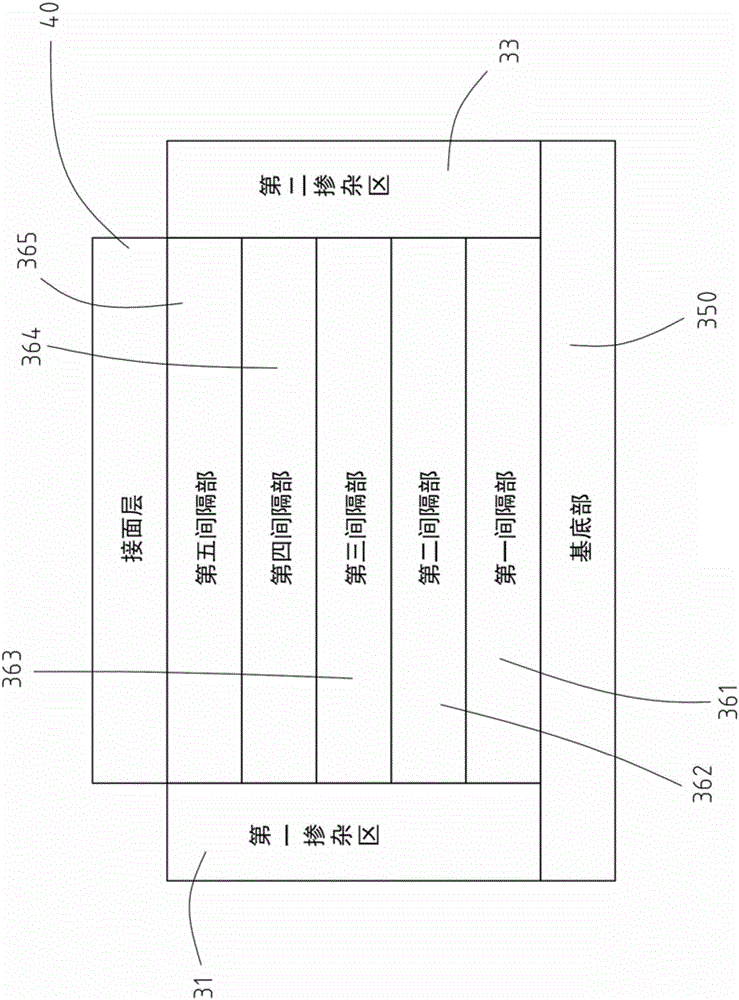

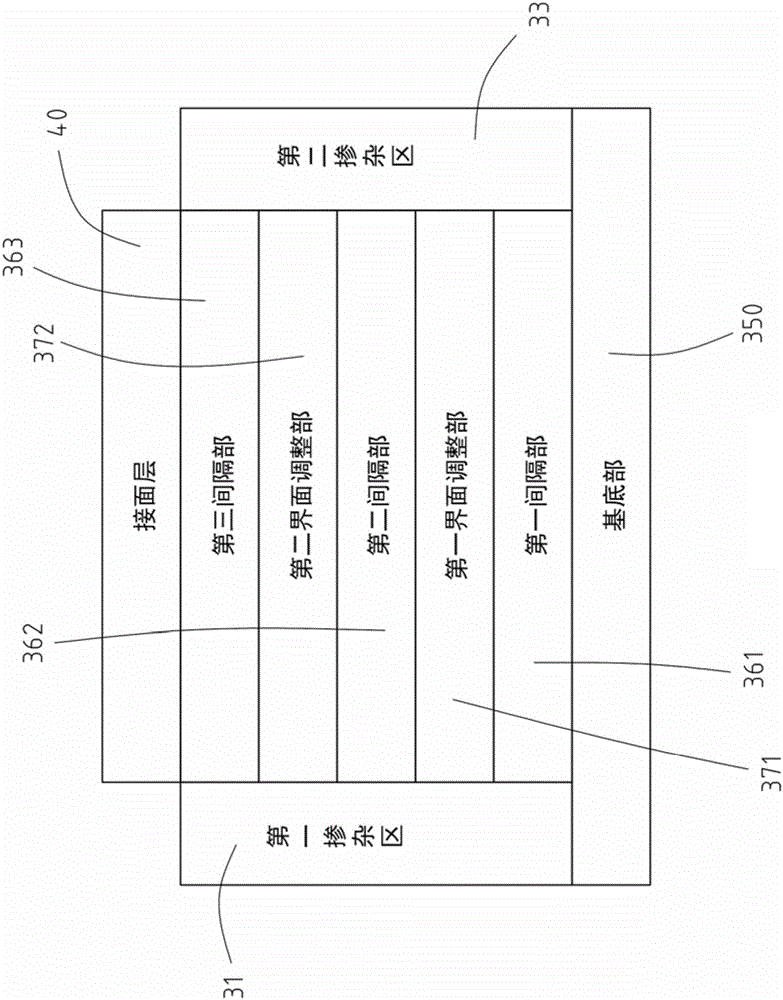

Enhancement-Mode High-Electron-Mobility Transistor Structure

ActiveCN106486544AReduce leakage currentImprove interface homogeneitySemiconductor devicesInterface layerSemiconductor

An enhancement-mode high-electron-mobility transistor structure comprises a channel layer, a barrier layer, an interface layer, a gate electrode, a source electrode and a drain electrode. The channel layer is a first III-V semiconductor and is arranged on a substrate. The barrier layer is a second III-V semiconductor and is arranged on the channel layer. The barrier layer comprises a first doped region, an adjusting doped region and a second doped region. The first doped region and the second doped region are n-type second III-V semiconductor, and the adjusting doped region comprises a p-type second III-V semiconductor. The first doped region and the second doped region are arranged at two sides of the adjusting doped region. The interface layer is arranged above the adjusting doped region and is a p-type third III-V semiconductor, and furthermore the doping amount is higher than that of the adjusting doped region. Furthermore the doping concentration of an area which is adjacent to the interface area in the adjusting doped region is higher than that of the area that is adjacent to the channel layer.

Owner:GLOBALWAFERS CO LTD

PN step of LED (Light Emitting Diode) chip, LED chip and manufacturing method of PN step

ActiveCN103413875AGood coverageIncrease the turn-on voltageSemiconductor devicesLeakage current reductionLight-emitting diode

The invention discloses a PN step of an LED (Light Emitting Diode) chip, the LED chip and a manufacturing method of the PN step. The LED chip comprises a substrate and an epitaxial layer which is formed on the substrate, wherein the epitaxial layer is provided with the PN step, the PN step is covered with an insulation passive film, the upper step surface of the PN step is a P type conducting layer, the lower step surface of the PN step is an N type conducting layer, and a PN step side surface is formed in a way that the upper step surface and the lower step surface are connected; the PN step side surface comprises a first connecting edge which is positioned on the upper step surface and a second connecting edge which is positioned on the lower step surface, the second connecting edge is positioned between the first connecting edge and the end part of the lower step surface, and the PN step side surface is a curved surface or an inclined surface. According to the PN step of the LED chip, the LED chip and the manufacturing method, which are disclosed by the invention, the covering effect of the insulation passive film on the LED chip is facilitated, the turn-on voltage of the LED chip is effectively increased, the leak current is reduced, and the luminous efficiency of the LED chip is effectively increased at the same time.

Owner:JUCAN PHOTOELECTRIC TECH (SUQIAN) CO LTD

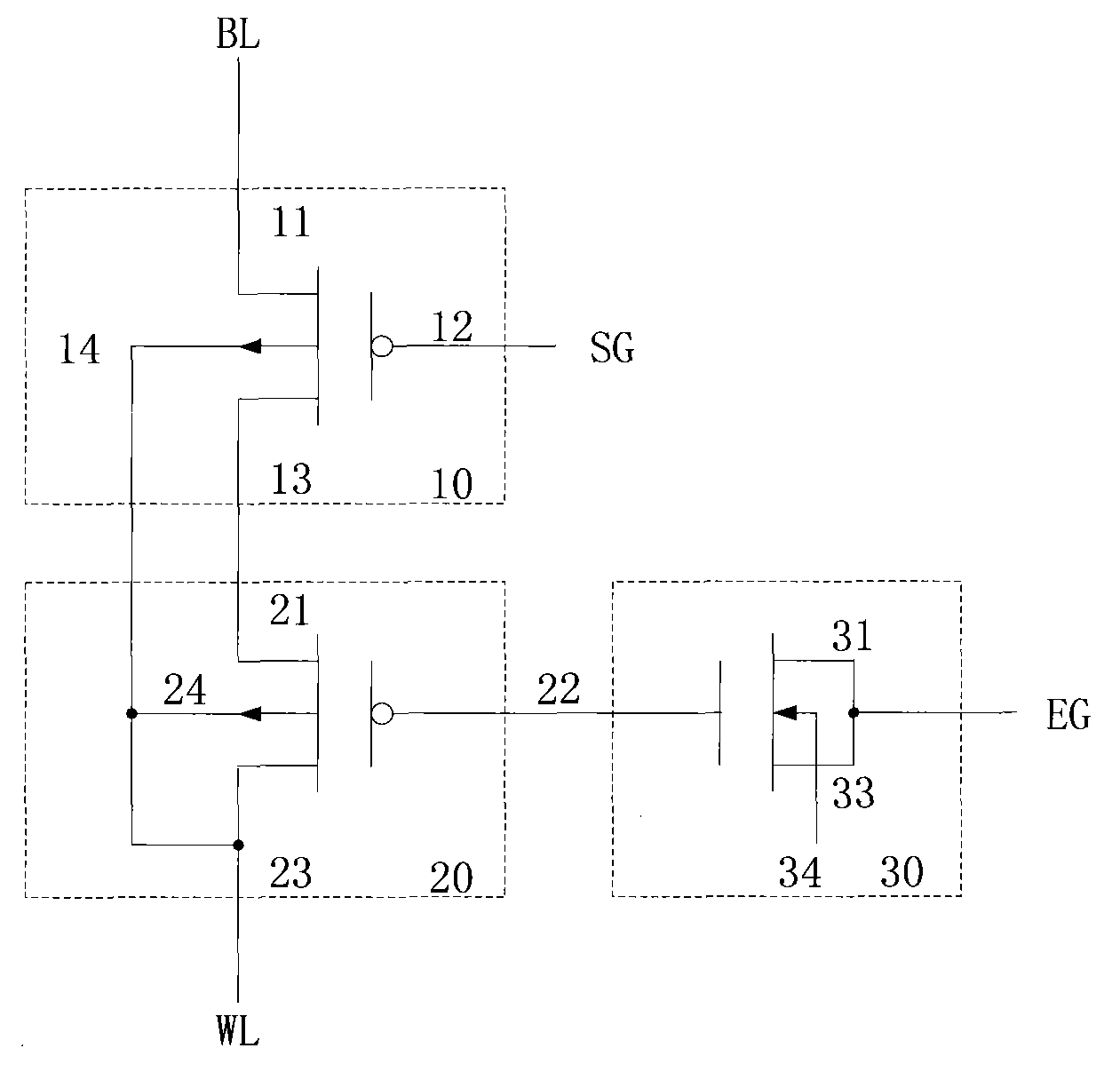

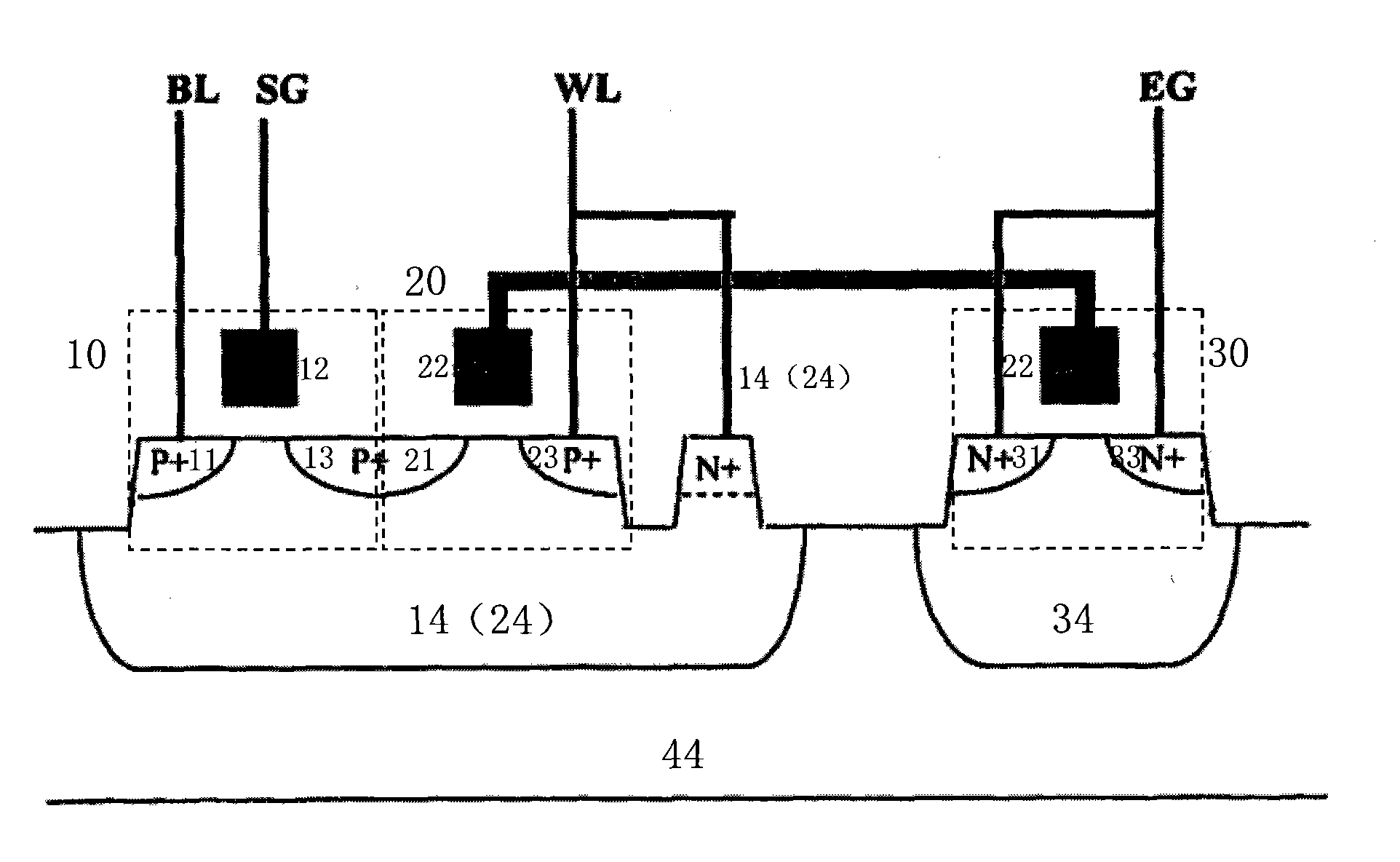

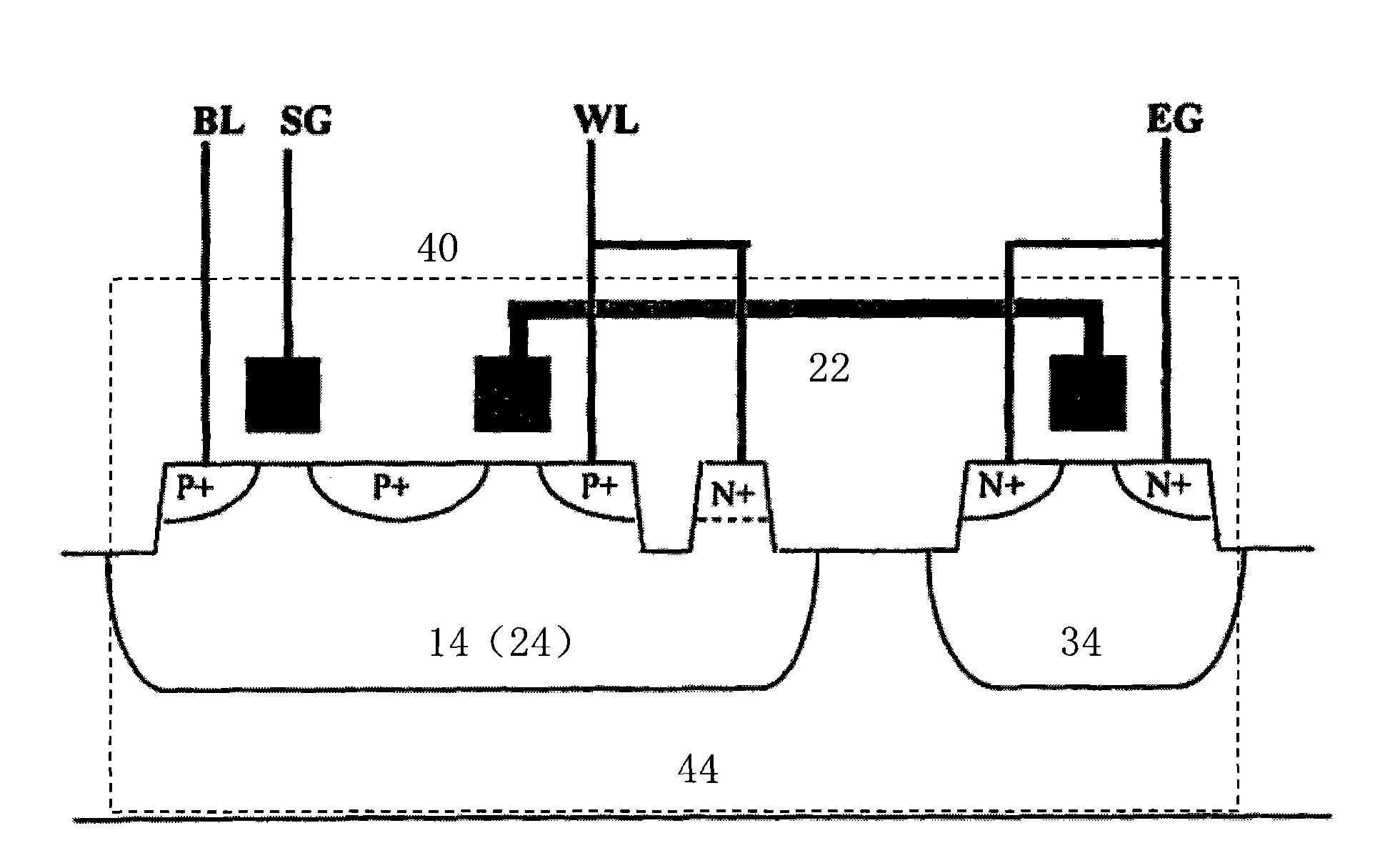

Unit structure of multi-time programmable (MTP) device

ActiveCN102063938AIncrease the doping concentrationIncrease the turn-on voltageSolid-state devicesRead-only memoriesUnit structureImpurity

The invention discloses a unit structure of a multi-time programmable (MTP) device. In the unit structure of the MTP device, an n well (24) is transversely isolated from an n well (34) through a p-type substrate (41) and a p well (42), and the p-type substrate (41) transversely contacts with the n well (34), so that larger breakdown voltage can be provided and an erase voltage is increased. The p well (42) is arranged between the n well (24) and the n well (34) and does not directly contact with the n well (34), so that the dosage concentration of p type impurities in a channel region of a parasitic metal oxide semiconductor (MOS) transistor is improved, a start voltage of the MOS transistor (40) is increased and the erase voltage is increased. According to the two factors, the maximum value of the erase voltage, which the unit structure of the MTP device can apply, is increased, so that higher erase speed and better erase effect can be achieved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

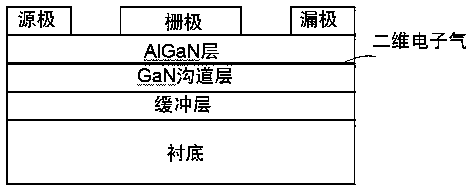

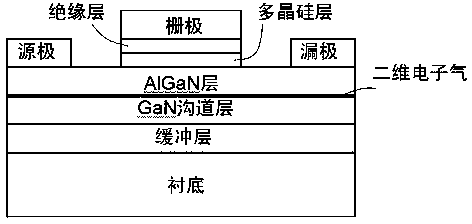

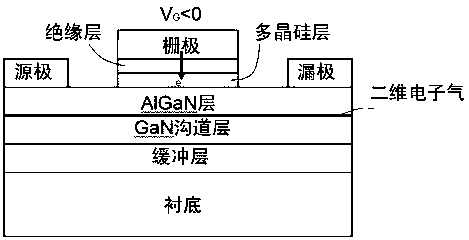

Gallium nitride power field effect transistor

InactiveCN103390643AIncrease the turn-on voltageImprove switching performanceSemiconductor devicesField-effect transistorGallium nitride

The invention discloses a gallium nitride power field effect transistor which comprises a substrate, a buffering layer, a GaN channel layer arranged on the buffering layer in an epitaxial mode, an AlGaN layer extended on the GaN, a source electrode, a drain electrode, a grid electrode, a polycrystalline silicon layer and an insulating layer, wherein the polycrystalline silicon layer and the insulating layer are arranged between the grid electrode and the AlGaN. When the voltage of the grid electrode is negative, electrons of a grid electrode metal layer are tunneled to the polycrystalline silicon layer, the threshold voltage of the GaN field effect transistor is increased, therefore, the switching performance of the GaN field effect transistor is improved, and the power consumption of the transistor is reduced.

Owner:无锡派腾微纳米科技有限公司

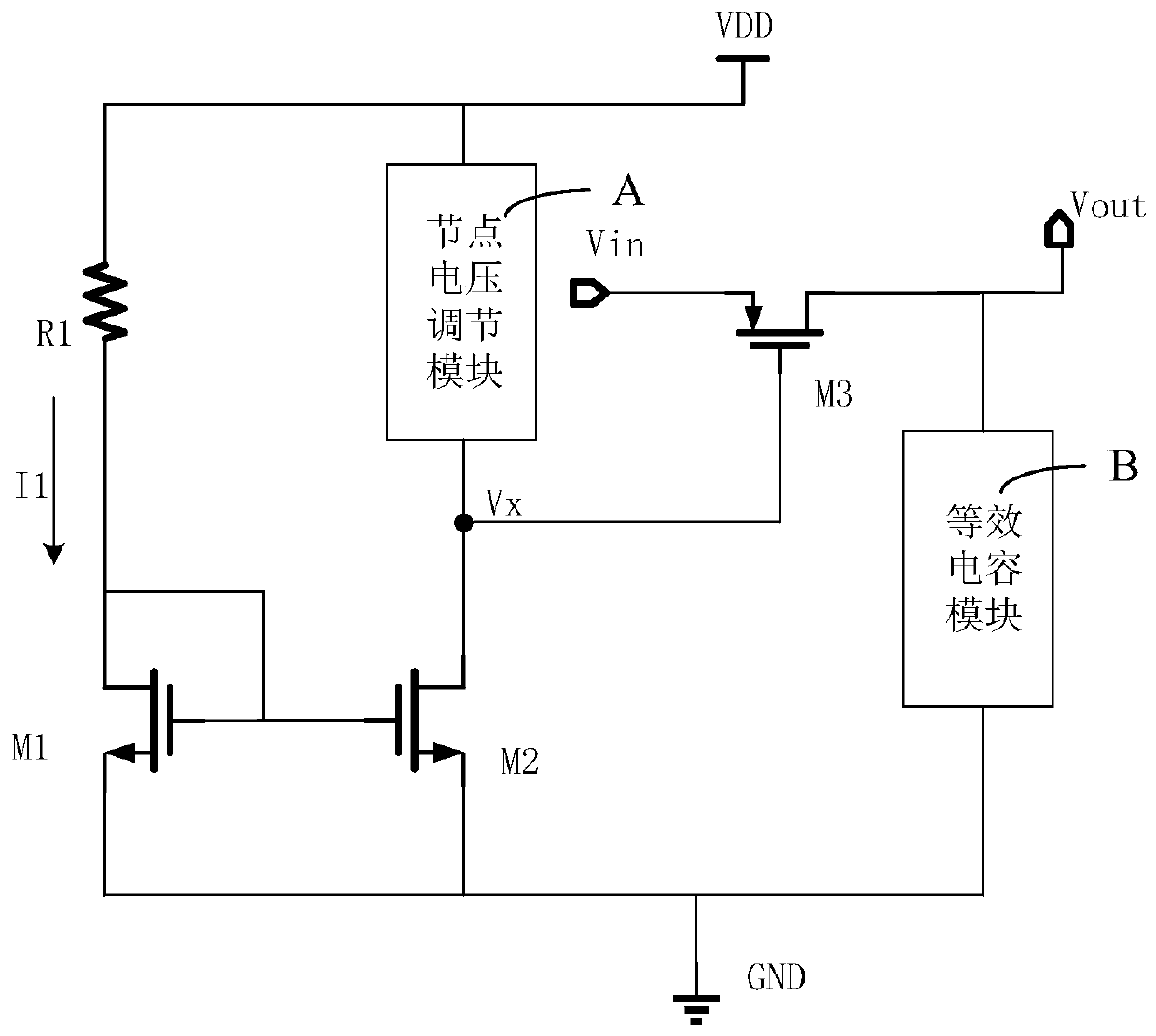

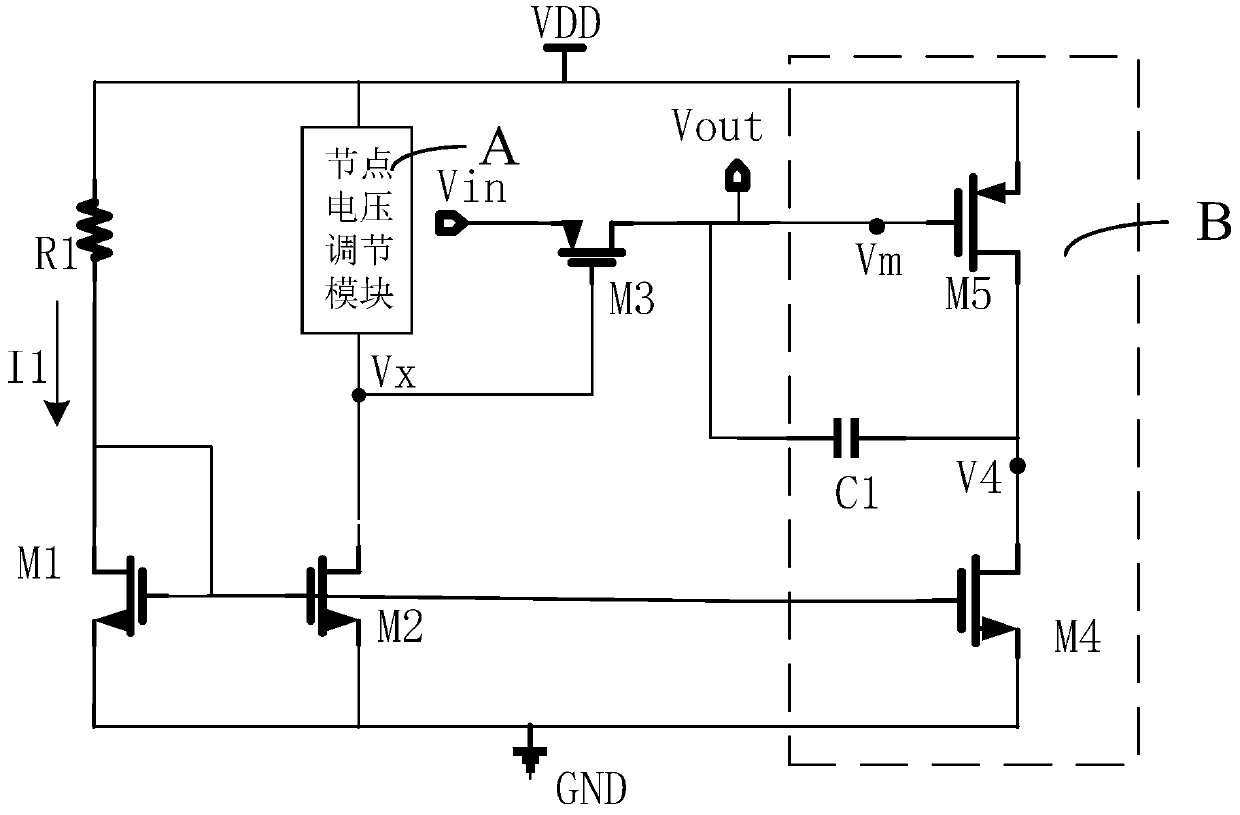

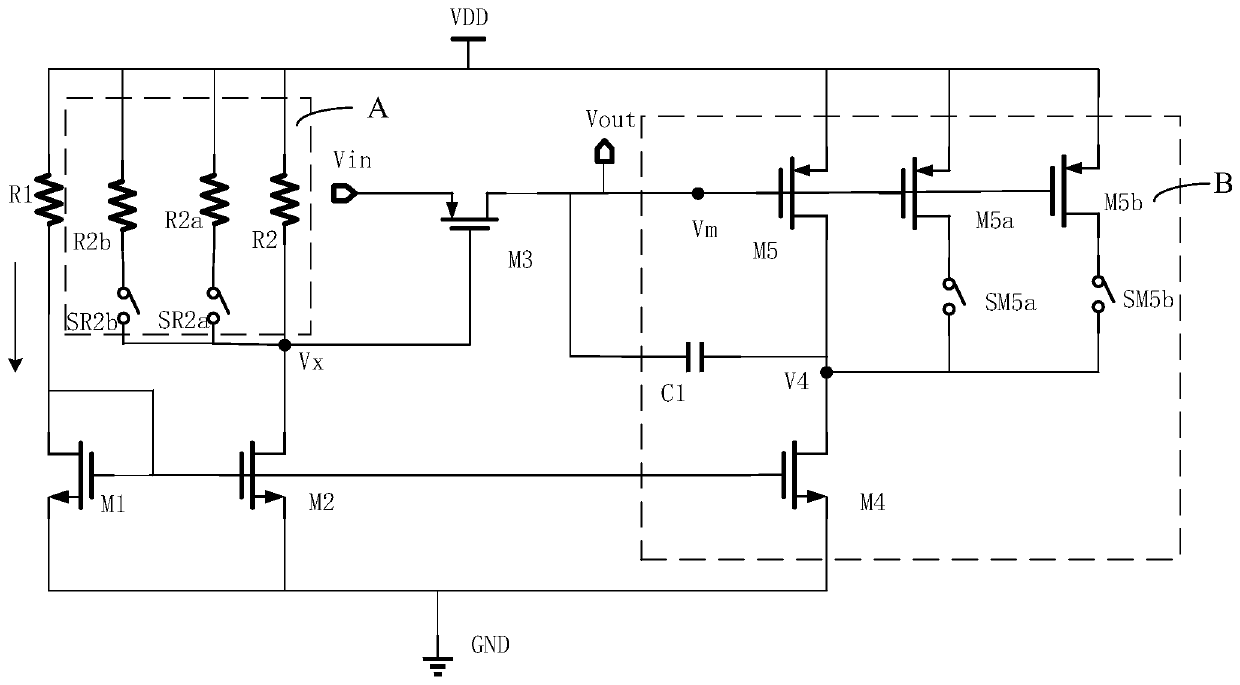

Low-pass filter circuit, low-pass filter, and CMOS chip

PendingCN110311650AIncrease -3dB frequencyIncrease the turn-on voltageFrequency selective two-port networksHarmonic reduction arrangementIntegrated circuitHigh-pass filter

The invention relates to a low-pass filter circuit, a low-pass filter and a CMOS chip. The low-pass filter circuit comprises a first resistor, a first switch tube, a second switch tube, a node voltageadjusting module A, a third switch tube and an equivalent capacitor module B; bias current is generated through the first resistor and the first switching tube; a current mirror structure is formed by the first switch tube and the second switch tube, and the current flowing through the second switch tube is equal to the bias current. The node voltage adjusting module A adjusts the node voltage between the input end of the second switch tube and the control end of the third switch tube, so that the conduction voltage of the third switch tube is increased, large resistance is formed, and the-3dB frequency of the low-pass filter circuit can be effectively increased.. Devices in the low-pass filter circuit can be directly made on an integrated circuit, and low-cost mass production is facilitated.

Owner:HUNAN GOKE MICROELECTRONICS

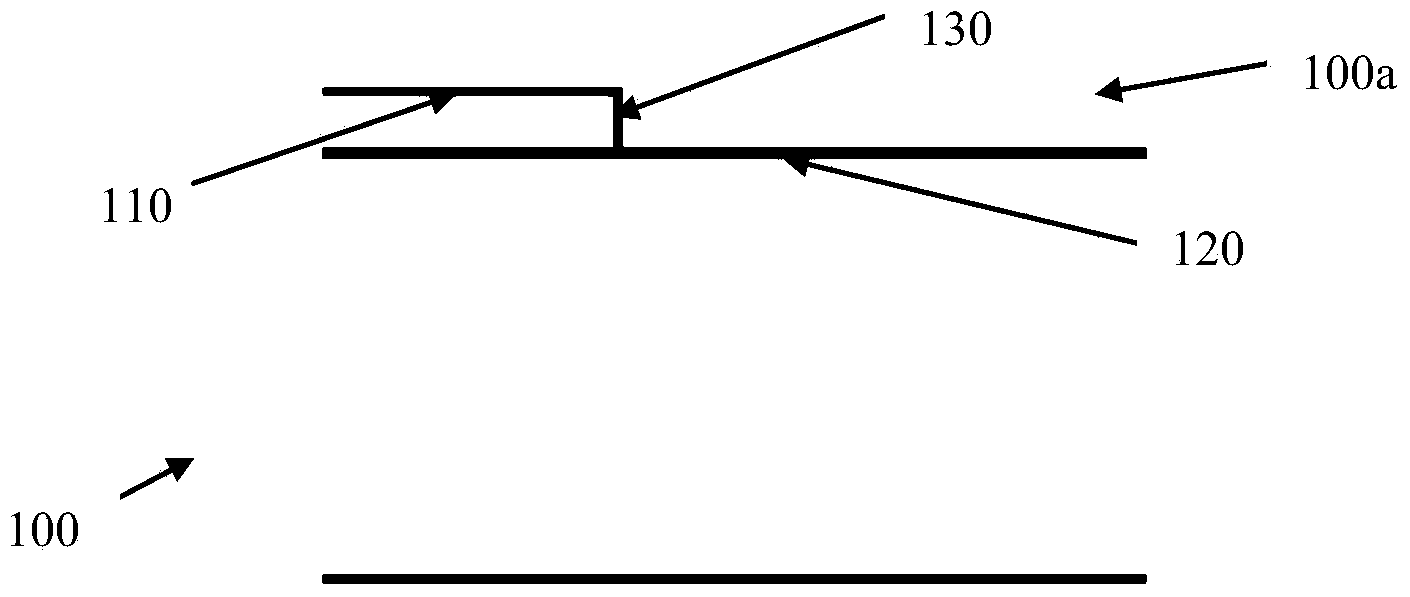

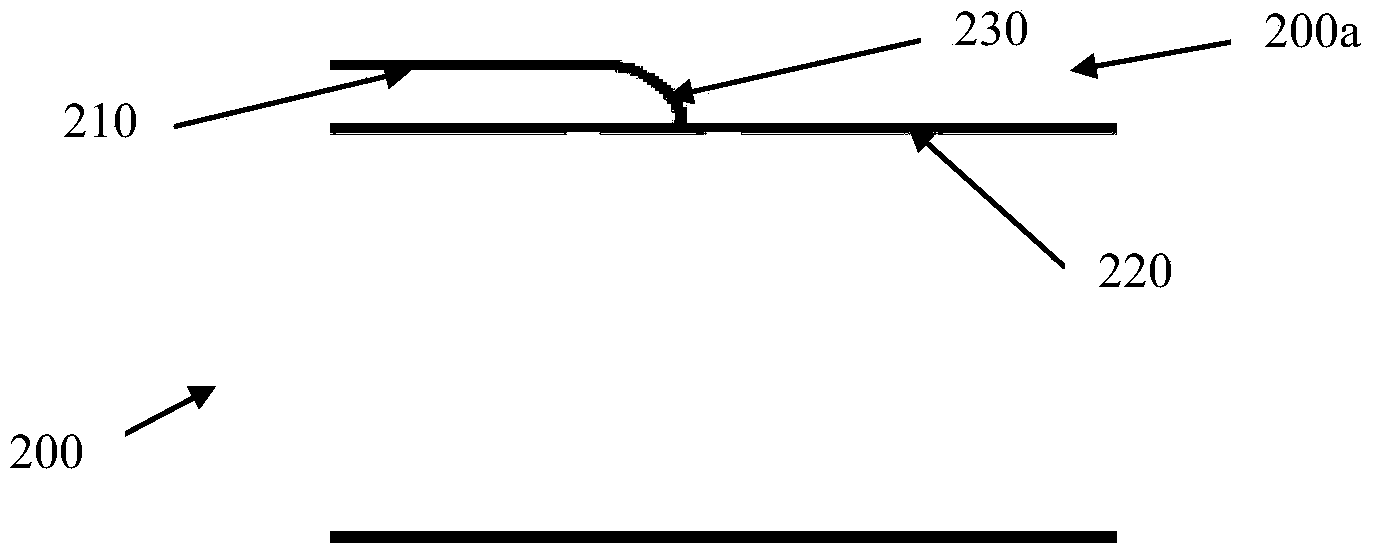

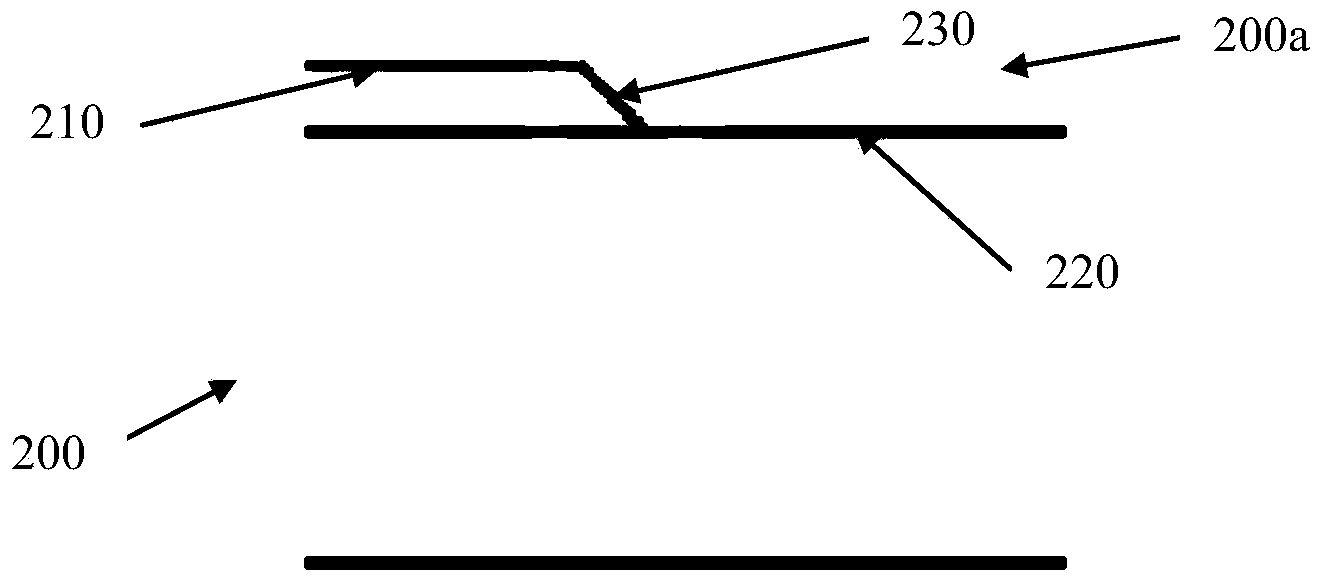

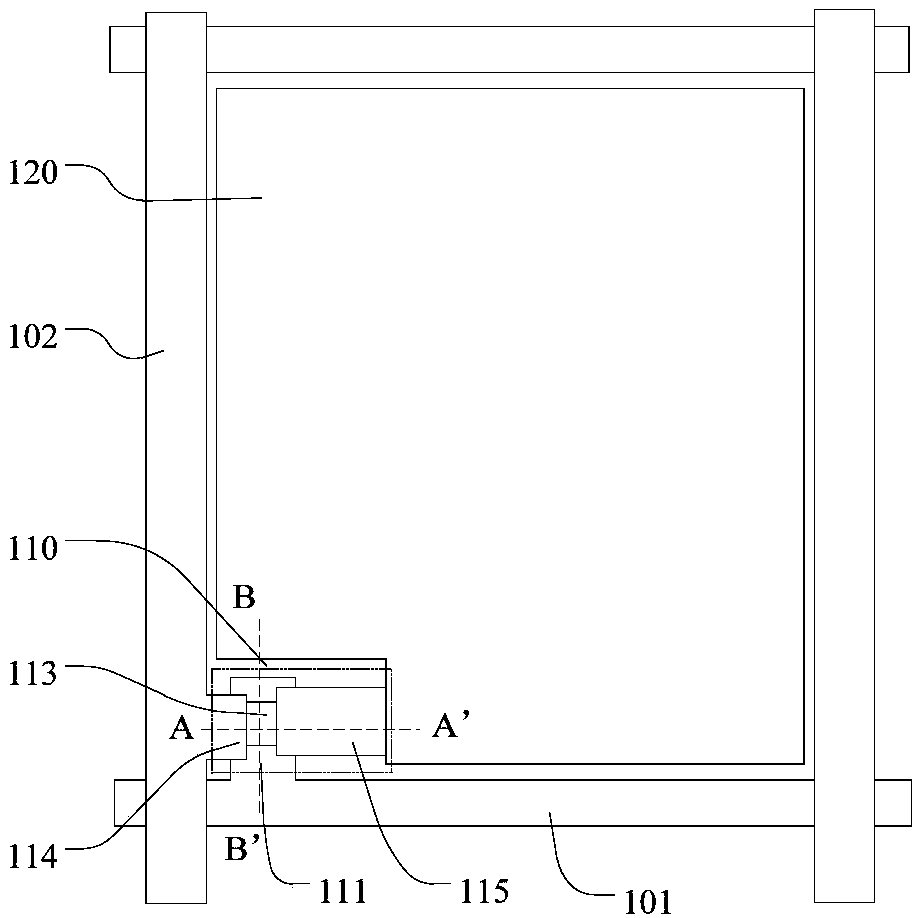

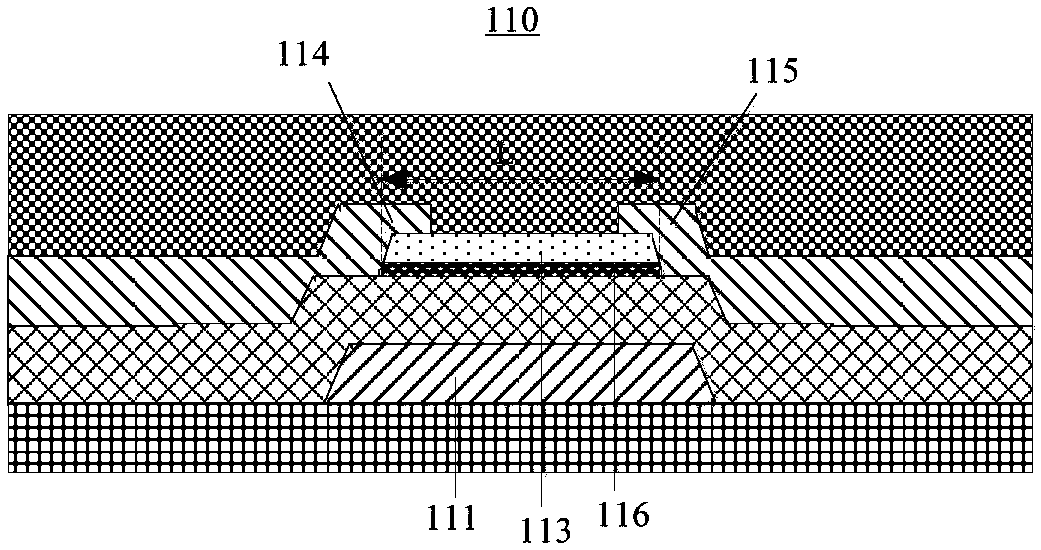

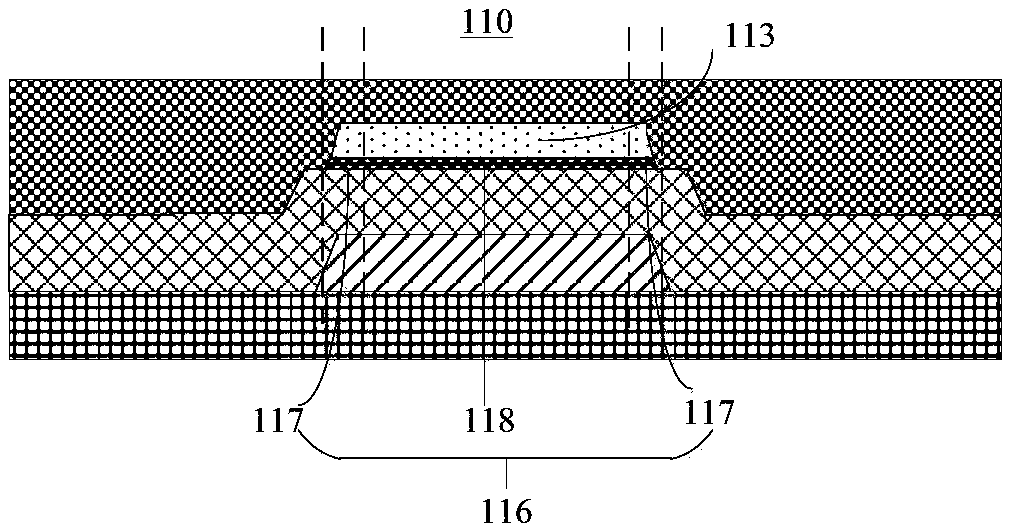

Thin film transistor and manufacturing method thereof and electronic device

ActiveCN109509793AImprove hump effectImprove performanceTransistorSolid-state devicesActive layerElectron

A thin film transistor and a manufacturing method thereof and an electronic device are provided. The thin film transistor comprises a substrate, and a gate, a gate insulating layer, an active layer, asource and a drain which are arranged on the substrate. The active layer comprises a channel region located between the source and the drain. The channel region consists of an edge region along the length direction of a channel and a main region outside the edge region. The thin film transistor further comprises an auxiliary layer located between the gate and the active layer. The auxiliary layeroverlaps at least partially with the projection of the edge region of the channel region on the substrate, and is used to increase the turn-on voltage of the edge region of the channel region.

Owner:BOE TECH GRP CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com