Storage unit circuit with adaptive leakage current cutoff mechanism

A memory cell circuit, leakage current technology, applied in information storage, static memory, digital memory information and other directions, can solve the problems of increased static energy consumption of memory banks, reduced product life and reliability, etc., to reduce leakage power consumption, The effect of low power consumption and high robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

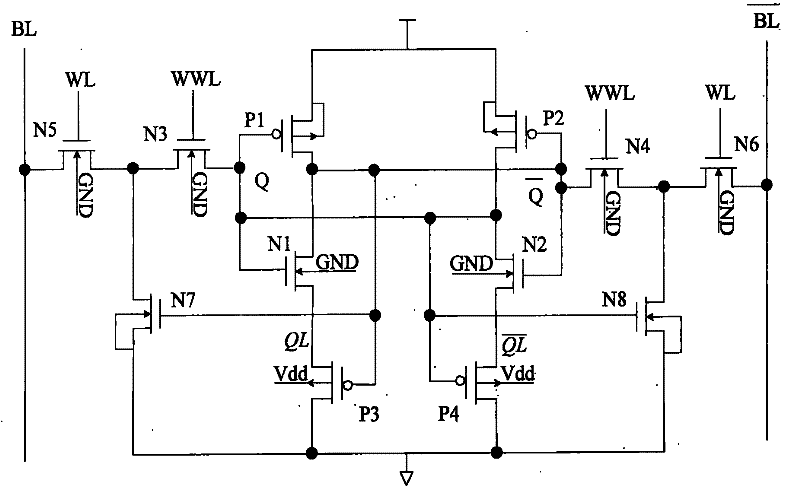

[0027] see figure 1 , the memory unit circuit with low power consumption and high robustness of the present invention with adaptive leakage current cut-off mechanism is composed of twelve transistors: four PMOS transistors P1, P2, P3, P4 and eight NMOS transistors N1~N8 , the transistor constitutes a double-terminal read-write sub-threshold memory cell circuit, and the memory cell circuit is connected between the bit line BL and the bit line between.

[0028] Among them, the body terminals of the four PMOS transistors are connected to the power supply voltage Vdd, and the body terminals of the eight NMOS transistors are grounded; the drain terminal and the gate terminal of the NMOS transistor N1 are respectively connected with the drain terminal and the gate terminal of the PMOS transistor P1, forming the first An inverter; the drain terminal and the gate terminal of the NMOS transistor N2 are respectively connected with the drain terminal and the gate terminal of the PMOS t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More