Complementary Metal Oxide Semiconductor Transistor Fabrication Method

A technology of oxide semiconductors and complementary metals, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of increased overlap capacitance, inconsistency, reduced transistor switching speed and transient characteristics, etc., to achieve overlap The effect of reducing capacitance, reducing process cost and improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

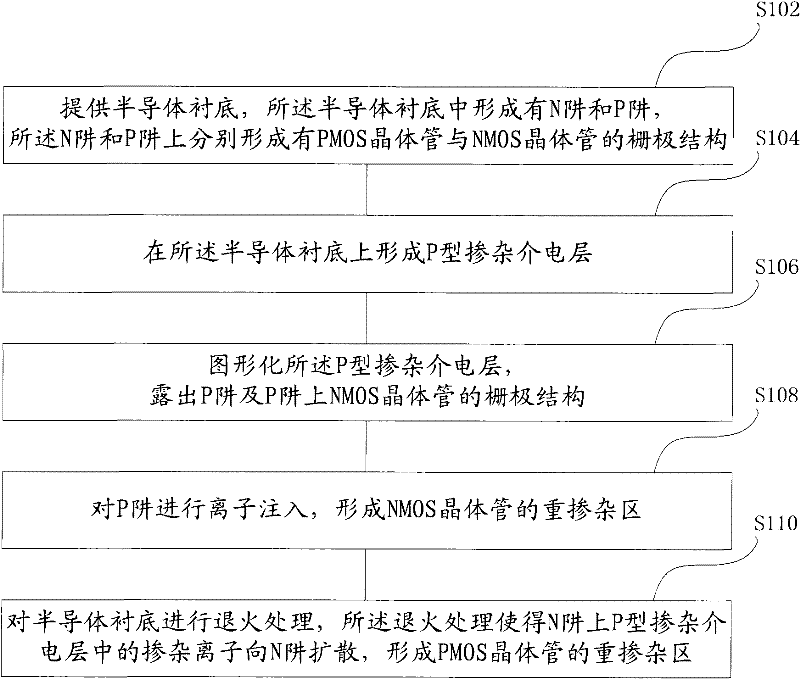

Method used

Image

Examples

Embodiment Construction

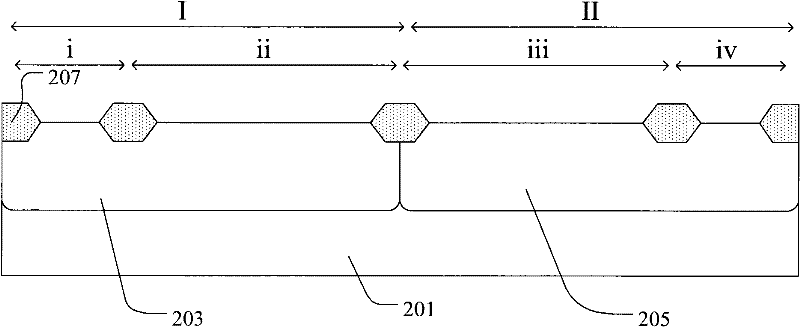

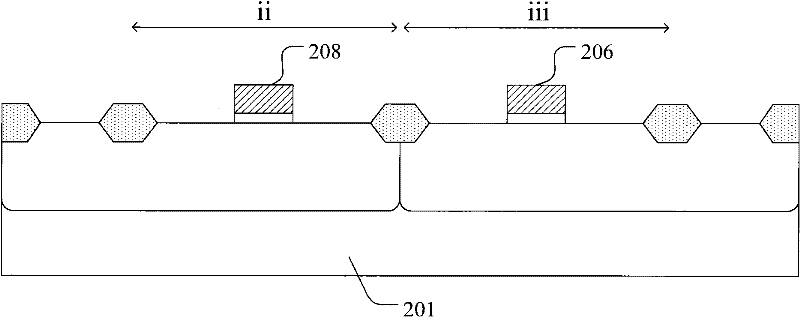

[0023] In the CMOS transistor manufacturing process of the prior art, the P-type heavily doped region of the PMOS transistor is formed by ion implantation, and the doping ions in the P-type heavily doped region in the PMOS transistor are usually boron ions, and the boron ions are formed on the semiconductor substrate. The diffusion speed in the bottom is fast; in the prior art, annealing treatment is required after the implantation of the heavily doped region is completed, and in the annealing treatment, the boron ions in the P-type heavily doped region will Diffusion continues above, that is, secondary diffusion occurs. The secondary diffusion of boron ions causes the doping curve of the P-type heavily doped region to deviate from the original doping curve after ion implantation. In particular, after the secondary diffusion, the P The doping curve of the N-type heavily doped region does not match the doping curve of the N-type heavily doped region, and the mismatched doping cu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More