Electrostatic-proof protection circuit

A protection circuit, anti-static technology, applied in emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, circuit devices, etc., can solve problems such as distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

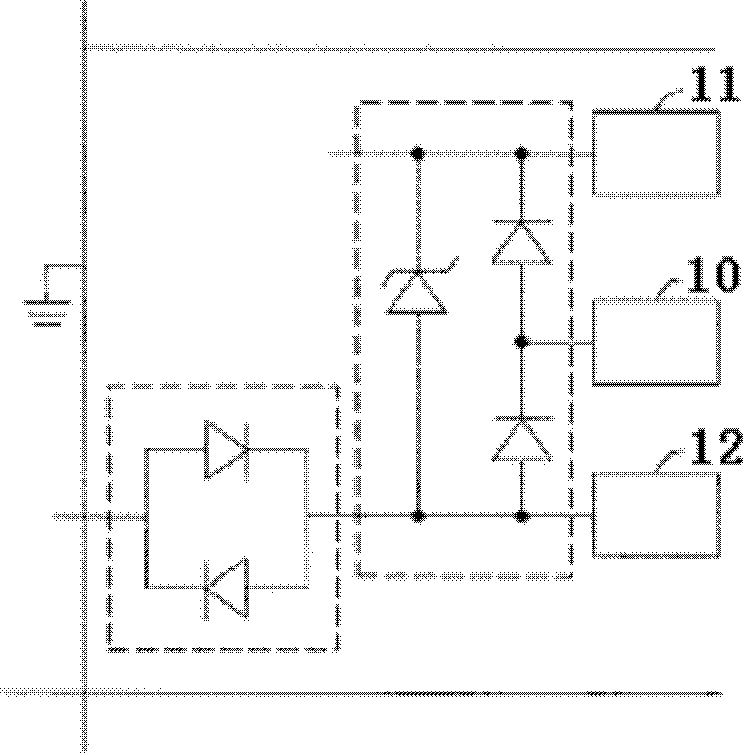

[0048] see Figure 4A to Figure 4C , which is a circuit diagram showing the first embodiment of the antistatic protection circuit of the present invention. As shown in the figure, the anti-static protection circuit of the present invention includes a first diode D1, a second diode D2, a first PMOS transistor M1, and a first PMOS transistor M2. components are described in detail.

[0049] The anode of the first diode D1 is connected to the ground terminal VSS, its cathode is connected to the cathode of the second diode D2, and a first tap point a is formed at the connection, and the anode of the second diode D2 is connected to the signal Source VIN.

[0050] The first PMOS transistor M1 has a source s1, a gate g1, a drain d1 and a substrate, the substrate is connected to the source s1 and then connected to the first tap point a, and the gate g1 is connected to the first tap point a through a capacitor C1. The signal source VIN is connected, and its gate g1 is also connected ...

no. 2 example

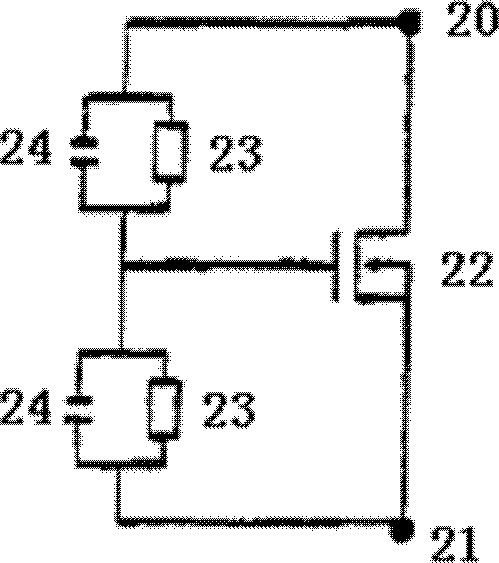

[0059] see figure 2 , is to show the circuit diagram of the second embodiment of the antistatic protection circuit of the present invention, wherein, with the antistatic protection circuit of the foregoing embodiment (such as Figures 4A to 4C Shown) the same or similar components are represented by the same or similar symbols, and detailed descriptions are omitted to make the description of this case clearer and easier to understand.

[0060] The biggest difference between the anti-static protection circuit of the second embodiment and the anti-static protection circuit of the first embodiment is that the anti-static protection circuit of the first embodiment uses the ground terminal VSS as the static discharge point of the signal source VIN; The anti-static protection circuit of the second embodiment uses the power supply terminal VDD' as the electrostatic discharge point of the signal source VIN'. In addition, because the static discharge point is selected differently, in ...

no. 3 example

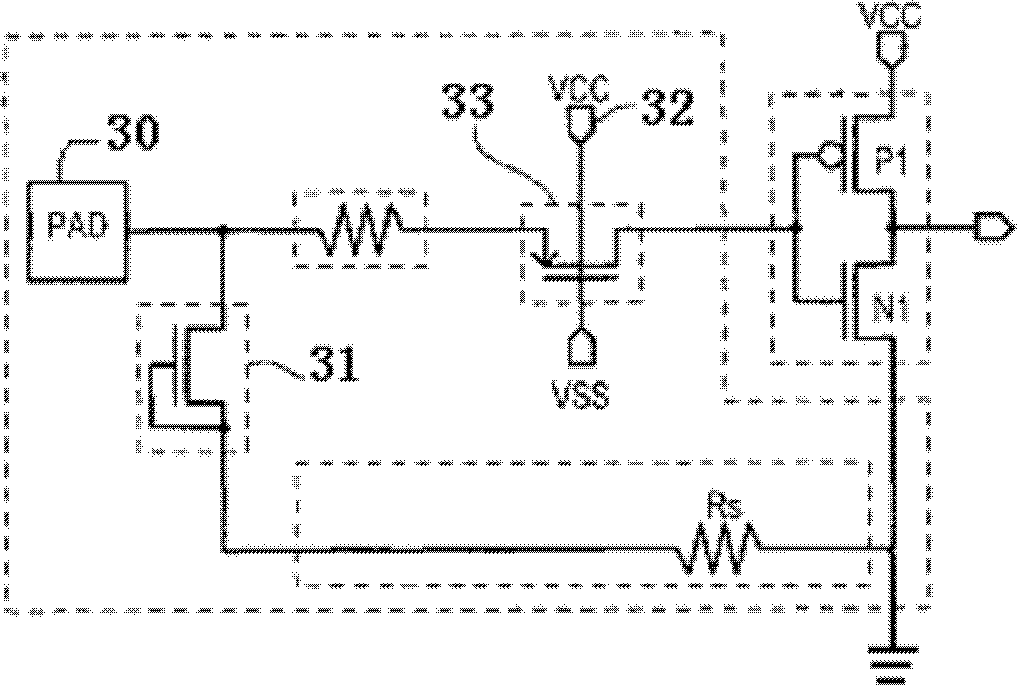

[0068] see Figure 6 , is to show the circuit diagram of the third embodiment of the antistatic protection circuit of the present invention, wherein, with the antistatic protection circuit of the foregoing embodiment (such as Figures 4A-4C as well as Figures 5A-5C Shown) the same or similar components are represented by the same or similar symbols, and detailed descriptions are omitted to make the description of this case clearer and easier to understand.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More