Optimization method of low-power-consumption circuit design

A technology of circuit design and optimization method, applied in computing, electrical digital data processing, instruments, etc., can solve problems such as constraints and increased chip power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

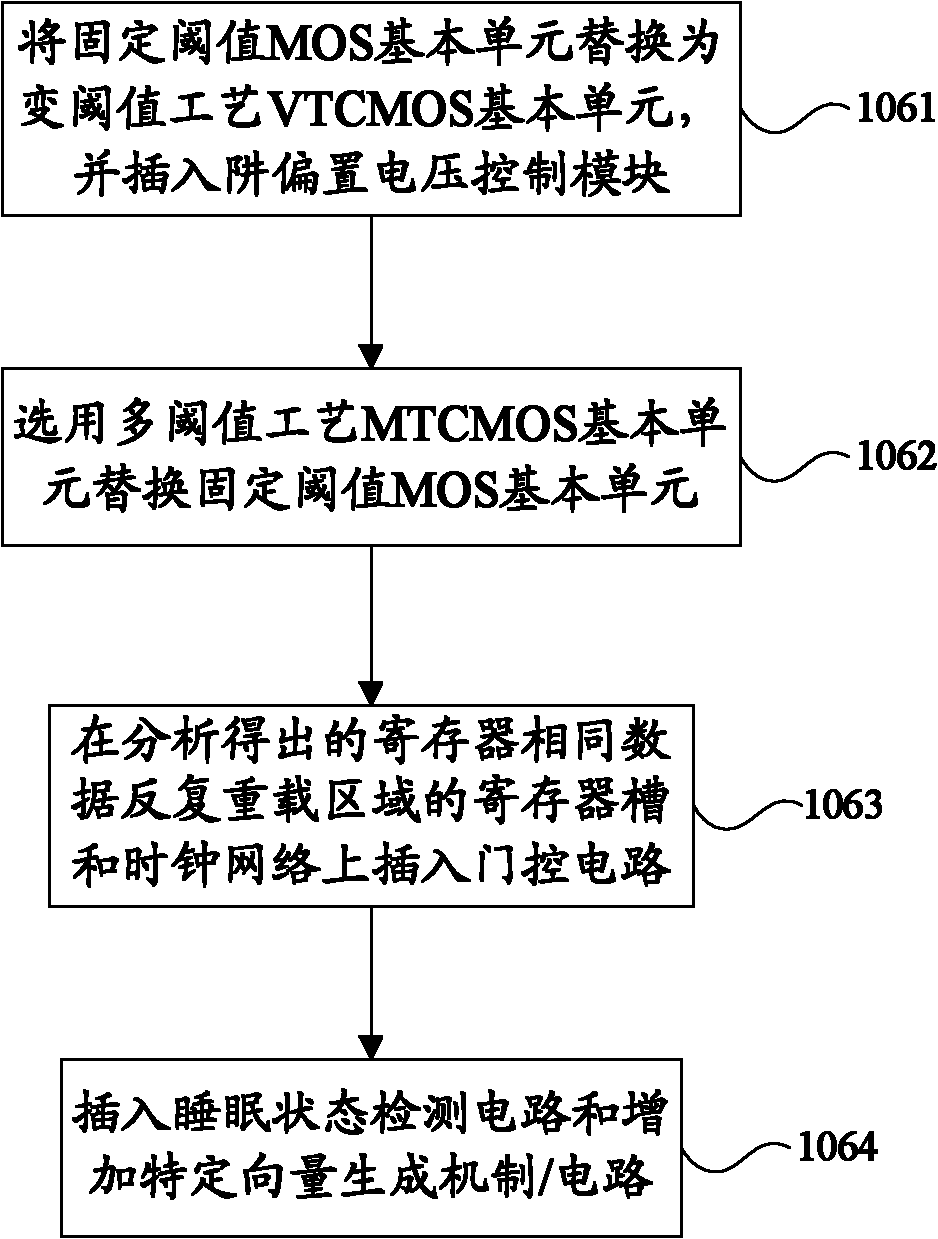

[0012] The present invention aims at optimizing the gate-level circuit netlist design, inserting and / or replacing some units in the circuit netlist to support MTCMOS, VTCMOS, power gating, multi-voltage, and dynamic voltage and frequency scaling (DVFS), power gating Low power consumption technology such as chip system makes the power consumption of the chip system the lowest under the premise of ensuring the circuit performance of the chip system.

[0013] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

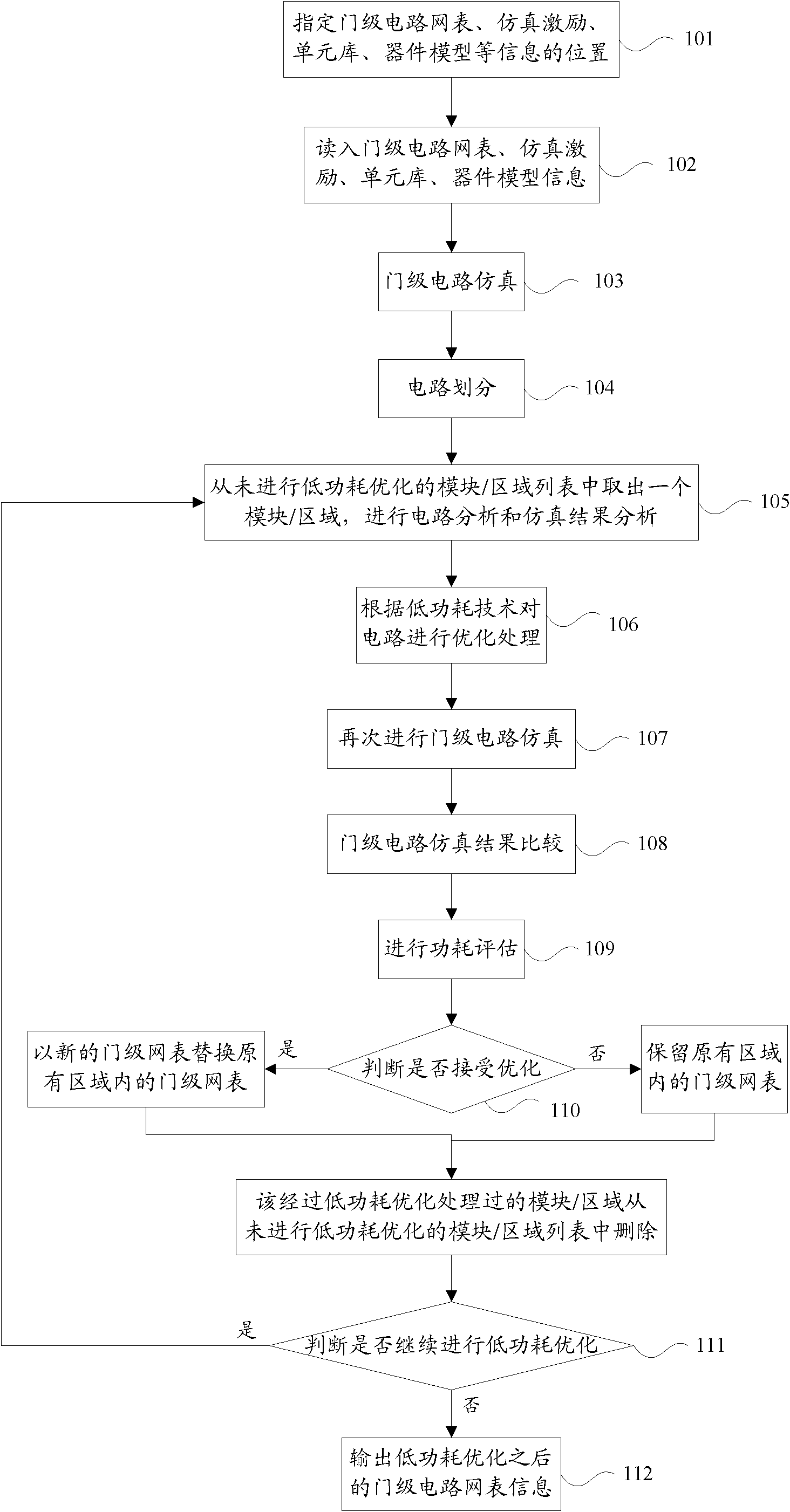

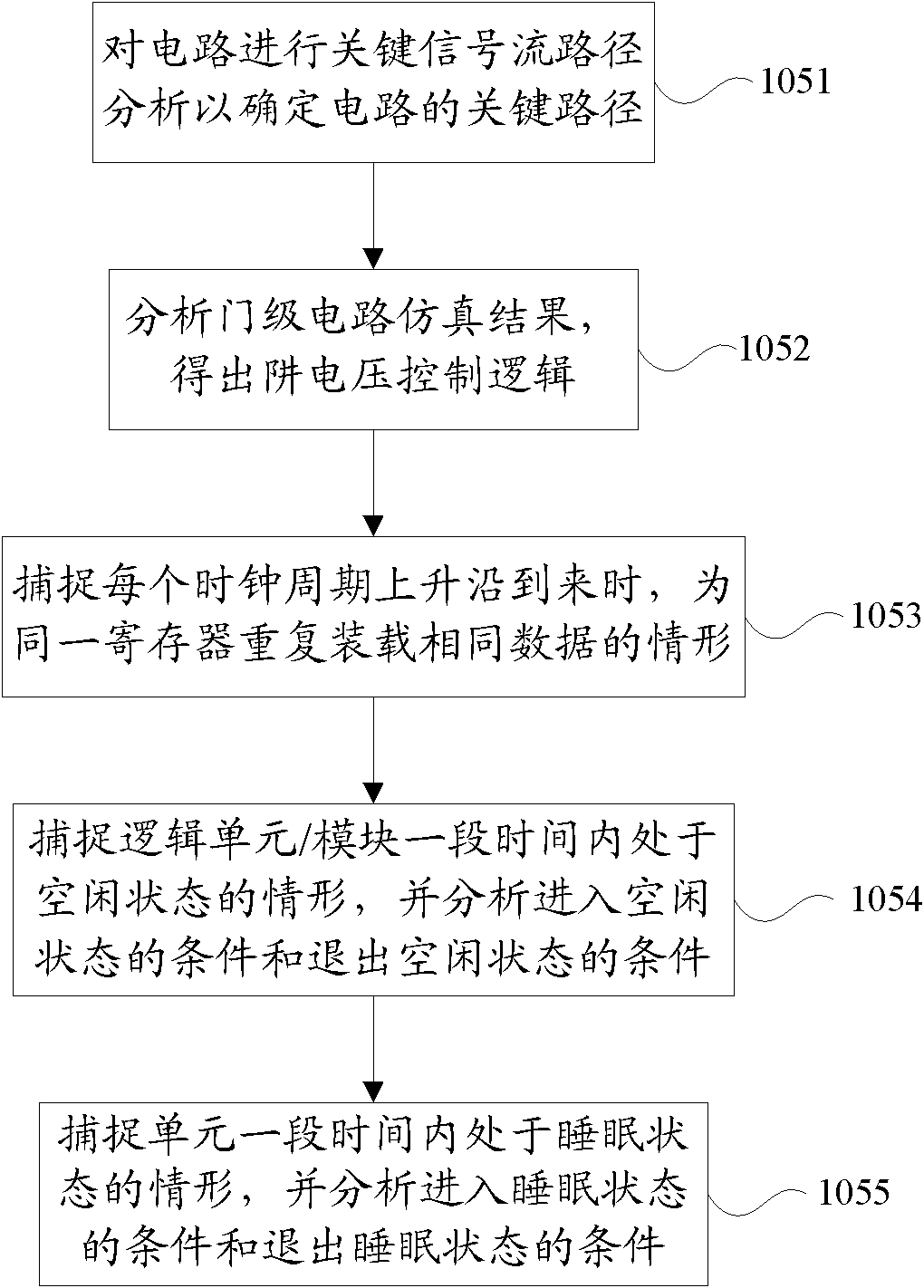

[0014] figure 1 A flow chart of a method for optimizing a low-power circuit design provided by an embodiment of the present invention specifically includes the following steps:

[0015] Step 101, designate the location of gate-level circuit netlist, simulation stimulus, cell library, device model and other information...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More