Anti-NBTI (Negative-Bias Temperature Instability) effect reinforcing method based on CMOS (Complementary Metal-Oxide-Semiconductor Transistor) digital logic gate circuit

A digital logic and gate circuit technology, applied in logic circuits, electrical components, reliability improvement and modification, etc., can solve problems such as degradation effects, and achieve the effect of reducing increment and threshold voltage drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The specific implementation of the present invention will be further described below in conjunction with the accompanying drawings and examples, but the implementation and protection scope of the present invention are not limited thereto.

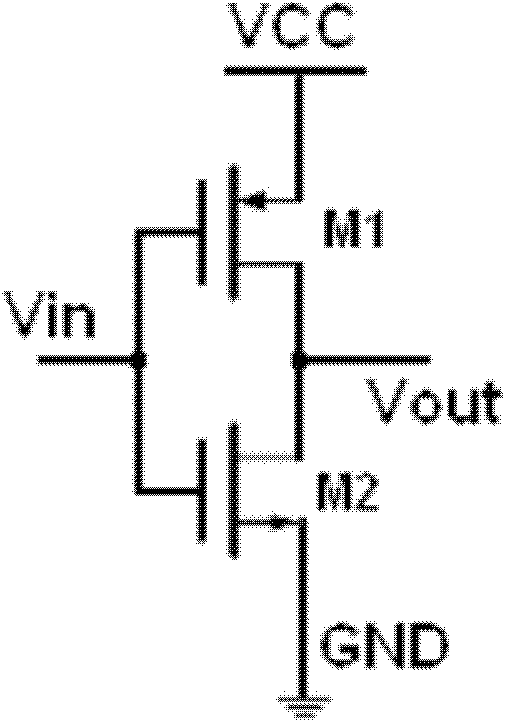

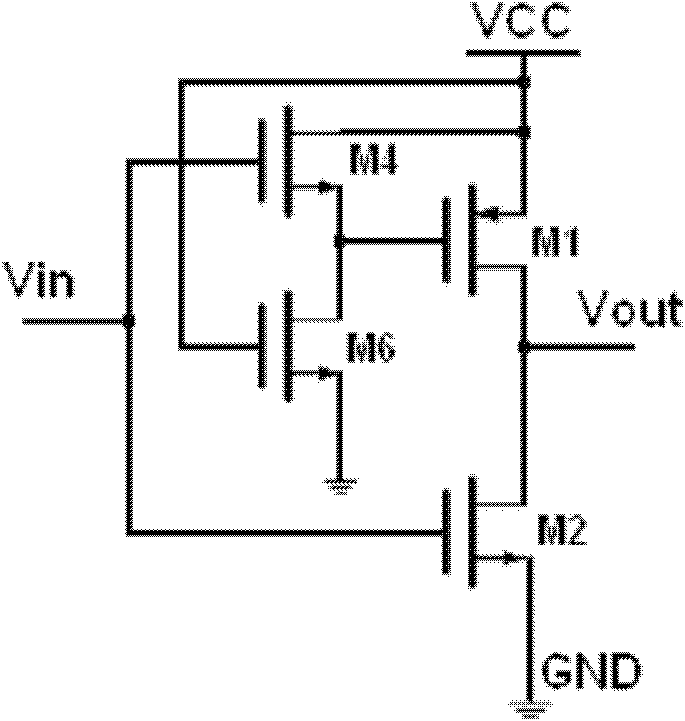

[0016] Such as Figure 1a For not using the common inverter circuit of the present invention, Figure 1b It is the embodiment circuit of the inverter of the present invention. exist Figure 1b In this embodiment, the input signal Vin is simultaneously connected to the gate of the second MOS transistor M2 and the gate of the fourth MOS transistor M4 of the source follower; the source output terminal of the fourth MOS transistor M4 is connected to the gate of the first MOS transistor M1 The gate of the sixth MOS transistor M6 is connected to VCC, the drain is connected to the source of the fourth MOS transistor M4, and the source is grounded, which is used as a current source load; the drains of the first MOS transistor M1 and the sec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com