Fuse structure and method for forming the same

A fuse structure and fuse technology, which are applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of complex process, occupying COMS area, and small fusing current, so as to achieve a simple forming process and save chips. Area, the effect of reducing the manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

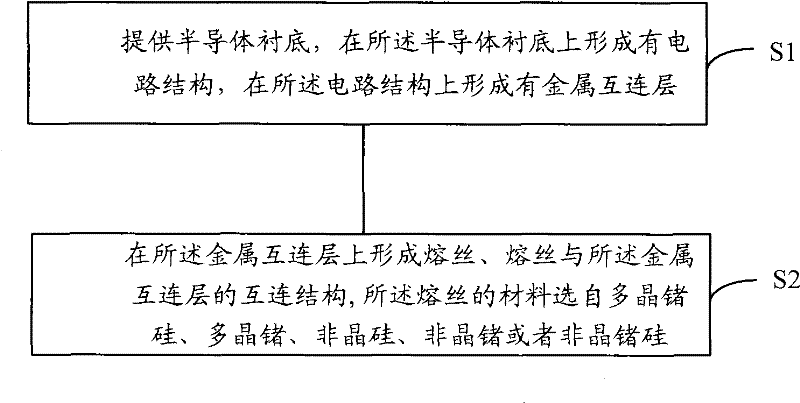

[0053] In the prior art, there is a fuse structure that uses polysilicon as a fuse. However, since the deposition temperature of polysilicon is above 600°C, it must be formed before the CMOS back-end process and is parallel to the CMOS circuit on the same plane. Therefore, the fuse structure It will occupy the area of the chip and increase the cost. The inventor has repeatedly studied, hoping to find a fuse structure that can be formed after the CMOS back-end process and stacked on the CMOS circuit without occupying the chip area.

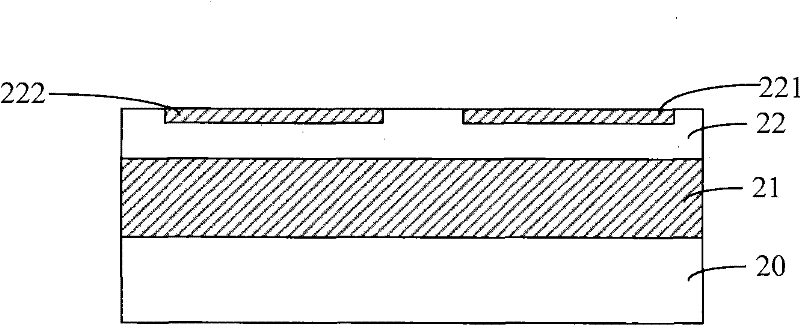

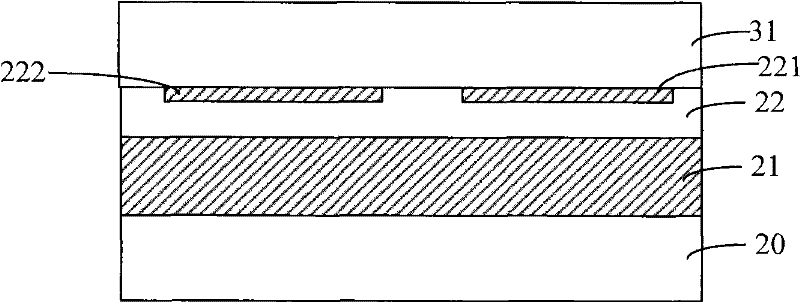

[0054] In the method for forming a fuse structure according to a specific embodiment of the present invention, after the circuit structure and the metal interconnection layer are formed, the interconnection structure of the fuse and the multi-fuse and the metal interconnection layer is formed on the metal interconnection layer.

[0055] In order to enable those skilled in the art to better understand the spirit of the present invention, the metho...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More