CMOS spacer structure and preparation method thereof

A side wall structure and isolation wall technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of underlying silicon substrate damage, device performance degradation, damage, etc., to eliminate loss and increase physical distance , Improve the effect of filling conditions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

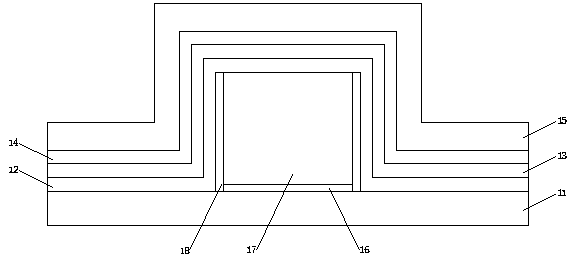

[0037] see Figure 3a As shown in -e, the present invention also provides a method for preparing a CMOS sidewall structure, the steps of which include:

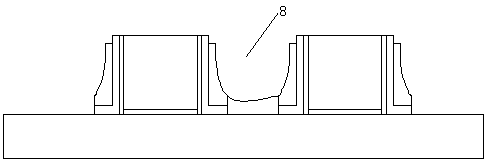

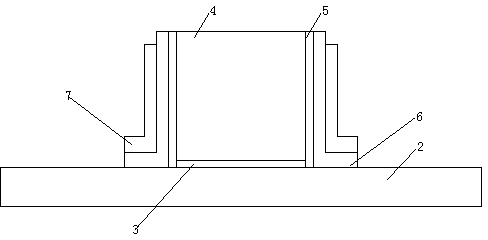

[0038] A first oxide layer 12, a first nitride layer 13, a second oxide layer 14 and a second nitride layer 15 are sequentially deposited on a silicon substrate 11 provided with a gate 17, wherein the side of the gate 17 A bias isolation wall 18 is arranged on the wall, and a dielectric layer 16 is arranged between the gate electrode 17 and the silicon substrate 11 .

[0039] Selective dry etching of the second nitride layer 15 to form a sidewall nitride layer 15 outside the second oxide layer 14 on the side of the gate 17 1 ; With the sidewall nitride layer 15 1 As a mask, wet etch the second oxide layer 14, etch away the second oxide layer at the top of the gate 17, and the sidewall nitride layer 15 1cover the other second oxide layer, and form an L-shaped outer oxide layer 14 outside the first nitride layer 13 on the si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More