8-value memory cell embedded in dram storage matrix, and corresponding conversion circuit thereof

A storage unit circuit and storage matrix technology, applied in information storage, static memory, digital storage information, etc., can solve the problems of limited range of control threshold, inability to realize the opening property of MOS transistor threshold interval, complex structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

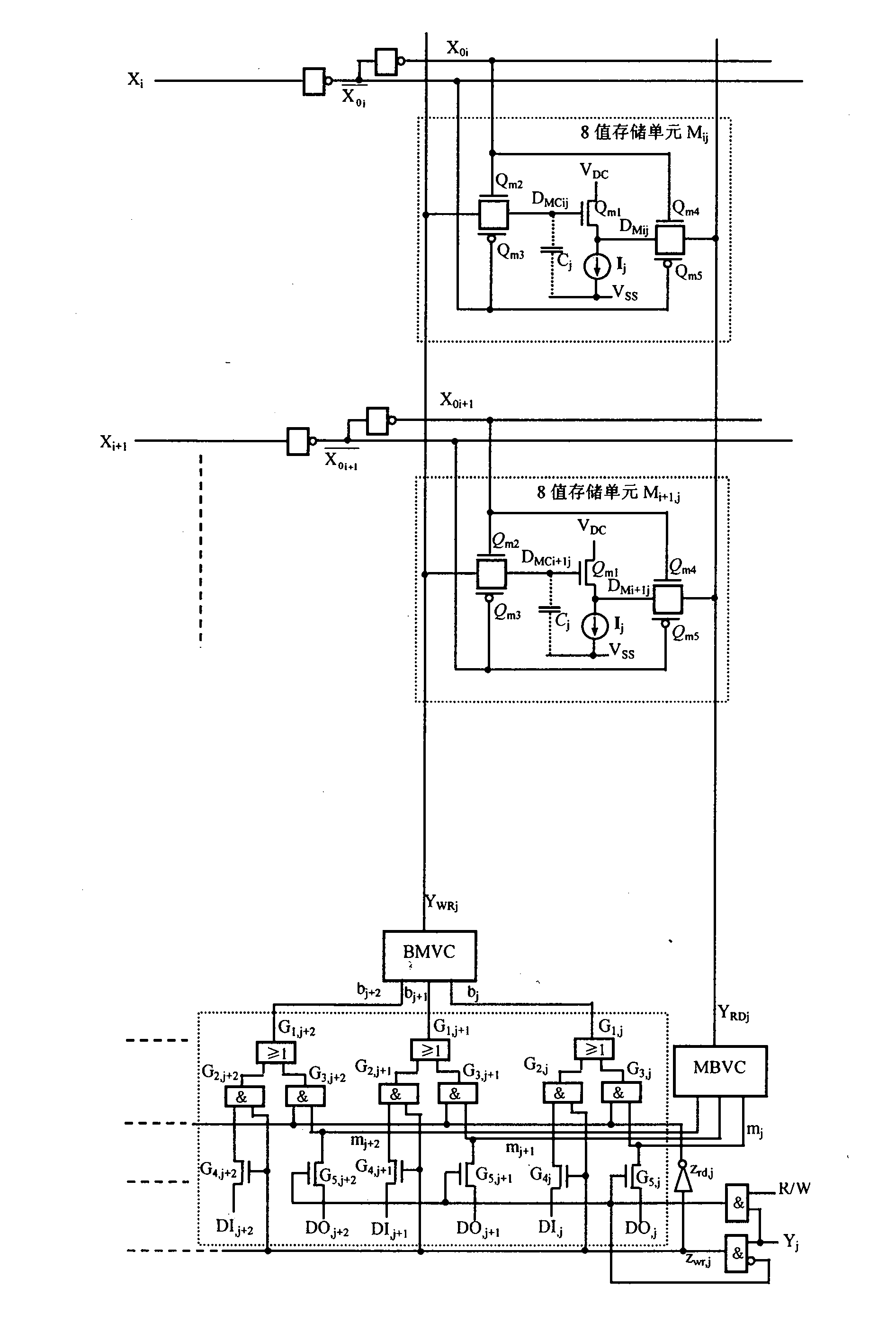

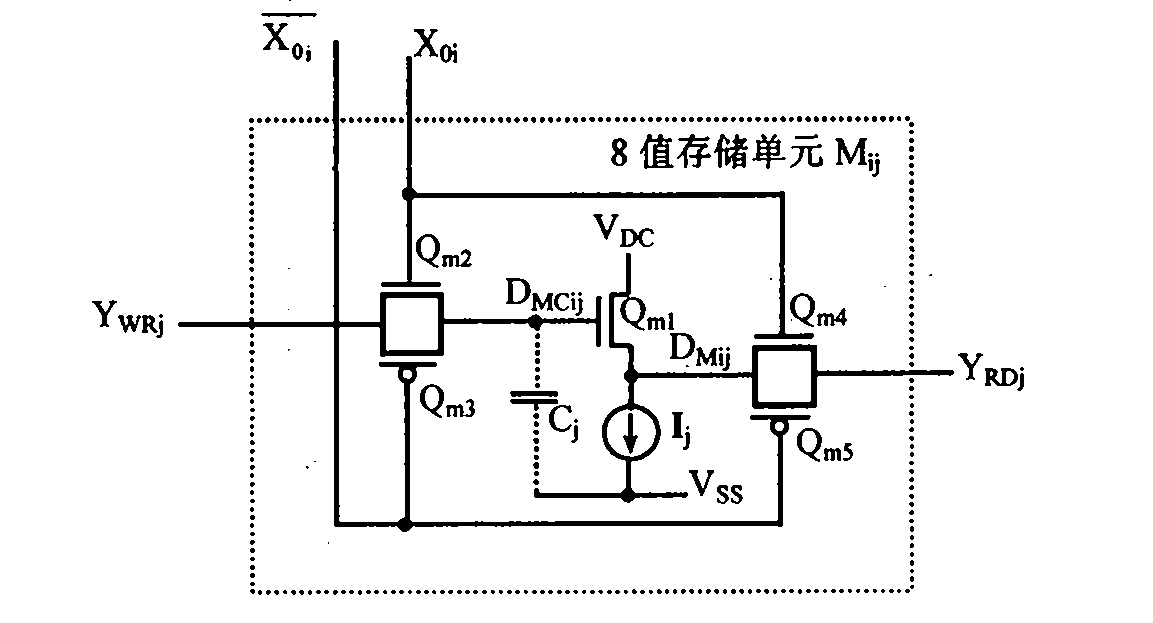

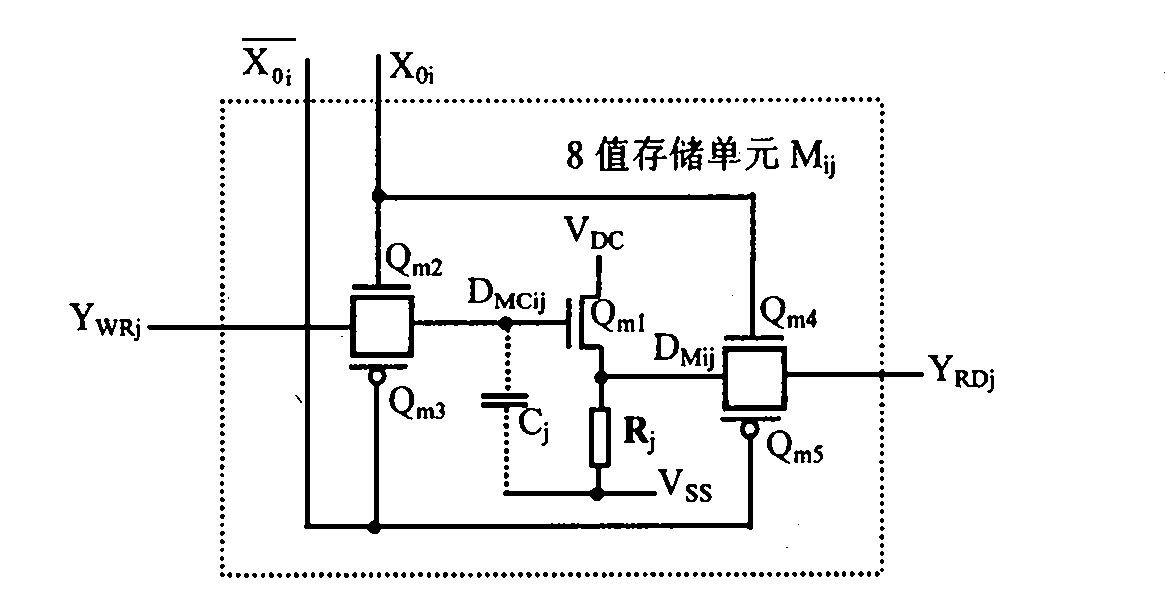

[0039] Embodiment 1: Description of the functions realized by the 2-8 value conversion circuit BMVC.

[0040] see Figure 4 ( Figure 1~5 Middle V DC =1.8V, V SS = -3.5V, V D =0V), gate f j7 ~ f j1 (There are two kinds of NAND gate and NOT gate) The working voltage is V DC , gate f j7 ~ f j1 Output high level near V DC , the output low level is close to 0V; ①When b j+2 b j+1 b j =111, f j7 = 0, f j7 Send low level to PMOS tube Q a7 gate, tube Q a7 conduction, V DC directly connected to Y WRj , Y WRj output voltage V YWRj =V DC (logic 7); ② when b j+2 b j+1 b j =110, f j7 = 1 and f j6 = 0, f j7 Send high level to tube Q a7 gate, tube Q a7 cut off, f j6 Send low level to tube Q a6 gate, tube Q a6 conduction, V DC connected to Y through a conduction diode WRj , V YWRj =V DC -V d (logic 6); ③ when b j+2 b j+1 b j =101, f j7 = f j6 = 1 and f j5 = 0, f j7 , f j6 Each sends a high level to the tube Q a7 , Q a6 gate, tube Q a7 , Q a6 cut...

Embodiment 2

[0041] Embodiment 2: Description of the functions realized by the 8-2 value conversion circuit MBVC.

[0042] see Figure 5 , consider the tube G B0mj ~G B3mj The gate of the gate is connected to the input Y through a band-pass-band-resistance variable threshold circuit RDj , tube G H4mj ~G H6mj The gate of the gate is connected to the input Y through the high-pass-low-pass variable threshold circuit RDj , where the tube G H4mj in Y RDj When the input is logic 4~7, it is turned on, and the tube G H5mj in Y RDj When the input is logic 6 and 7, it is turned on, and the tube G H6mj in Y RDj When the input is only logic 7, it is turned on, and the tube G B0mj in Y RDj When the input is only logic 2 and 3, it is turned on, and the tube G B1mj in Y RDj The input is only turned on when the logic level is 1, and the tube G B2mj in Y RDj The input is only turned on when the logic level is 3, and the tube G B3mj in Y RDj The input turns on only at logic level 5, also c...

Embodiment 3

[0043] Example 3: to Figure 3-5 Pspice computer simulation waveform Figures 10-14 instruction of.

[0044] Figure 10The circuit for embedding a 2-value DRAM memory matrix for an 8-value memory cell is in X i and Y j When high level, b j+2 , b j+1 , b j , Y WRj , Y RDj 、m j+2 、m j+1 、m j The waveform diagrams are separated up and down in sequence. It can be seen from the figure that when the input b of BMVC j+2 b j+1 b j =000~111 (the above 3 waveforms), BMVC output Y WRj It is an 8-valued signal 0~8 (the fourth waveform), and the 8-valued signal is obtained by the 8-valued storage unit Y RDj (5th waveform), Y RDj Input to MBVC, and finally MBVC outputs m j+2 m j+1 m j =000~111 (the following 3 waveforms), MBVC has 3-bit 2-value output m j+2 m j+1 m j waveform with BMVC's 3-bit 2-valued input b j+2 b j+1 b j The waveform is the same; Note: X i and Y j The high and low levels are each near V DC and 0; due to TG 1 and TG 2 It is to transmit 8-valu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More